S3C2410 DMA原理与实例

1. DMA的含义:Direct Memory Acess ,可以不通过CPU而在DMA控制器的控制下,高速地和I/O设备和存储器之间交换数据。

2.S3C2410A支持4通道DMA,在以下四种情况可运行

① 源设备和目标都在系统总线AHB上

② 源设备和目标都在外围总线APB上

③ 源设备在系统总线,而目标设备位于外围总线

④ 源设备在外围总线,而目标设备位于系统总线

3. 传输协议

① 单步模式:一次DMA传输有两个DMA应答周期(产生两个应答信号nXDACK)指示DMA读和写周期,主要用与测试和调试模式,在读写周期之前,总线控制权可以让给其他总线控制器

② 连续模式:一次DMA请求将产生连续的的DMA传输,直到规定的DMA传输数据传输完,在DMA传输周期间,nXDACK一直有效。DMA请求信号被释放。并且每次传输一个数据单元后,释放一次总线控制权,以让其他总线控制器有机会可以占有总线。

4. DMA操作

DMA使用三态FSM(有限状态机)进行操作,以下用三个步骤描述

State-1:初始状态,DMA等待DMA请求,若请求到达,进入状态2。此阶段,DMA AC和INT REQ 为0

State-2:DMA ACK 变为1,计数器CURR_TC的值从DCON[19:0 ]装载。DMA ACK保持1,直到它被清0

State-3:对DMA进行原子操作的sub-FSM(子状态机)进行初始化。sub-FSM 从源地址读取数据后将数据写入目标地址。对于这种操作方式,数据大小和传输大小应给予考虑。在整体服务方式中(whole service mode),这种操作重复直到计数器CURR_TC变为0,然而在单一模式中只进行一次。当子FSM完成每个原子操作,主FSM倒计CURR_TC。另外,当CURR_TC为0 和中断设置DCON[29]为1时,主FSM发出INT REQ(中断请求信号),同时清除DMA ACK 假如以下任一种情况发生

① 在整体服务模式(Whole service mode)CURR_TC变为0

② 在单一模式(Single service mode)原子操作完成

在单一模式,主FSM的三个状态进行后停止,等待另外的DMA REQ。如果DMA REQ到达,就重复三个状态。因此,DMA ACK被声明后进行每个原子操作。

相反,在整体服务模式(Whole service mode),主FSM在状态3等待直到CURR_TC变为0。所以DMA ACK 在传输区间被声明后进行原子操作当TC达到0时。

有可能有些朋友对“原子操作”有疑问,我没有找到标准的定义,按我的理解就是操作不可间断,一定要完成这个操作才能进行另外的操作。 相反,在整体服务模式(Whole service mode),主FSM在状态3等待直到CURR_TC变为0。所以DMA ACK 在传输区间被声明后进行原子操作当TC达到0时。

有可能有些朋友对“原子操作”有疑问,我没有找到标准的定义,按我的理解就是操作不可间断,一定要完成这个操作才能进行另外的操作。

5. 外DMA 请求/应答协议,有三种

① Single service Demand ② Single service Handshake ③Whole service Handshake

Demand 和 Handshake 模式的区别主要是XnXDREQ 和 XnXDACK时序,datasheet中有具体实例

6. 操作设置

① DMA通道初始化:rDISRC 、 rDISRCC 、 rDCON0 、 rDIDST 、 rDIDSTC 、 rDMASKTRIG0

② DMA中断初始化

③ 设置DMA请求源,如:Uart设置成DMA形式 rUCON0 = rUCON0 & 0xff3 | 0x8;

④ 设置DMA中断服务程序

实例:

//------------系统初始化---------------------------------------------------------------

2 ChangeClockDivider(1,1); // 1:2:4

3 //ChangeMPllValue(0x5C,0x04,0x00); // FCLK=200MHz

4 ChangeMPllValue(0x7d,0x1,0x1); // FCLK=266MHz MPLLCON

5 void AppDMAInit(void)

6 {

7 //rINTMOD |= (1<<17); ;//[17]INT_DMA0:0 = IRQ, 1 = FIQ

8 //pISR_DMA0=(int)Dma0Done;//DMA0的中断服务程序

9 pISR_DMA1=(int)Dma1Done;//DMA1的中断服务程序

10 //rDISRC0=TSRC_ADDR;

11 rDISRCC1=(0<<1)|(0<<0); // inc,AHB源来自于AHB

12 // rDIDST0=0x31100000;

13 rDIDST1=0x10000000;

14 rDIDSTC1=(0<<1)|(0<<0); // inc,AHB目的为AHB

15 rDCON1=(0<<31)|(1<<30)|(1<<29)|(1<<28)|(1<<27)|(1<<23)|(0<<22)|(1<<21)|(0<<20);

16 //|((rDCON0&fff00000)|0x80);//demand mode,whole service mode,burst mode

17 //31位1:Handshake mode 0: Demand mode is selected.

18 //30位0:Dreq与DACK与APB时钟同步 1AHB

19 //29位1:传送完成中断产生 0-CURR_TC interrupt is disabled

20 //28位 选择传送size of an atomic transfer 0: a unit transfer 1: a burst transfer of length four is performed.

21 //27位1:整个服务模式 0单个

22 //23位0:S/W请求模式被选,DMA加3倍通过设置DMASKTRIG寄存器的SW_TRIG位

23 //1:DMA源选择通过[26:24] triggers the DMA operation

24 //22位1:当前值为0时,DMA通道(MDA REQ)关断当传送计数.0:自动重载

25 //21:20位 00 = Byte 01 = Half word 10 = Word 11 = reserved

26 //[19:0]Initial transfer count (or transfer beat).

27 rDCON1= (rDCON1&0xf8f00000)|0x20 ;//1word*4(burst)*32=128word

28 //rDCON1 &=0xf8ffffff; //[26:24]=000 DCON1: 000:nXDREQ1 DCON0:000:nXDREQ0

29 rGPEDAT=(rGPEDAT&0xfff5)|0x5;

30 rGPECON=(rGPECON&0xffffff00)|0x00000055;

31 //赋首地址

32 src=(BYTE*)GRAPH_START_ADRR;

33

34 }

35

36 中断初始化

37

38 static void __irq Dma1Done(void) //DMA1中断(DMADONE)

39 {

40 //unsigned char i=100;

41 ClearPending(BIT_DMA1);

42 src =src+512;

43 rDISRC1 =(int) src;

44 //dma1done=0;

45 //Uart_Printf("dma is %x!\n",rDISRC1);

46

47 }

48

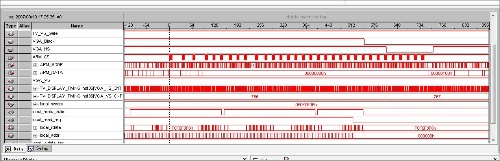

用FPGA采样DMA波形效果: