同步时序和异步时序电路、并行

同步时序电路

同步时序电路的组成规则:一个电路是同步时序电路,若它由相互连接的电路元件构成,则需要满足以下条件:

- 每一个电路元件是寄存器/组合电路

- 至少一个电路元件是寄存器

- 所有寄存器都接收同一个时钟信号

- 每个环路至少包含一个寄存器

最简单的同步时序电路

最简单的同步时序电路

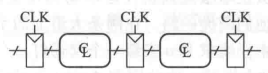

同步时序逻辑电路的流水线形式

同步时序逻辑电路的流水线形式

异步时序电路

非同步时序电路:异步电路

同步和异步电路

理论上,异步电路设计比同步电路设计更通用

因为:系统时序不受时钟控制的寄存器约束

类比→用任意电压的模拟电路比数字电路更通用;可使用各种反馈的异步电路比同步电路更通用

但,同步电路比异步电路更好设计;数字电路比模拟电路更容易。

实际上,几乎所有的系统本质上都是同步的。(两不同时钟的系统间通信、任意时刻接收输入,异步电路也重要)

总之,研究异步电路可能有利于改进同步电路

有限状态机

设计有限状态机的步骤:

1.确定输入输出

2.画状态图

3.对Moore型状态机:

①写状态转换表

②写输出表

4.对Mealy型状态机:

写出组合的状态转换表和输出表

5.选择状态编码(影响硬件设计)

6.为下一状态和输出逻辑写布尔表达式

7.画出电路草图

时序逻辑的时序

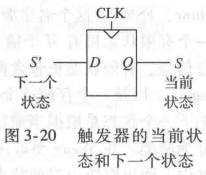

时钟沿对D采样sampling:触发器在时钟沿上升沿将输入D复制到输出Q

类比,照相机的孔径时间:在此时间内物体需要保持不动,照相机才能获得清晰的图像

时序元件在时钟沿附近也有“孔径时间”:在此时间内需要输入稳定,触发器才可以有明确定义的输出→时钟沿前的建立时间、时钟沿后的保持时间

动态约束:信号可以在有限时间里反复震荡,但在动态约束下,我们只关心时钟周期结束时的最终值,此后设置一个稳定值(真实世界无法满足)

用A[n]表示:第n个时钟周期结束时信号A的值,n是整数

不再考虑时刻t的值A(t), t是实数

足够长的时钟周期→使所有信号都稳定下来→限制系统速度

时钟偏移:真实系统中,时钟无法准确地同时到达所有触发器→增加必要的时钟周期

1 动态约束

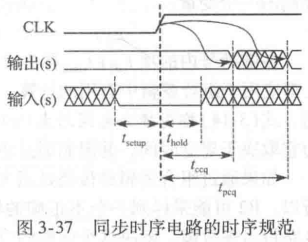

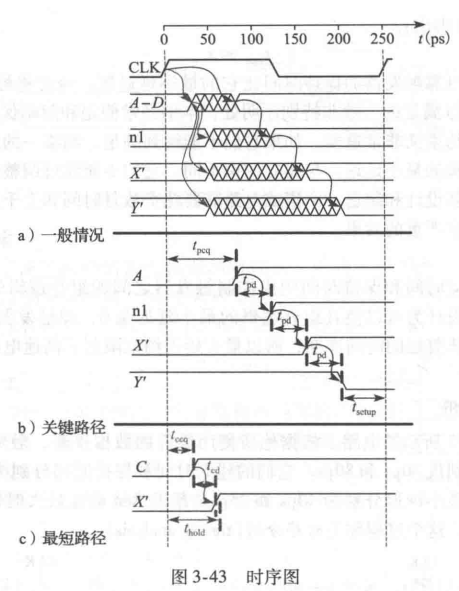

输出:时钟上升时,在时钟Q到最小延迟$t_{ccq}$后开始改变,在时钟到传播延迟$t_{pcq}$内达到最终值

输入:时钟上升沿到来前,在建立时间$t_{setup}$内保持稳定;时钟上升沿后,至少在保持时间$t_{hold}$内保持稳定

孔径时间=建立时间+保持时间(输入保持稳定状态的时间总和)

动态约束: 同步时序电路的输入,必须在时钟沿附近的建立和维持孔径时间内保持稳定

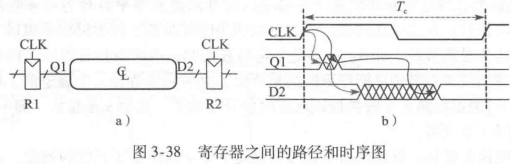

2 系统时序

时钟周期/时钟时间$T_c$:重复时钟信号的上升沿之间的时间

时钟频率$f_c=\frac{1}{T_c}$,时钟频率↑ 导致 数字系统在单位时间内完成的工作量↑

单位Hz(每秒周期数),换算关系:$1MHz=10^6Hz, 1GHz=10^9Hz$

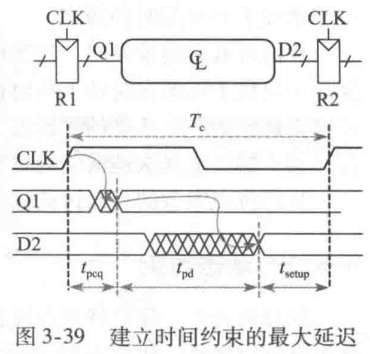

1、建立时间约束

最小时钟周期: $T_c \geq t_{pcq} + t_{pd} + t_{setup}$

制造商确定触发器时钟到Q的传播延迟$t_pcq$,建立时间$t_{setup}$

最大延迟约束/建立时间约束(设计师可以控制的): $t_{pd} \leq T_c - ( t_{pcq} + t_{setup} )$

$( t_{pcq} + t_{setup} )$时序开销,$t_{pd}$传播延迟

传播延迟过大→【D2可能在R2对其采样时不能稳定到其最终值】

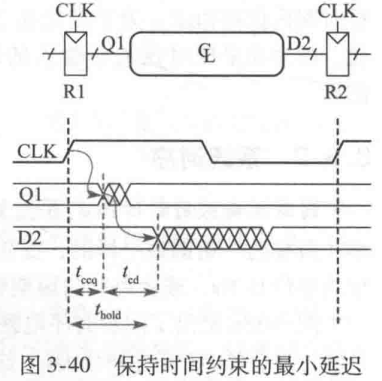

2、保持时间约束

下图:时钟上升沿后,只需$t_{ccq}+t_{cd} \geq t_{hold}$,D2发生变化($t_{ccq},t_{cd}$触发器属性)

组合逻辑的最小延迟约束/保持时间约束:$t_{cd} \geq t_{hold}-t_{ccq}$

若$t_{cd}=0$则$t_{hold} \leq t_{ccq}$ →【一个可靠的触发器的保持时间比它的最小延迟短】

保持约束时间不能通过调整时钟周期改正,千万别违反“保持时间约束”

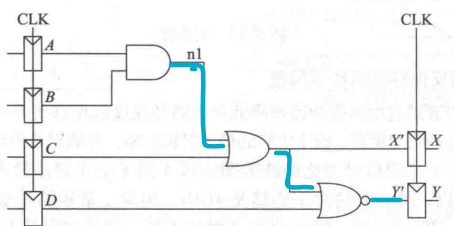

关键路径:时间最长的

最短路径

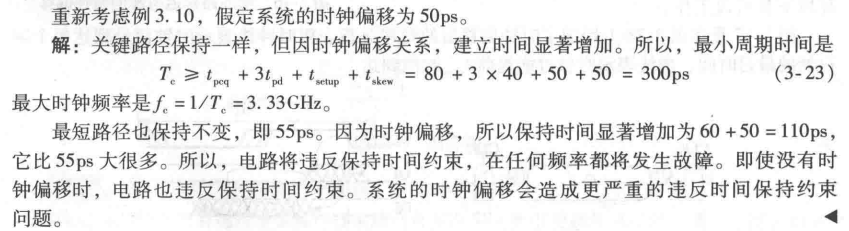

3 时钟偏移*

现实世界,每个寄存器到达时间有所不同,时钟沿到达时间的变化称为时钟偏移

4 亚稳态

输入时间在CLK之前的$t_{setup}$,CLK之后的$t_{hold}$时,破坏动态平衡,输出无法确定

亚稳态:触发器对孔径时间内发生变化的输入进行采样,输出Q随时可取$0~V_{DD}$之间电压

最后触发器确定输出到0或1的稳态,但到稳态的“分辨时间”无界,取决于球在最初位置上的平衡程度。

双稳态设备的两稳态间存在亚稳态。

5 同步器

真实世界的异步输入不可避免输入数字系统,没处理好就会产生亚稳态,所以要想办法尽可能降低出现亚稳态电压的概率。

为保证产生正确逻辑电平,一切异步输入都要经过同步器

系统可靠性的度量→平均失效间隔时间MTBF![]()

岁同步器延迟$T_c$指数增加

![]()

![]()

无封闭解(解析解,通过严格的公式所求得的解),故尝试带值

![]()

并行

系统速度度量/性能:延迟、通过系统的信息吞吐量

任务:经处理后能产生一组输出的一组输入

延迟:任务开始到结束需要的时间

吞吐量:系统单位时间内产生任务的数量

并行:同一时间内处理多个任务,可提高系统吞吐量

空间并行:多硬件,多任务同一时间一起处理

时间并行:一个任务分成多个阶段,分布到所有阶段

流水线:时间并行

并行的克星→依存关系(当前任务依赖于前一个任务的结果)

5.15