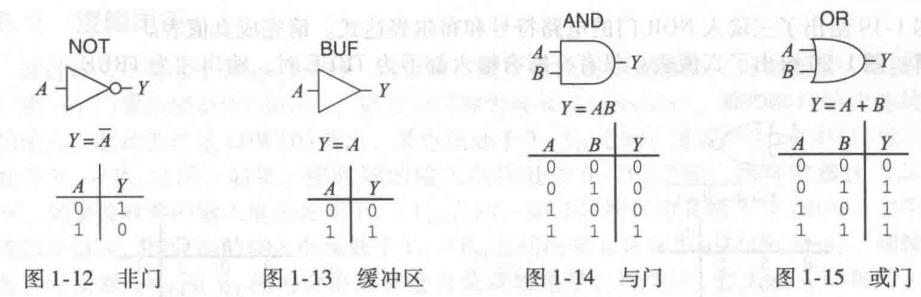

组合逻辑、逻辑门

抽象

像微处理器的大规模电路有很高的复杂性,可以用抽象和模块化原则将电路视为

一个明确定义了接口和功能的黑匣子

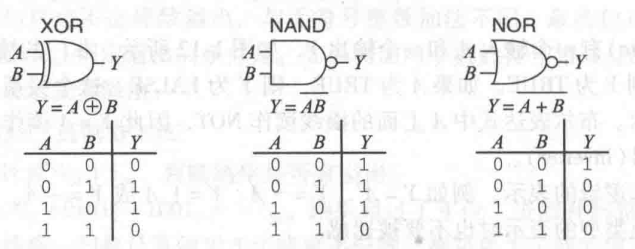

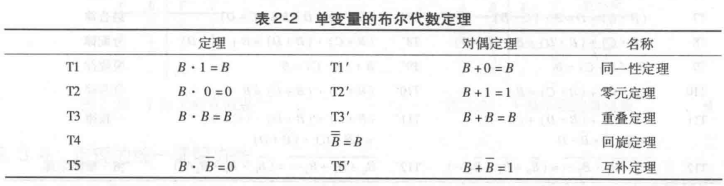

布尔代数

公理

单变量定理

逻辑门需要花费成本、功耗和延迟,所以用导线代替门电路是有益处的

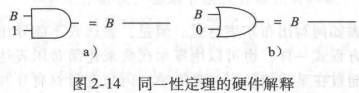

同一性定理

T1:2输入与门中,若有一个输入总为1,可以删除与门,用连接输入变量B的一条导线代替

T1':2输入或门中,若有一个输入总为0,可以删除或门,用连接输入变量B的一条导线代替

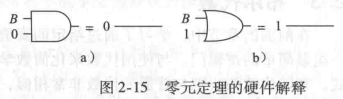

零元定理

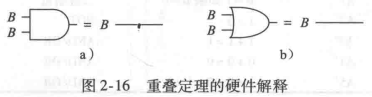

重叠定理

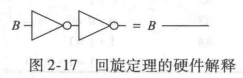

回旋定理

互补定理

多变量定理

逆变器/气泡(bubble)

想象“推”一个气泡通过门,使它从门的一边输入,从另一边输出可将与门替换成或门

规则:

- 从输出端向后推气泡 或 从输入端向前推气泡, 将原来的与门换成或门,原来的或门换成与门

- 输出端推气泡返回输入端,把气泡放在门的输入端

- 向前推所有门输入端的气泡,把气泡放在门输出端

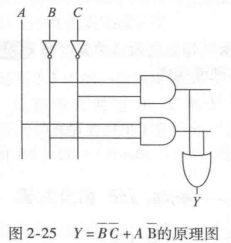

从逻辑到门

原理图应该遵循的准则

- 输入在原理图左边

- 输出在原理图右边

- 任何时候门都从左流向右

- 最好使用直线,不使用很多有拐角的线

- 线总在T型接头连接

- 两条线交叉的地方有一个点,表示其间有连接

- 没点没连接

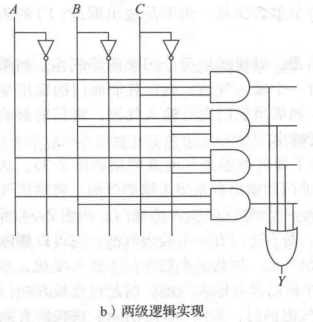

可编程逻辑阵列PLA

任何布尔表达式的与或式都可以用系统的方法画成和下图相似的原理图

按列画输入,有需要可用在相邻列间放逆变器提供输入信号的补

按行画每个最小项,用与门实现

对每一个输出,画或门连接和输出有关的最小项

1.上述图化简后电路速度可能更快(逻辑门输入更少)

2.用反相器进一步减少门数量

由德摩根定理,带反向输入的与门等效于一个或非门

基于不同实现技术,用更少的门或使用几种特定工艺的门更便宜

eg. CMOS实现中,与非门,或非门>与门,或门

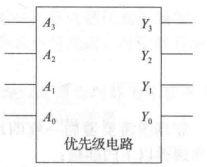

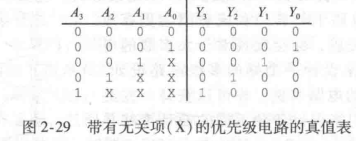

优先级电路

优先级为3>2>1>0

多级组合逻辑

“最好的”:门数量最少、速度最快、设计时间最短、花费最少、功耗最低……

注意!在某个工艺中最好的电路,在另一个工艺中并不是最好的。(类似于机器学习里的天下没有免费的午餐no-free-lunch定理)

积累设计经验,然后用观察法设计好的电路;充分利用计算机辅助设计CAD工具探索更多可能性

减少硬件

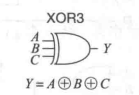

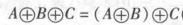

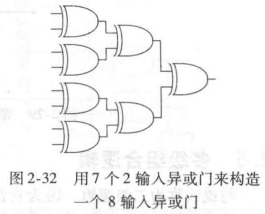

3输入异或门

![]()

两种实现(推荐第二种,减少了硬件)

类似的,8输入异或门实现方式①两级与或式逻辑:128个8位输入与门+1个128位输入或门②(better)2输入异或门树

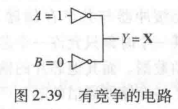

真实电路中的X和Z

非法值X

结点同时被0或1驱动

真实电压可能处于$0~V_{DD}$,取决于驱动高电平和低电平相对强度

危害:可能导致大电流在两竞争的门间流动,发热并损坏电路

X也可能是一个未初始化的值,方便报出警告

【注】

真值表里X表示0和1都可以

电路里则值电路结点有未知值或非法值

浮空值Z

浮空floating、高阻态high impedance、高Z态:结点未被高电平或低电平驱动

浮空结点:可能为0或1或01之间电压,与系统先前状态有关,不代表有错

只要浮空结点连接到有效电平就能正常工作

产生原因:未将电压接入输入端/假定无连接的输入端为0

三态缓冲器

①高电平有效

E使能,A输入,Y输出

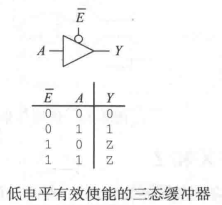

②低电平有效

用途:用在连接多个芯片的总线上

过去普遍

一个时刻仅允许一个芯片的使能信号向总线驱动数据,其他芯片输出浮空,防止竞争

任何时刻均可以通过共享总线读取信息

现在需要加快速度,所以就用“点到点链路”了

浙公网安备 33010602011771号

浙公网安备 33010602011771号