可编程逻辑器件和数字系统设计初步

可编程逻辑器件

传统通用逻辑器件:逻辑规模小、占用印刷板面积大、功耗大、可靠性低

专用集成电路ASIC(Application Specific Integrated Circuit),针对特定用途

可编程逻辑器件PLD(Programmable Logic Device),属于ASIC:可由设计者自己完成逻辑功能,系统集成度高、可靠性高、设计过程灵活、可用软件仿真

现代数字系统设计过程的变换:“通用器件+印刷版+焊接调试”→“可编程逻辑器件+计算机+仿真软件”

PLD结构:①基于乘积项Product-Term②基于查找表Look-Up-Table

基于乘积项的PLD

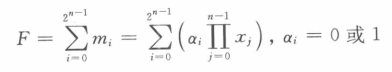

任何组合逻辑函数可被表达成最小项之和的形式

用可编程“与-或”阵列实现逻辑$f=ABC+A\hat{C}D+B\hat{D}$

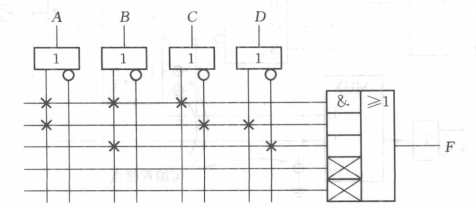

基于查找表的PLD

以一个二维的逻辑块阵列构成PLD器件的逻辑核心,可编程的连线分布在逻辑块和逻辑块、逻辑块和输入输出块之间。逻辑块内部以查找表方式实现逻辑功能。

采用此结构的PLD芯片称为FPGA(Field Programmable Gate Array)现场可编程门阵列

查找表本质:随机读写存储器

1位随机读写存储器(RAM):可以在任何时候被写入一个逻辑值0或1(随机写入),可以在任何时候将此逻辑值读出(随机读出)。本质:1位数据锁存器

多个RAM构成一个RAM阵列,为选择写入和读出的RAM,常采用类似数据选择器的结构,给每个RAM赋予一个地址。通过地址的选择,可对指定RAM读写。

浙公网安备 33010602011771号

浙公网安备 33010602011771号