常用同步时序电路(同步计数器、时钟发生电路、通用移位寄存器)

1 同步计数器

实际集成电路同步计数器有辅助功能:同步置数、同步或异步复位、超前进位

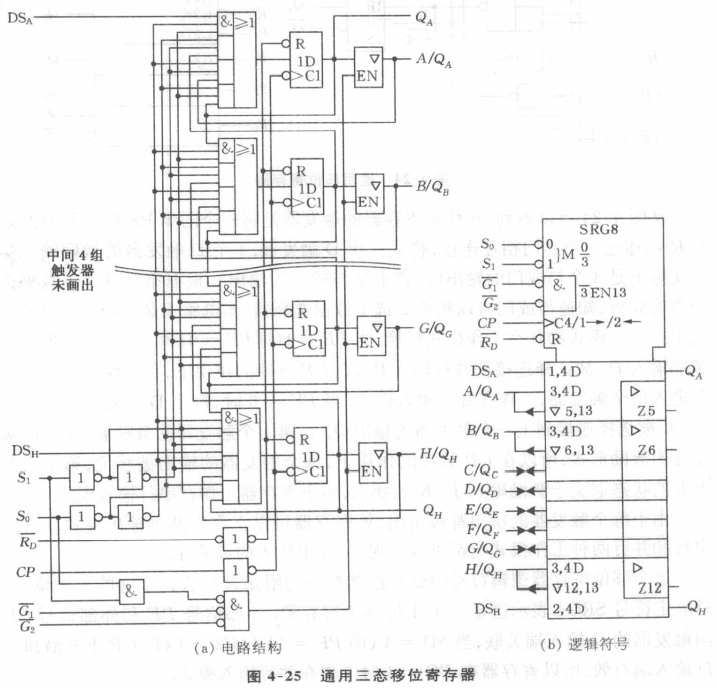

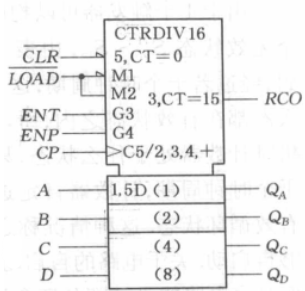

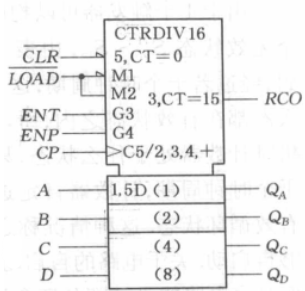

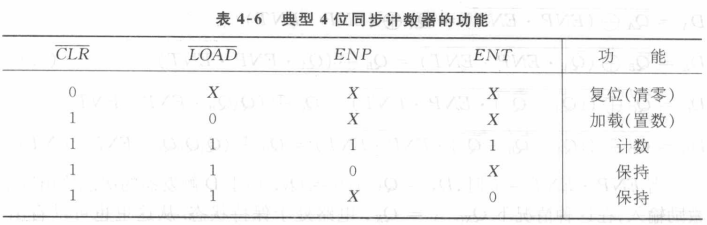

【典型4位二进制同步计数器】

4个输出$Q_A$~$Q_D$

4个并行输入A、B、C、D

4个控制端$\overline{CLR},\overline{LOAD},ENP,ENT$

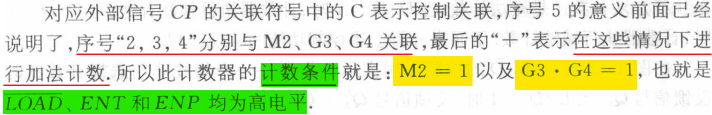

功能如下

$\overline{CLR}$同步清零端:$\overline{CLR}=0$,在CP作用下,$Q_A$~$Q_D$被清零

$\overline{LOAD}$同步置数端:$\overline{LOAD}=0$,在CP作用下,$Q_A$~$Q_D$被置为A、B、C、D的值

$ENP,ENT$计数允许:

$ENP=1,ENT=1$,允许计数

其他情况保持原有计数值不变

$ENT$还有进位输入作用

每个触发器激励输入D:连接一个与或门输出(其输入来自控制端$\overline{CLR},\overline{LOAD}$+一组异或门输出$D_X,X=A、B、C、D$)

实际上是数据选择器,选择端$\overline{CLR},\overline{LOAD}$

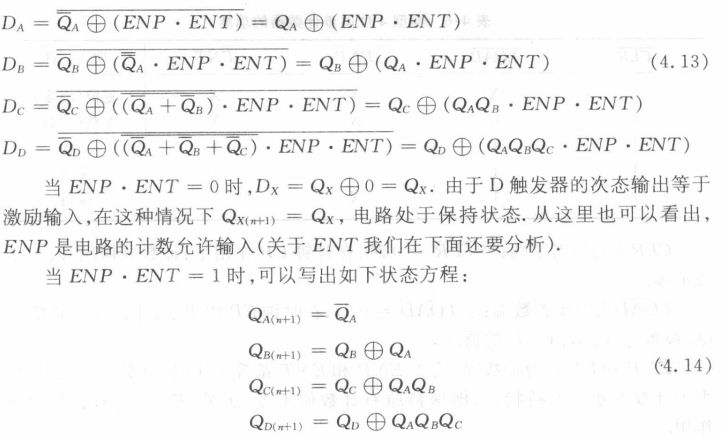

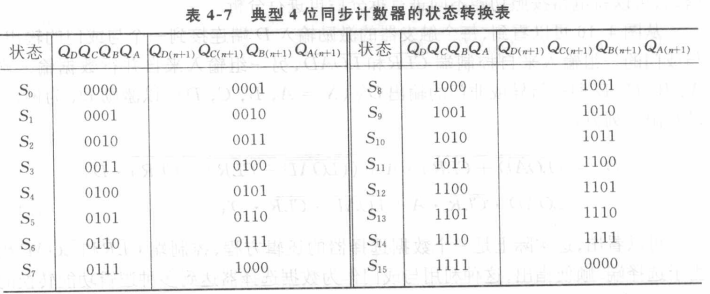

【二进制加法计数器】

$Q_A:LSB(the least significant bit),Q_D:MSB(the Most Significant Byte)$

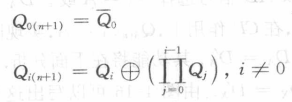

每位输出次态=本位现态输出$\oplus $低于本位所有现态输出的逻辑与

$RCO$:增加位数(在异或函数第二项增加低位输出的逻辑与)

![]()

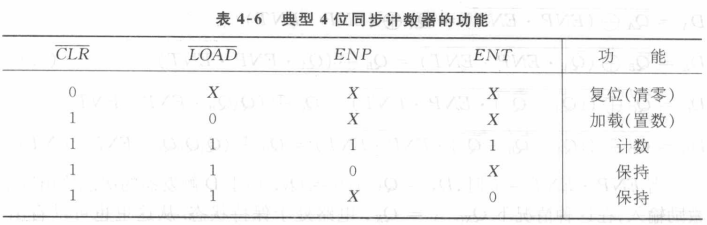

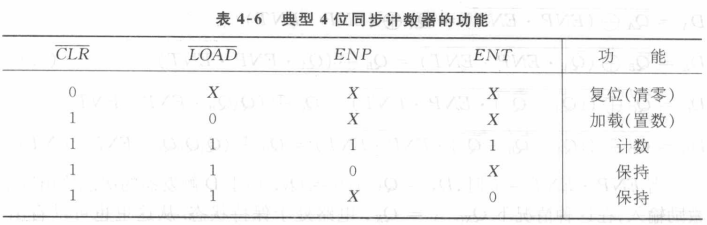

【4位同步计数器逻辑符号中“公共控制框内限定符号”】

![]()

![]()

总限定符号$CTRDRV16$:循环长16(4位二进制)的计数器

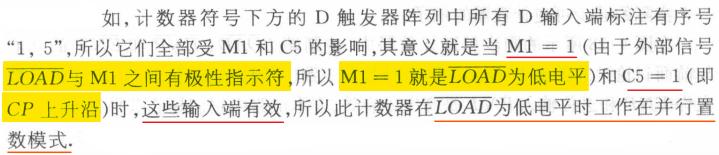

对应外部信号$\overline{LOAD}$标注的M:关联符号,Mode方式关联

$M1,M2$:$\overline{LOAD}$信号在高、低电平下,内部关联的对象不同

对应外部信号$CP,ENT,ENP$标注的C,G:关联符号,Control控制关联,G与(AND)关联

关联符号:图形符号中所有标注同样标志序号输入输入输出都受其影响

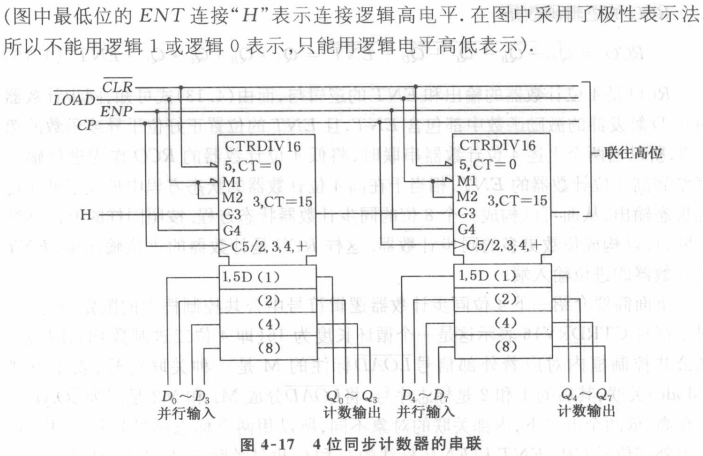

【多个同步计数器串联成更多位数的同步计数器】

最低位计数器$ENT=1$:保证最低位计数器可正常计数

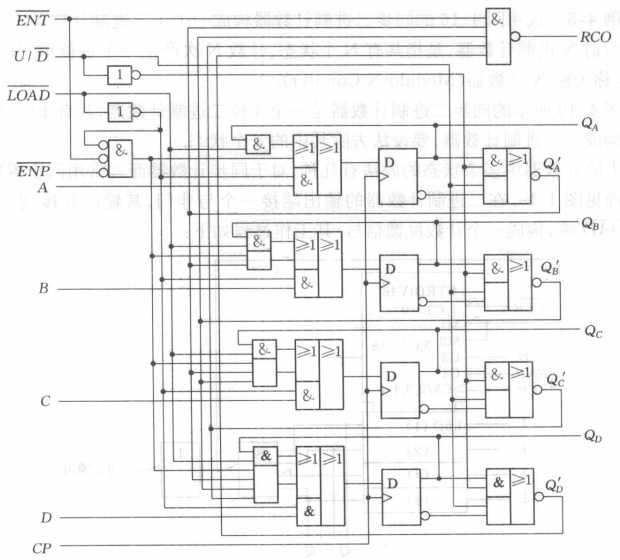

【同步可逆计数器】在外部控制下,可加法计数也可减法计数

$ENP,ENT$低电平有效

方向控制端$U/\overline{D}$(通过与或非门选择计数器反馈信号$Q_x'$):

控制加法计数($U/\overline{D}=1$时选$Q_x'=Q_x$)或减法计数($U/\overline{D}=0$时选$Q_x'=\overline{Q_x}$)

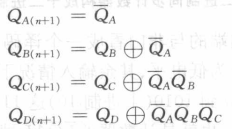

减法计数器$\overline{LOAD}=1,\overline{ENP}=0,\overline{ENT}=0,U/\overline{D}=0$状态方程

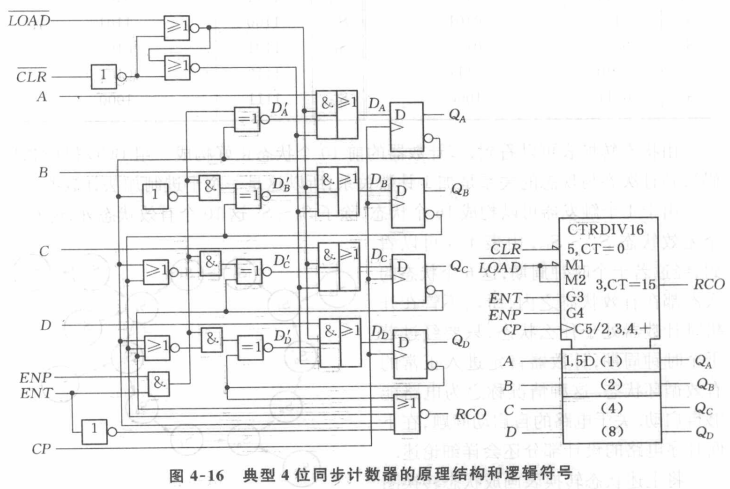

【构成任意进制的计数器】

N进制计数器/模N计数器:共有N个状态,计数N此产生一个进位信号

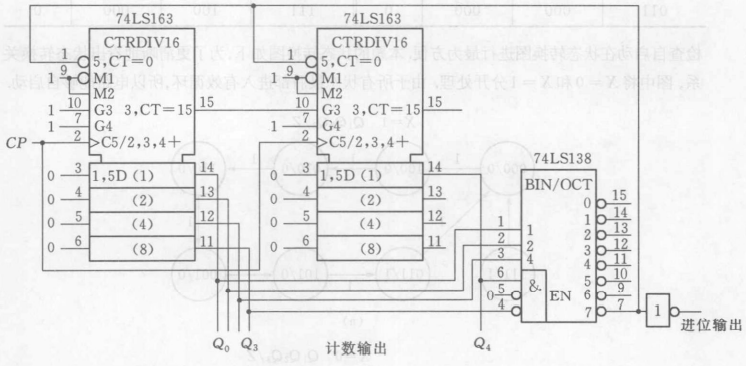

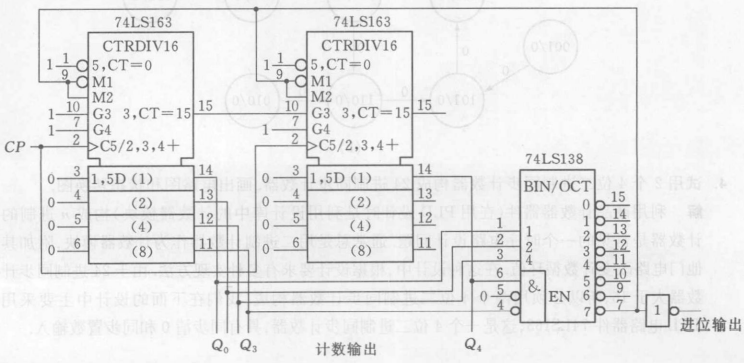

![]()

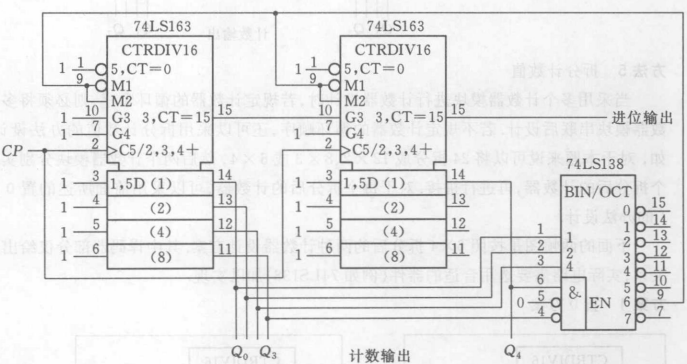

24>16所以用2个4位二进制同步计数器,采用TTL电路器件74LS163,有同步清0、同步置数输入

【法1】同步清0

74LS138的输入是23(10111)上面是低位,下面是高位

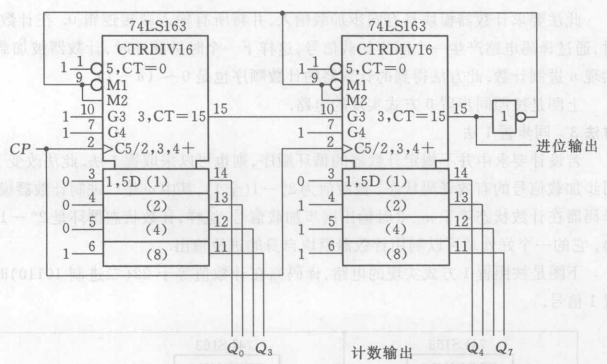

【法2】同步置0

与前面的区别在,进位输入的非接在M1和M2(LOAD端),上面接在5,CT=0(CLR端)了

——————————————————————————————————————

——————————————————————————————————————

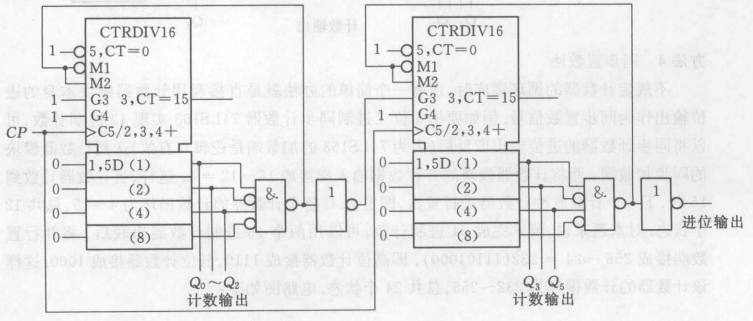

【法3】 同步置1

译码器在计数值等于22(二进制10110)时产生同步置1信号

【法4】同步置数

256-24=232(11101000),高位1110,低位1000,计数循环位232~255

【法5】拆分计数

a.置0方案

b.置1方案

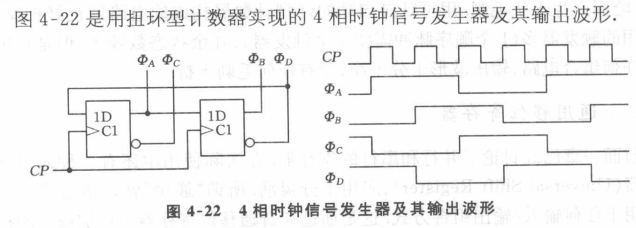

2 时钟发生电路

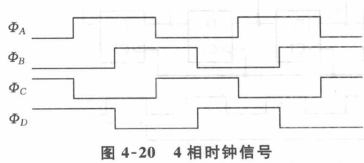

时钟信号的移相、分频

几个时钟信号相差固定相位

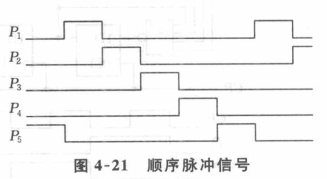

顺序脉冲:系统控制信号部分按时间先后产生一系列脉冲信号,这些信号在时间上严格按照时间顺序排列

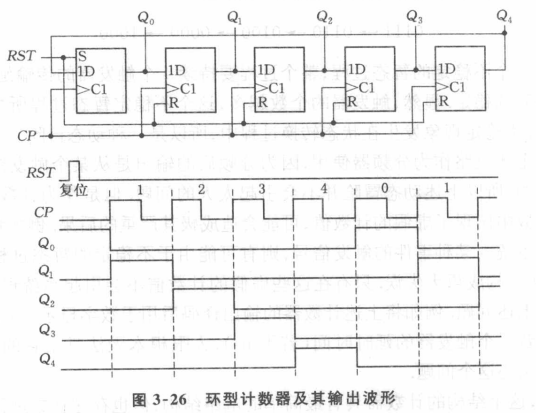

每两个相邻信号间有一定延时(可用每两个触发器状态相差1个时钟周期的环型计数器或扭环型计数器构成)

单活跃电路:任何时刻只有一个输出逻辑1

上面和下面基本环型计数器的不同:反馈到第1个触发器激励端的信号

上面的“可自启动的环型计数器”:将第1个到第4个触发器输出经过1个或非门组合后反馈到第1个触发器激励端

(保证任何状态下,只要经过有限个时钟脉冲,总可用进入单活跃状态);

与用计数器和译码器组合成的顺序脉冲信号发生器

(1个顺序脉冲要1个触发器,冗余状态少,构成脉冲多时比较经济)相比,冗余态多,故无毛刺干扰。

下面的“基本环型计数器”:

将最后一个触发器输出反馈至第1个触发器激励端(不能保证电路进入只有一个输出是逻辑1的正确循环)

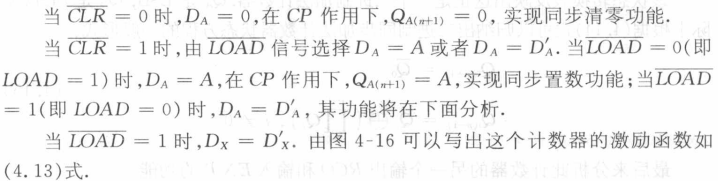

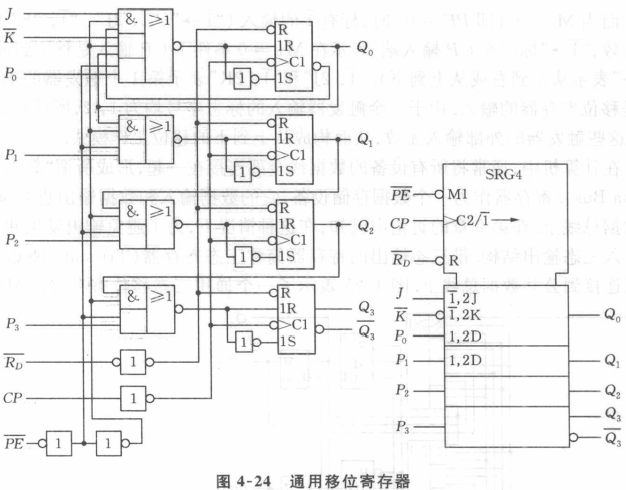

3 通用移位寄存器

通用:寄存器可用用于任何输入/输出方式

通过在普通移位寄存器上加额外的控制逻辑电路实现。

---------------------------------------

2个串行输入端$J、K$

4个并行输入端$P_0$~$P_3$

4个数据输出端$Q_0$~$Q_3$

控制信号$PE$:选择工作在串行输入或并行输入模式

异步信号清零输入$R_D$:时钟正边沿触发

将同步RS触发器S端和R端通过非门连接构成D触发器

三台寄存器:带三态输出的寄存器