JTAG 接口

JTAG 接口

简短介绍

JTAG 为 Joint Test Action Group 的缩写,是在生产后用来校验、测试印刷电路板的一种标准。

JTAG 作为数字仿真工具的一种补充,被电子设计自动化 (EDA) 使用的一种标准。它规定了一个串行通信接口作为调试端口,不需要外部访问系统地址、数据总线,直接实现内部访问。这个接口连接到片上 Test Access Port (TAP),这个 TAP 具有状态协议来访问一系列测试寄存器,这些寄存器能够呈现芯片逻辑电平以及期间功能。

标准: IEEE 1149.1-1990, entitled Standard Test Access Port and Boundary-Scan Architecture

JTAG 标准被一些半导体芯片厂商进行了扩展。

接口应用

调试

虽然 JTAG 早期应用目标是进行板级测试,随着时间发展,现在 JTAG 标准设计来辅助器件、电路板或系统的测试、诊断以及故障隔离。现今,JTAG 是进行集成电路子模块访问的主要手段,这一特性让它称为调试嵌入式系统的基本机制。在大部分系统上,基于 JTAG 的调试在 CPU 重置之后即可使用,帮助开发早期的启动引导软件 (软件一般在最开始阶段进行工作)。一个 JTAG 适配器使用 JTAG 接口来访问 CPU 内部的片上调试模块。这些模块让软件开发者直接以机器指令级调试嵌入式系统软件。

有时候 FPGA 开发者也会使用 JTAG 来开发调试工具。使用与 CPU 相同的机制来帮助调试 FPGA 数字设计模块。

固件存储

JTAG 允许传输数据到内部非易失存储器件上。JTAG 可以用来写软件与数据到闪存上。这通常是使用访问 CPU 时使用的相同的数据总线实现的,且有时是通过 CPU 处理的。有时候存储芯片自身具备 JTAG 接口。

边界扫描测试

JTAG 边界扫描技术提供访问复杂集成电路的逻辑信号的方法 (比如器件引脚)。这些信号呈现在边界扫描寄存器中 (BSR),通过 TAP 可以进行访问。这允许测试、控制信号状态用来测试、调试。因此,软件与硬件故障可以通过这一方法进行定位。

当结合内建自测 (BIST),JTAG 扫描链使能了低功耗,嵌入式方案来测试一个 IC 的某一个特定的静态故障。

测试案例通常以标准格式给出 (比如 SVF,或其二进制 XSVF)。

电气特性

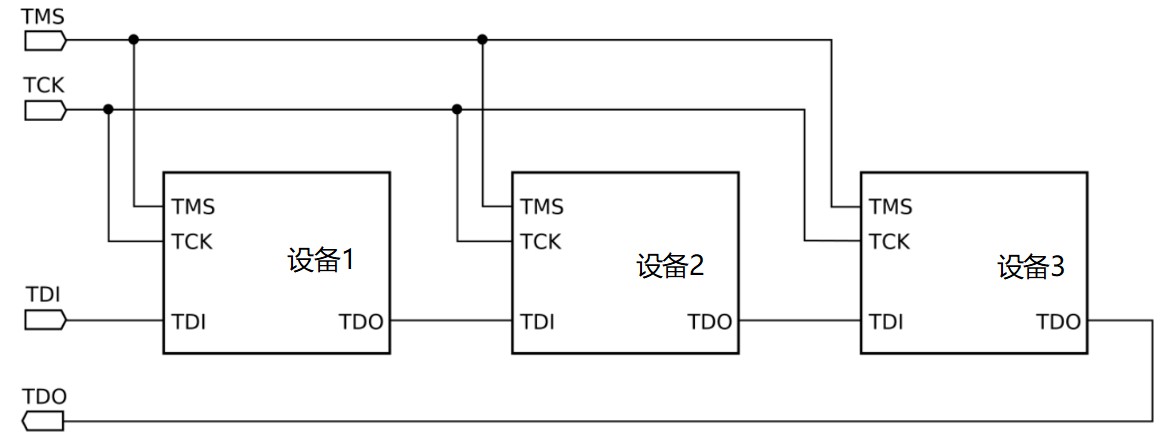

一个 JTAG 接口,按其版本,可以有两个、四个或五个引脚的形式。四、五引脚的接口设计,可以令电路板上多个芯片以菊花链的形式进行连接。双引脚接口可以使多个芯片以星形拓扑进行连接。在任何情况下,测试探针只需要连接到一个 JTAG 端口上,就可以访问电路板上所有的芯片。后面只介绍四、五个引脚的情况。

链接器引脚为:

TDI,测试数据输入引脚TDO,测试数据输出引脚TCK,测试时钟引脚TMS,测试模式选择引脚TRST,测试重置引脚 (可选)

TRST 引脚是一个可选引脚 (低电平有效复位)。如果没有这个引脚,也没有关系,通过 TCK 与 TMS 配合也能够实现状态机重置。

因为只有一个数据引脚,因此协议是串行的。时钟输入为 TCK 引脚。每一个 TCK 上升沿一个数据比特从 TDI 输入,一个数据比特从 TDO 输出。可以载入不同的指令。对于某个 IC,指令可以读取芯片 ID,采样输入引脚、驱动输出引脚,操作芯片功能,或旁路 (将 TDI 连到 TDO)。

TCK 的最大工作频率取决于链上允许的最低频率,通常是 10~100 MHz。当然 TCK 频率也依赖于板卡布局以及 JTAG 适配器的能力与状态。

时钟与 TMS 的配合,会更改 JTAG 标准状态机的状态。JTAG 状态机可以复位、访问指令寄存器或访问指令寄存器选择的数据。

浙公网安备 33010602011771号

浙公网安备 33010602011771号