高通DSP优化 - 纯汇编优化 - 查表指令

在DSP汇编优化过程中,查表指令是一个极其重要的指令,也是需要开发者重点掌握的指令。

大多数平台,查表指令是比较容易理解的:“提供一个vector的表,再提供一个vector的索引,生成一个vector的结果”。但这不包括高通平台(⊙﹏⊙)。

本文主要讲解一下高通平台的查表指令。

先看一下高通对于此指令的说明:

高通有几种查表模式,此处介绍最常用的一种:

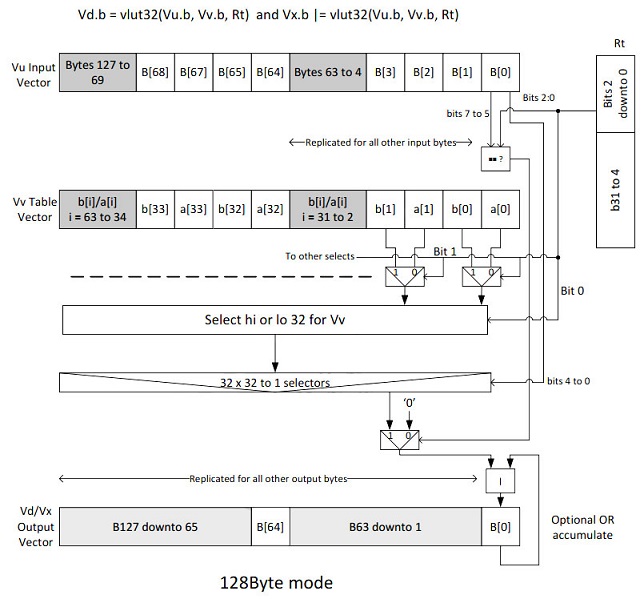

Vd.b=vlut32(Vu.b,Vv.b,Rt) 和 Vx.b|=vlut32(Vu.b,Vv.b,Rt))

这两条指令常组合使用。

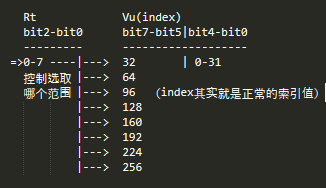

从图中可以看到,Rt中有效位置为bit2-bit0,即数字0-7,会和index vector(Vu)的bit7-bit5相比较,控制index vector中索引值在第几个32的范围内查表(最大查表范围8x32=256)。例如Rt=1,则index值在32-63范围时,才会从table vector(Vv)中取值。同时呢,index的值如果在32-63范围内,则它的第5位正好是1,和上边的介绍正好是对应的。

如下图:

因此根据你查表的index值的范围,常常会有n条指令组合起来使用。如下,查找0-127范围时,代码如下:

Load index vector to V0;

Load table vector to V1; // total 128 element

V2.b =vlut32(V0.b,V1.b,0);

V2.b|=vlut32(V0.b,V1.b,1);

V2.b|=vlut32(V0.b,V1.b,2);

V2.b|=vlut32(V0.b,V1.b,3);

Store the result V2;

到此,你已经了解了这个指令的一半了,还有一件重要的事情是:

从图中还可以看到Rt的最低位(即Vu的bit5)同时控制着从table vector中的奇数或者偶数位置取数据。 因此我们常需要对table vector(Vv)做64bytes的shuffle操作。从而让table vector的顺序按照如下排列:

127, 63,126, 62,........68, 4, 67, 3, 66, 2, 65, 1, 64, 0

Rt=0,1,2,3 same ordering for bytes 128-255 Rt=4,5,6,7

到此,所有该注意的事项已经说明了。我们看一个实际的例子。

// c code

uint8_t table[256] = {0, 1, ...};

uint8_t src = 0xXXXXXXXX;

uint8_t dst = 0xXXXXXXXX;

for (int i = 0; i < lengh; i++)

{

dst[i] = table[src[i]];

}

// hexagon pseudo asm code

load table to V0 and V1; // 128 elements per vector.

V0.b = vshuff(V0.b); // 对Vv做64bytes的shuffle操作

V1.b = vshuff(V1.b);

for (i -> length)

{

load src(index) to V2;

V3.b =vlut32(V1.b,V0.b,0);

V3.b|=vlut32(V1.b,V0.b,1);

V3.b|=vlut32(V1.b,V0.b,2);

V3.b|=vlut32(V1.b,V0.b,3);

V3.b|=vlut32(V2.b,V0.b,4);

V3.b|=vlut32(V2.b,V0.b,5);

V3.b|=vlut32(V2.b,V0.b,6);

V3.b|=vlut32(V2.b,V0.b,7);

store result(V3) to dst;

}

另外,如果表只有128Bytes,则vlut32查表指令只需要4句(上述例子中为256的表,故vlut32共8句)。

至此,END.HAHA