高通DSP优化 - 纯汇编优化 - 条件指令

在dsp中,常常有一类特殊的寄存器,其有着特殊的功能。如果对这些寄存器有一些了解,那么对你的代码设计(汇编开发),有着很大的帮助。对代码质量、代码效率都有较大的益处。

今天,我们主要简单了解一下高通的条件寄存器P和Q,称之为“谓词寄存器”。

- 首先,了解一下条件寄存器和普通寄存器的联系。(以下内容有些是我自己的看法,如果不对,请及时指正)

P寄存器和Q寄存器分别主要针对标量指令和向量指令,它们的位数和寄存器的宽度有关,一般通用寄存器的一个byte对应谓词寄存器的一个bit。

例如,高通平台通用标量寄存器是32-bits(4bytes),但由于其可组成一个64-bits(8bytes)的寄存器对来处理宽度为8bytes的指令,因此每一个P寄存器的宽度为8-bits,共用4个P寄存器P3:0。

同理的,向量寄存器的宽度为128bytes,指令可支持128bytes的处理,故对应的Q寄存器的宽度为128-bits,共有4个Q寄存器Q3:0。

- 其次,了解一下条件寄存器重要的用法

条件寄存器,在数据的地址不对齐、长度不对齐时的,加载存储方面有重要的用途,特别是存储。

高通DSP的条件加载LOAD

只有对齐加载(vmem),没有非对齐加载(vmemu);且只支持P寄存器条件,即要么加载128bytes,要么加载0byte。

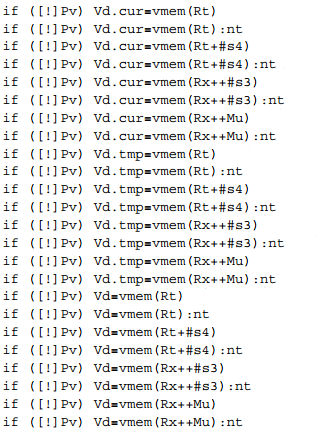

指令如下:

高通DSP的条件存储STORE

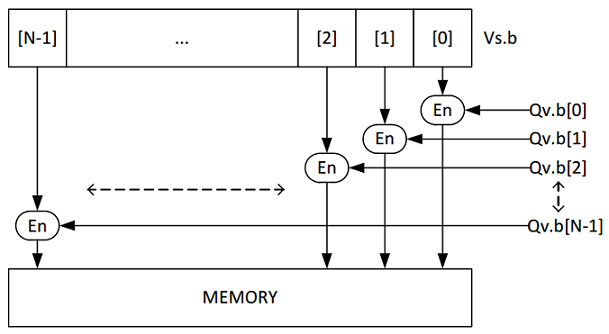

与加载相比,条件存储指令更加丰富,对齐存储(vmem)时,既支持P条件,也支持Q条件;非对齐存储(vmemu)只支持P条件。重点说一下,Q条件的对齐存储指令,它意味着Q寄存器的每一个bit分别控制着Vector寄存器中的每一个byte的存储与否,也就是说,我们可以更加灵活的选择一个向量中的每一个byte存储。

指令如下:(红色框为Q条件的对齐存储,蓝色框为P条件的非对齐存储)

If (Qv4) vmem(Rt) = Vs指令示意图

-

再次,条件寄存器如何赋值

最基础的,通过比较指令。比较指令都会更新条件寄存器中的值。

有些平台,一般的算术指令,如加减乘除等也会更新条件寄存器,如movidius平台。高通平台目前应该并不能通过普通的算术指令更新条件寄存器。 -

扩展

一般的,绝大多数DSP都会有条件指令,且有条件存取指令,掌握这些指令,对代码设计有较大好处。在了解平台的时候,可以关注一下这方面的东西。

浙公网安备 33010602011771号

浙公网安备 33010602011771号