DSP28377s系统时钟配置注意事项

DSP28377s系统时钟配置注意事项

问题一脸嫣然的向我们走来。。。

近日,一个兄弟在配置基于28377s芯片的主控系统时钟时,遇到点困难。

具体是这样的,原来的主控板使用的是20MHz外部晶振,为取200MHz系统时钟,倍频设为20,分频设为2,这样sysclock = 20MHz * 20 / 2,正好200MHz。具体调用TI公司的库函数,实现代码是这样的:

InitSysPll(XTAL_OSC,IMULT_20,FMULT_0,PLLCLK_BY_2);

但新的控制板上面使用了30MHz外部晶振,为配置200MHz系统时钟,此兄弟将倍频设为40,分频设为6,代码如下:

InitSysPll(XTAL_OSC,IMULT_40,FMULT_0,PLLCLK_BY_6);

计算下来,系统时钟也应该是200MHz,不过,按此配置后,程序运行就卡死在定时器1、2溢出while循环里了。

为什么呢?

这个算术应该是很简单的,30MHz x 40 / 6 不就是200MHz吗?为什么芯片会执行不正常呢?

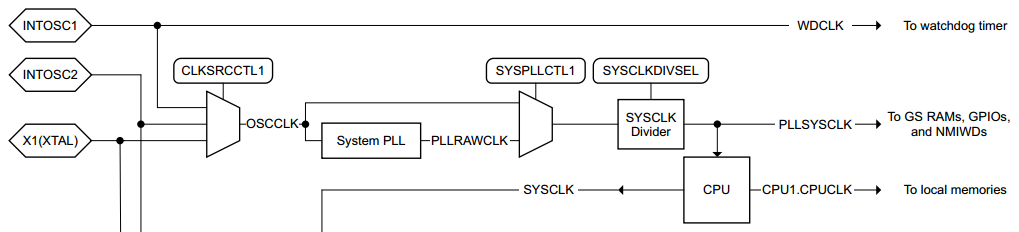

我们来看看,28系列dsp的系统时钟产生模式:

内外部时钟,可通过CLKSRCCTL1来选择哪个作为时钟源,之后所选的时钟源可由SYSPLLCTL1选择是否经PLL倍频后使用,一般为了DSP能够高速运算,我们都会选择使用PLL的。那么经过PLL之后,我们会得到PLLRAWCLK,然后再通过SYSCLKDIVSEL进行分频,最终就会得到我们想要的系统时钟了。

结合上面的代码,倍频过程就是通过IMULT_xx,FMULT_x两个参数实现的,前者代表整数,后者代表小数,具体就不赘述了;分频就是由PLLCLK_BY_x这个参数实现的。

好,说了这么多,还没有说到正题呢,倍频又分频,搞这么多事,问题到底出在哪儿呢?

原来,我们的PLLRAWCLK并不是super man,你跑多快它都能接住,它是有一个acceptable range ,那这个可接受范围是多少呢?

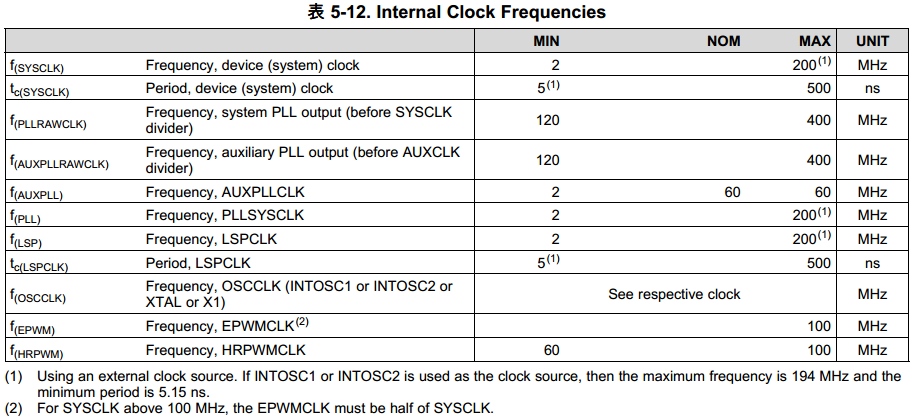

请君移步来看TI公司的28377s的规格文档,在里面表5-12有清晰的说明,如下:

原来PLLRAWCLK最大只能到400MHz,那么反过来看我们前面的配置,30MHz的晶振经过40倍频,已经达到了1200MHz,远远超出了允许范围,DSP很抱歉的说,它玩不转了。

华丽丽的解决方案

原因搞清楚后的感觉真是让人很畅快的,既然搞清楚了原因,那么怎么解决这个问题会比较好呢?当然可以简单的降低倍频,比如30MHz做10倍频,然后2分频,得到150MHz的系统时钟。不过28377s的最大系统时钟可以到200MHz,这样解决貌似还是牺牲了点芯片性能呢。

让我搜肠刮肚的想想,400除以30得13.3333。。。。抱歉,它可以无限循环下去,那么比它小的可以配置的最大数是多少?13.25(小数只能有0,0.25,0.5,0.75四个选择),没错,就是它!这样可以得到397.5MHz的倍频输出,再作2分频,系统时钟198.75MHz,应该是最大限度的利用了。

按照上面的配置,代码如下:

InitSysPll(XTAL_OSC,IMULT_13,FMULT_0pt25,PLLCLK_BY_2);

作者: 大风当歌

出处: https://www.cnblogs.com/arron-zx/>

关于作者:专注于电力电子控制算法及产品设计,新能源及电动汽车等领域

本文版权归作者和博客园共有,欢迎转载,但未经作者同意必须保留此段声明,且在文章页面明显位置给出, 原文链接 如有问题, 可邮件(150509134@qq.com)咨询.