Trace32下对ARM内存访问Access Classes总结

原内容来源于T32帮助文档debugger_arm.pdf的ARM Specific Implementations->Access Classes,这里记录方便查询。

首先介绍Access Classes都有哪些选项,然后介绍常见的Access Classes组合,最后介绍如何创建合法的Access Classes组合。

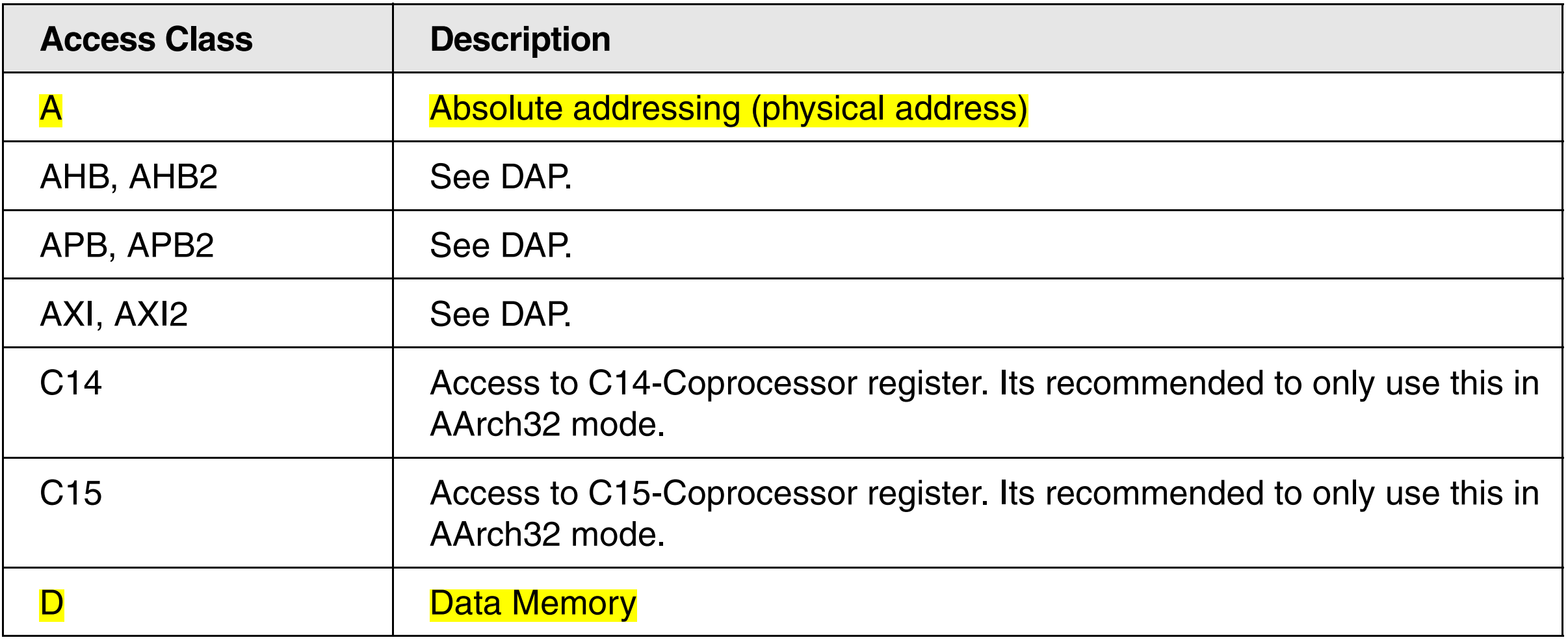

1. 单个Access Classes描述

2. 常见Access Classes组合

在MMU和Cache打开的情况下,默认访问是经过MMU和Cache的。访问的是虚拟内存。

A:访问不经过MMU,但是可能会经过Cache。访问的是物理内存。

NC:访问经过MMU,不经过Cache。

ANC:跳过MMU和Cache直接访问物理内存。

ZSR:访问的是安全区域的ARM32指令。

NUR:0044:00427080:进程号为0x44的非安全(N)用户空间(U)ARM32代码(R)。

NSR:0000:C04F44E4:内核空间非安全(N)特权模式(S)ARM32代码(R)。

在d.dump <Address>时,默认属性等同于当前属性,比如list.auto中为NUR:0044,则显示NUR:0044:<Address>内容。

3. 如何创建合法的Access Classes组合

下面根据发起访问的Master和目标分成几类:

- 通过CPU

- 通过CoreSight

- 访问C15/C14/SystemRegister

- Cache和虚拟内存访问

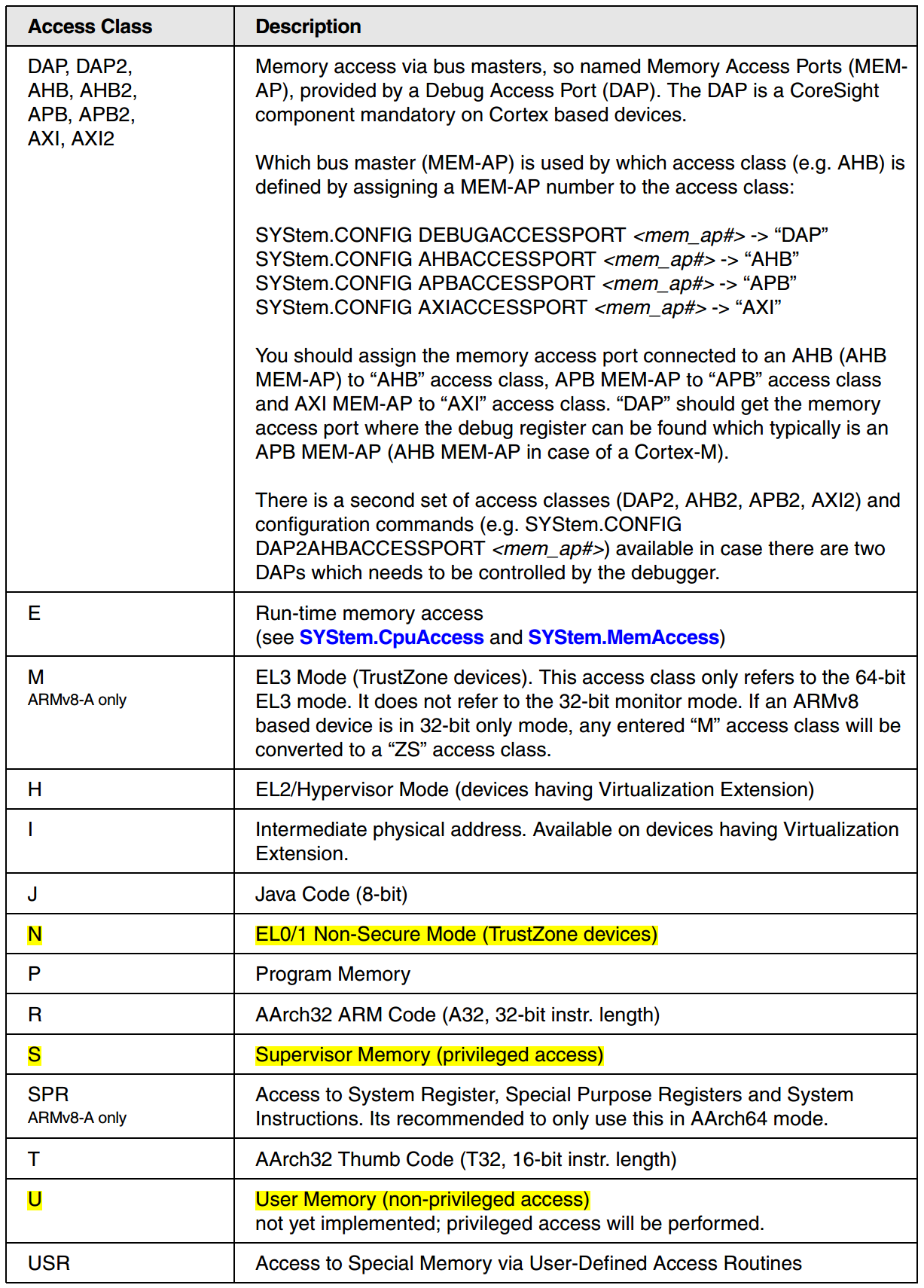

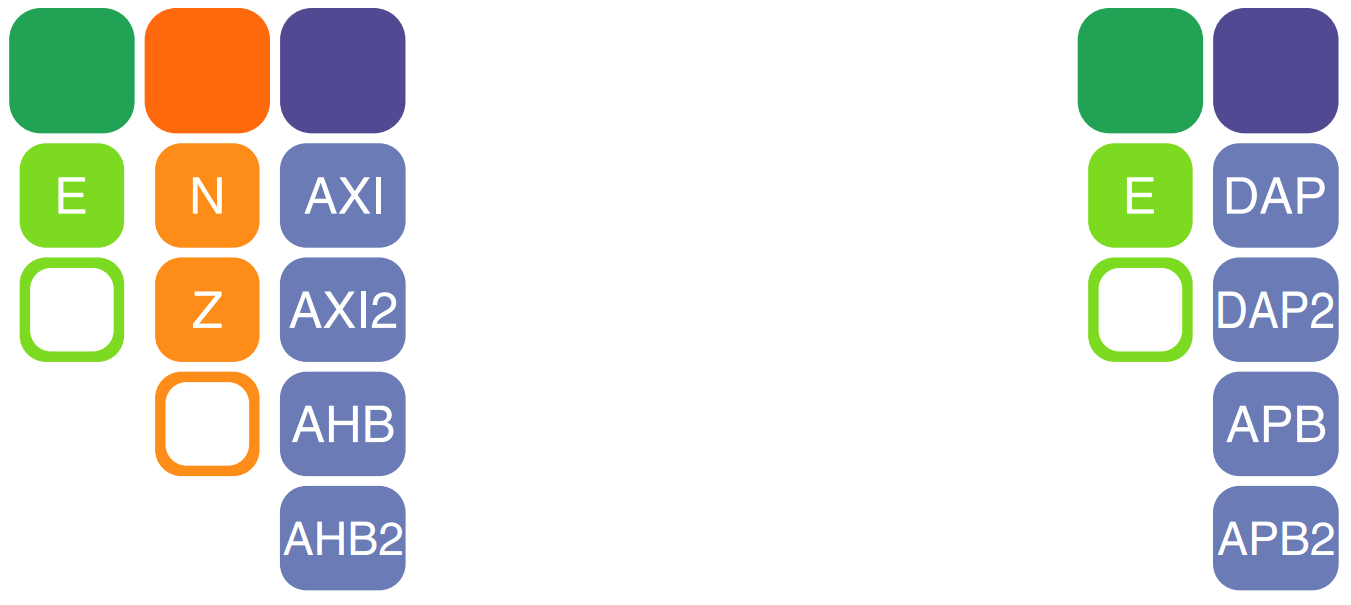

创建Access Classes组合的规则:

- 图示中每一列仅可选一个Access Class

- 仅可跳过有空框的列,否则必选一个Access Class

- 不可改变列顺序

3.1 通过CPU的内存访问

ZSD:前面两个空可以不写,安全模式特权虚拟数据访问。

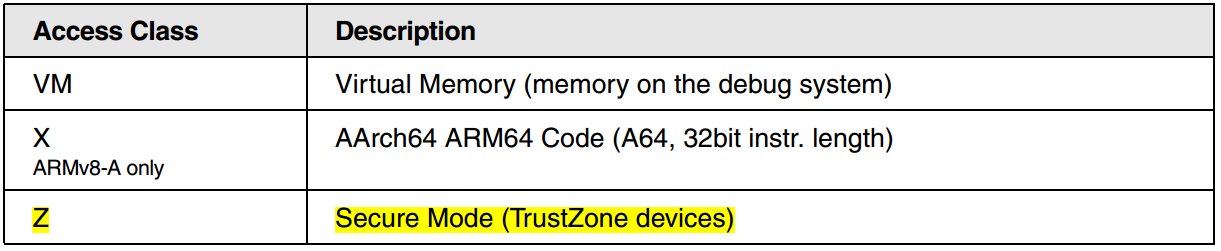

3.2 通过CoreSight访问

EAXI:运行时通过AXI总线访问内存。

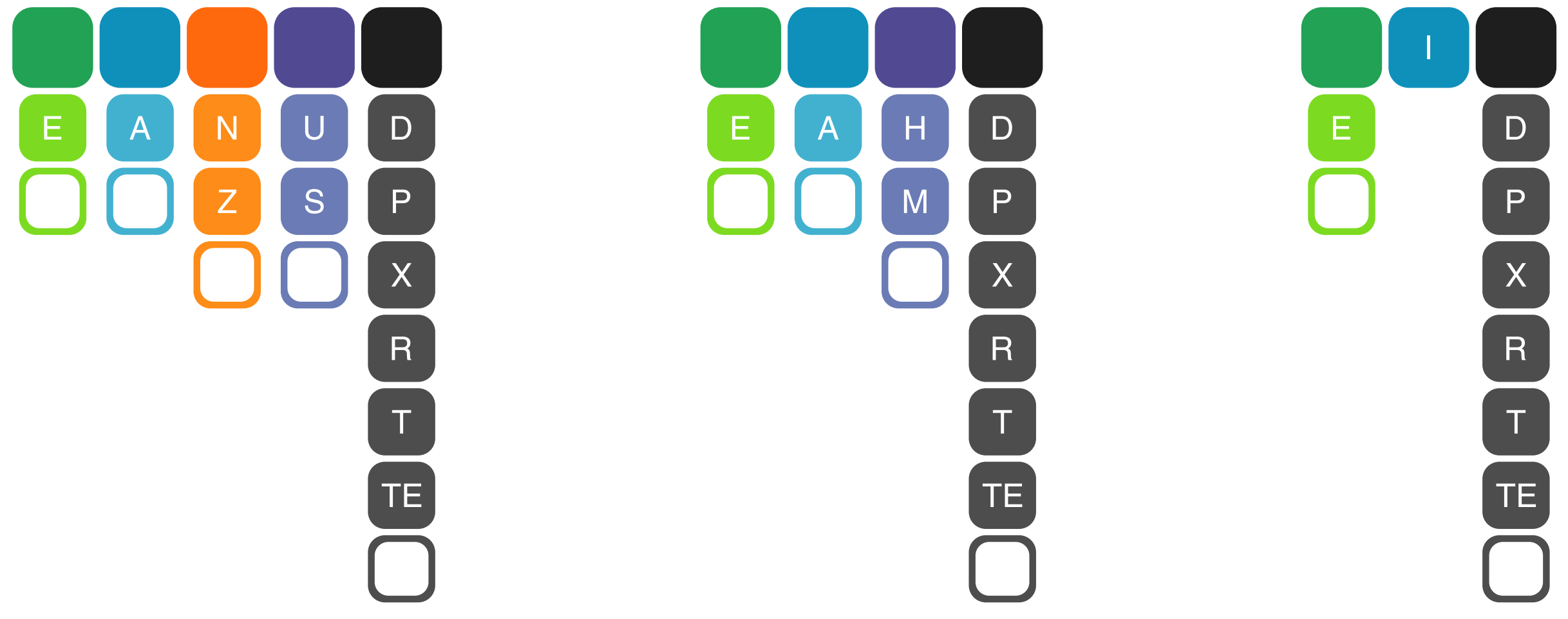

3.3 C15/C14/SystemRegister访问

3.4 Cache和虚拟内存访问

联系方式:arnoldlu@qq.com

浙公网安备 33010602011771号

浙公网安备 33010602011771号