ARM Star技术参考手册笔记

Chapter A1 Introduction

A1.1 About the processor

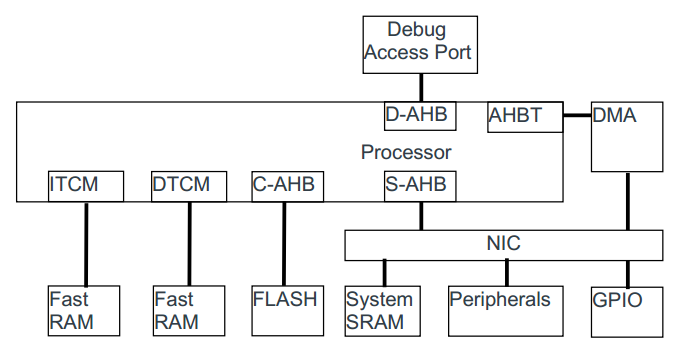

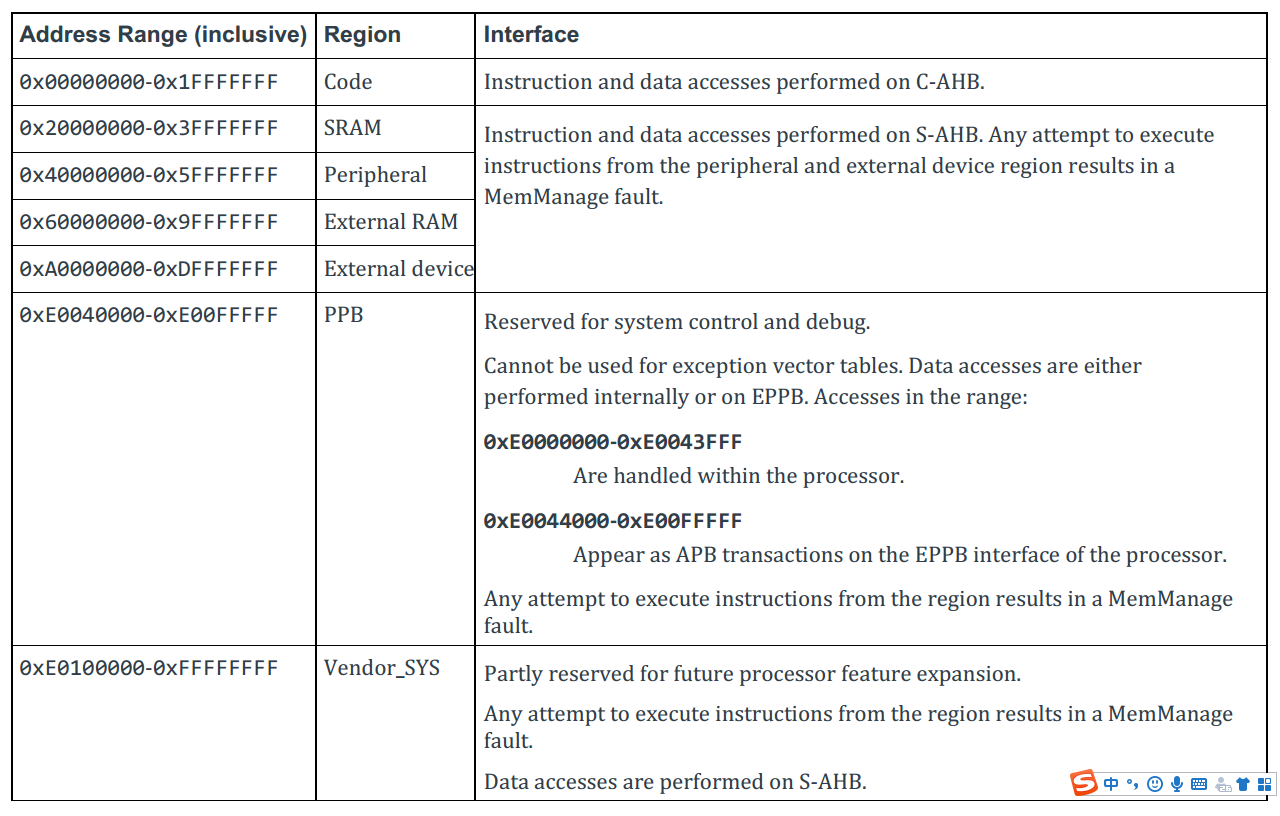

处理器支持的接口包括:

- C-AHB:Code AHB interface。

- S-AHB:System AHB interface。

- D-AHB:Debug AHB interface。

- EPPB:External PPB(Private Peripheral Bus) APB interface。

- TCM interface。

- Harvard I/D cache。

可选配置包括:

- TrustZone

- MPU

- FPU

- ETM和MTB

A1.2 About the processor architecture

处理器包括如下可扩展配置:

- 安全扩展

- 浮点扩展

- DSP扩展

- 调试扩展

处理器特性包括:

- in-order issue pipeline

- Thumb-2

- 大小端

- 最高480中断的NVIC

- 单精度FPU

- exception-continuable instructions

- 调试:断点、视点、跟踪、系统优化、MTB、ETM

- 协处理器接口

- 低功耗:clock gating、sleep mode、WIC

- 存储系统:MPU、SAU、Harvard I/D 缓存

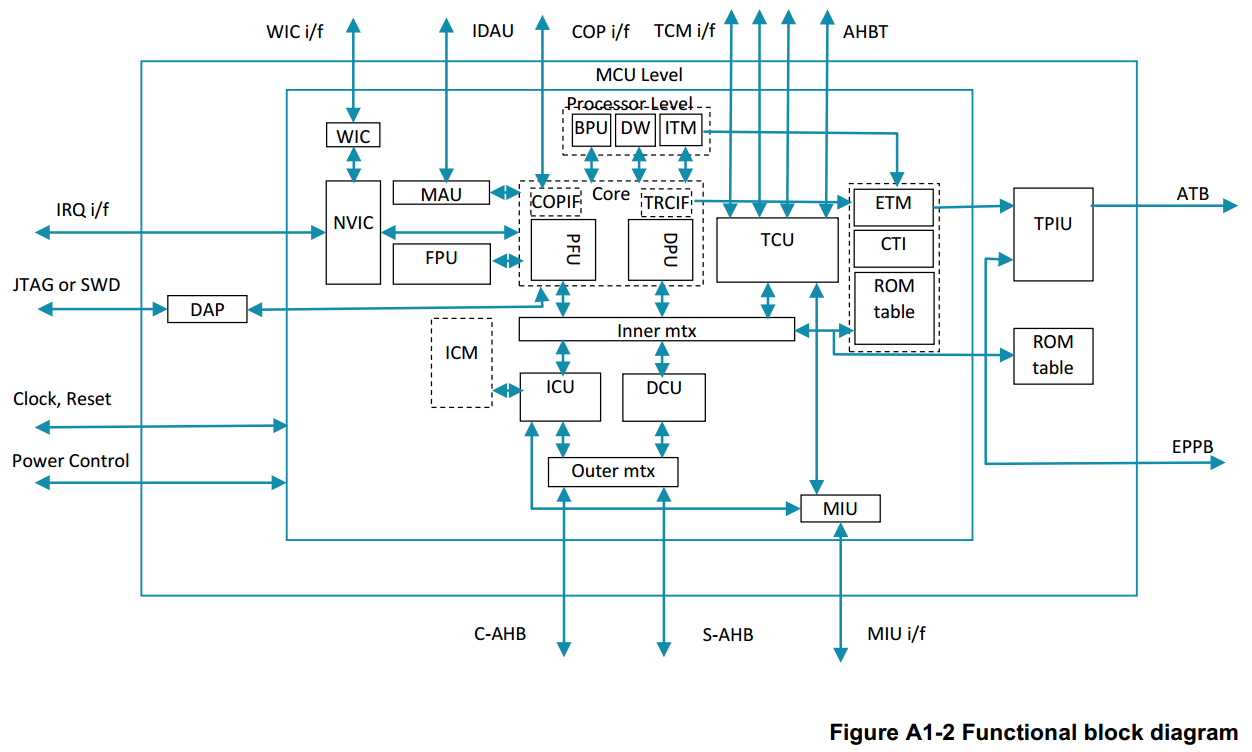

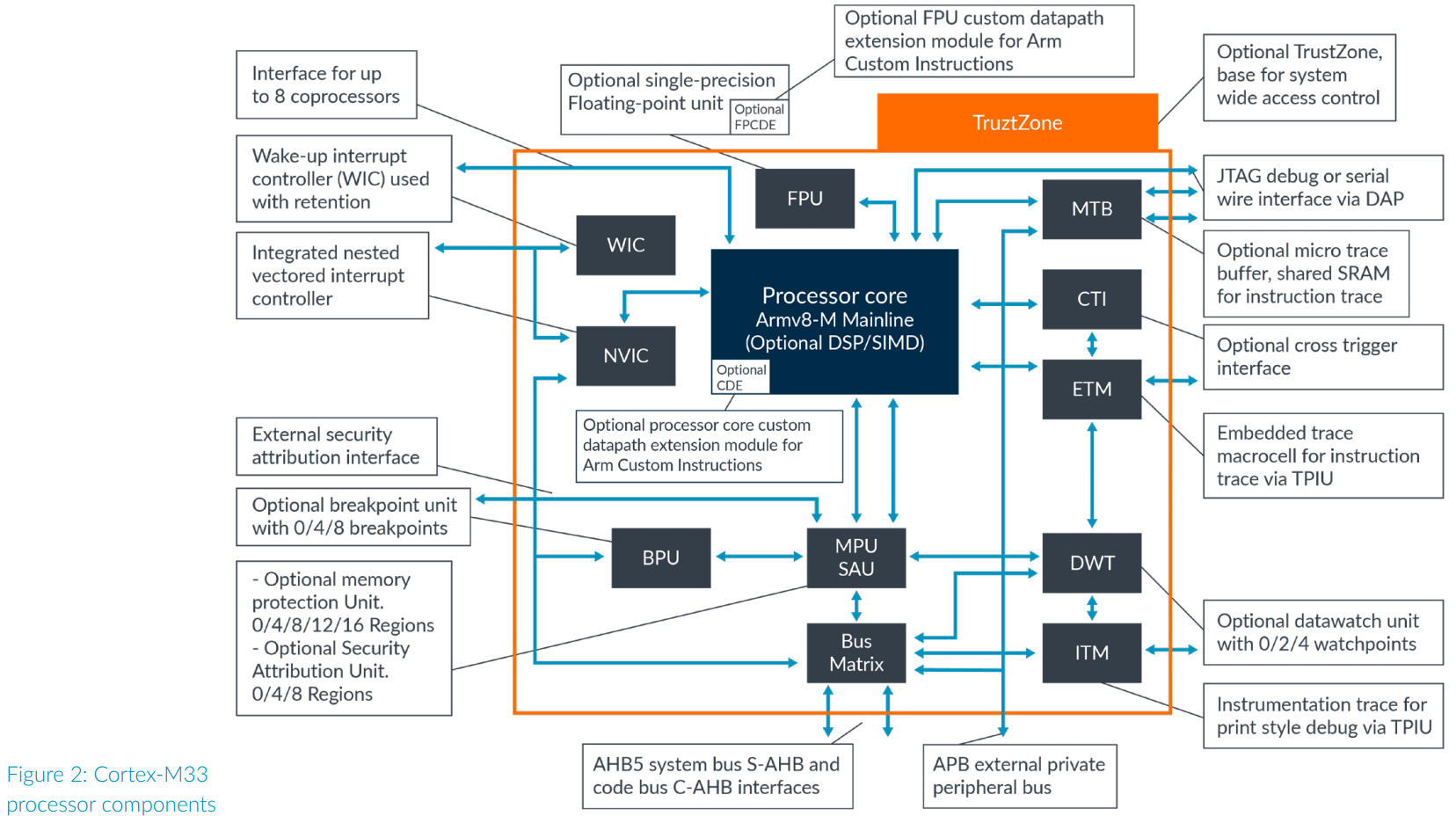

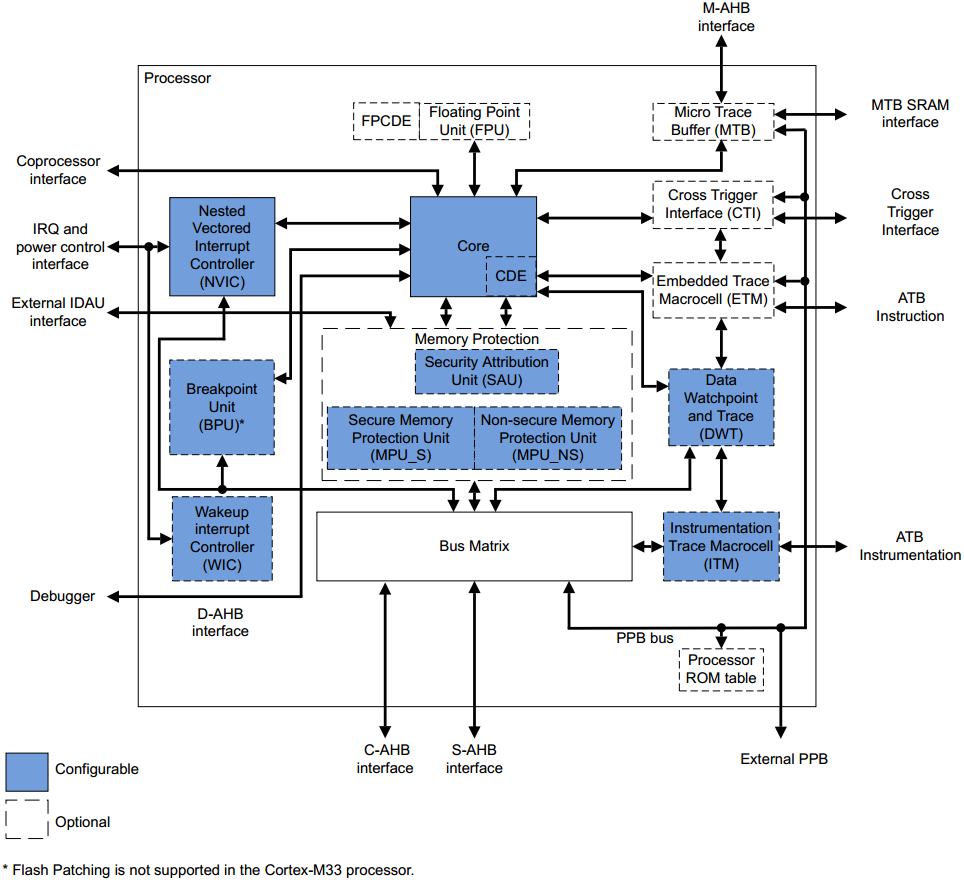

A1.4 Component blocks

核:

- DPU:Data Processing Unit

- PFU:Prefetch Unit

- TRCIF

- COPIF

调试模块:

- DWT:Data Watchpoint and Trace

- BPU:Breakpoint Unit

- ITM:Instrumentation Trace Macrocell

- MTB:Micro Trace Buffer

- ETM:Embedded Trace Macrocell

- CTI:Cross Trigger Interface

- ROM table:

- TPIU:Trace Port Interface Unit

- DAP:Debug Access Port

中断:

- NVIC:Nested Vectored Interrupt Controller

- WIC:Wakeup Interrupt Controller

MPU:

- MPU_NS:

- MPU_S

- SAU

FPU:

- FPU(Float Point Unit)

- FPCDE(Float Point Custom Datapath Extension)

Memory System:

- ICU:

- DCU:

- C-AHB:

- D-AHB:

- MIU:MBIST Interface Unit

M33相关框图如下:

A1.4.1 Processor core

CPU核内的CDE用于支持用户自定义指令ACIs(Arm Custom Instructions)。

A1.4.2 Security attribution and memory protection

ARM对内存保护提供了MPU,并且针对安全和分安全分别提供MPU_S和MPU_NS。

当非法访问产生后,MPU能产生一个异常并告知异常源,并且采取措施或告知系统。

SAU和MPU_S配套使用,提供对非安全访问的隔离。

A1.4.3 Floating-Point Unit

FPU也支持FPCDE,用于支持用户自定义浮点运算指令。

A1.4.4 Nested Vectored Interrupt Controller

NVIC的功能包括:

- 可配置的外部中断1-480,可以连续或者非连续映射。

- 中断优先级等级范围从8-256.

- 中断优先级动态调整。

- 优先级分组。这允许选择抢占中断级别和非抢占中断级别。

- 支持尾链和延迟到达中断。这使得背对背中断处理不需要中断之间的状态保存和恢复开销。

- 可选支持Armv8-M安全扩展。安全中断可以优先于任何非安全中断。

A1.4.5 Cross Trigger Interface Unit

A1.4.6 Memory System

可选的内存系统包括:

- 带C-AHB和S-AHB的BIU

- 带TCM接口的TCU。

- 指令和数据缓存。

- MIU提供的MBIST接口。

A1.4.8 MTB

跟踪数据通过M-AHB接口从处理器提取,并写到SRAM接口。

A1.4.9 Debug and trace

包括BPU、DWT、trace和system profiling。

其他还可能包括:ITM、TPIU/ROM Table等。

A1.5 Interfaces

S-AHB:用于从ARMv8-A内存的SRAM、外设、RAM、外部设备等映射区域取指令以及数据访问。

C-AHB:用于ARMv8-A内存映射代码区域取指令以及数据访问。

E-PPB APB接口:允许访问连接到CPU的CoreSight调试跟踪模块。

安全属性接口(Secure Attribution Interface):允许设置基于地址的安全属性。

ATB接口:输出ETM/ITM调试跟踪数据。

TCM Interface:支持最多2个TCM接口ITCM和DTCM。

AHBT接口:作为AHB-Lite从设备的TCM访问接口。

MTB Interface:Micro Trace Buffer AHB接口SRAM接口。

Coprocessor interface:协处理器接口。

D-AHB接口:允许调试器调试CPU核,访问寄存器、完整内存区域。

CTI:用于CTM(Cross Trigger Matrix)下其他核做Cross Trigger。

Power Control接口:通过Q-Channel对PMU进行开关功耗控制。

Chapter B1 Programmers model

B1.2 Modes of operation and execution

安全:安全状态、非安全状态。

运行模式:

- Thread:复位后默认处于Thread模式,或异常处理结束后返回到Thread模式。代码可以特权或非特权运行。

- Handler:异常发生后进入Handler模式,Handler模式下的代码都是特权访问。

运行状态:

- Thumb:运行16位或32位Thumb指令的普通执行状态。

- Debug:处理器处于Halting调试状态。

访问权限:特权访问和非特权用户访问。

B1.4 内存模型

系统内存子系统仲裁外部内存、内部SCS、调试模块之间的取指令和内存访问。

系统内存映射对调试器和CPU存取一致。

用户和特权访问的内存映射一致,除了PPB仅允许特权访问。

B1.4.1 Private Peripheral Bus

PPB提供如下功能的访问:

- System Control Space:MPU、SAU、NVIC

- DWT

- BPU

- ETM

- MTB

- CTI

- ROM Table

- L1

B1.4.2 Unaligned accesses

B1.5 Exclusive monitor

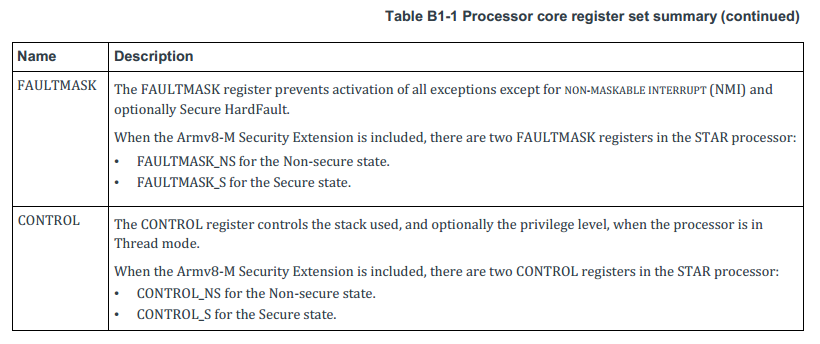

B1.6 Processor core registers summary

每个寄存器都是32位。

R0-R12:数据处理通用寄存器。

SP(R13):栈寄存器。在Thread模式中,可能为MSP或PSP;如果使能安全则可能为MSP_NS/MSP_S/PSP_NS/PSP_S。

MSPLIM/PSPLIM:栈限制寄存器,如果使能安全还包括MSPLIM_NS/MSPLIM_S/PSPLIM_NS/PSPLIM_S。如下将r0表示的stack低地址空间写入msplim,对stack指针进行限制:

msr msplim, r0

LR(R14):存储函数调用、异常返回地址。

PC(R15):保存当前进程运行地址。

PSR:状态寄存器包括 - 应用APSR、中断IPSR、执行EPSR。

B1.7 Exceptions

CPU核和NVIC共同实现了异常处理及其优先级。

当处理异常时:

- 所有异常处理都在Handler模式中进行。

- 异常产生后CPU状态自动保存到栈中,ISR结束后自动从栈中恢复。

- 取异常向量同时进行状态保存,提高中断进入效率。

支持tail-chaining,当多个中断连续发生时,不需要状态保存和回复。

Chapter B2 System Control

B2.1 Identification register summary

此类寄存器表示当前处理器支持哪些特性和功能。

B2.2 Auxiliary Control Register

ACTLR寄存器用于软件控制处理器的特性和功能,包括FPU、Dual-issue、多Cycle指令是否允许中断的配置。

Chapter B3 Memory System

B3.1 About the memory system

Star的存储系统包括:

- 可选的分开指令和数据缓存。

- 可选多TCM区域。

- ITCM

- DTCM - D0TCM和D1TCM

- TCM AHB从设备接口。

- 可选MPU,负责对所有访问进行保护检查、地址访问权限、内存属性。

- MBIST接口。

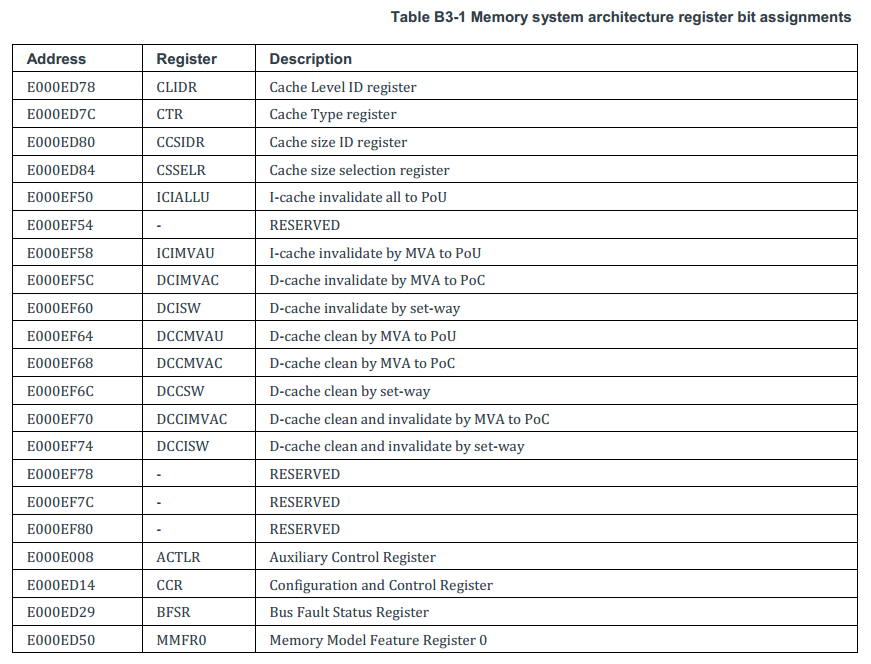

B3.2 Memory system architecture register summary

PoU和PoC区别?

PoC全局缓存一致性角度:系统中所有可以发起内存访问的硬件单元,都能保证观察到的某一个地址的数据是一致的。

PoU处理器缓存一致性角度:表示站在处理器角度来看高速缓存的一致性问题。

基于地址和set/way区别?

指的是缓存操作的范围:整个缓存、某个地址、某个set/way。

Clean和Invalidate区别?

Clean将cache中尚未写入到主存储器中的数据写回主存储器中。

Invalidate也即flush,将cache中invalid标志位置为1,使cache中内容无效。对于写回类型的数据cache来说,使无效,并不使数据写到主存中。

指令缓存不存在clean,因为不需要写回驻存。数据缓存存在invalidate、clean、clean and invalidate三种情况。

还可以通过对某块内存进行清0操作,高速缓存控制器会主动将这些零数据写入高速缓存中。

缓存寄存器总结

通用操作:

- CLIDR:Cache Level ID Register

- CTR:Cache Type Register

- CCSIDR:Current Cache Size ID register

- CSSELR, Cache Size Selection Register

指令缓存操作:

- ICIALLU:是所有指令Cache失效到PoU。

- ICIMVAU:基于地址使指令缓存行失效到PoU。

数据缓存操作:

- 失效缓存:

- DCIMVAC:Data Cache line Invalidate by Address to PoC

- DCISW:Data Cache line Invalidate by Set/Way

- 清缓存:

- DCCSW:Data Cache Clean line by Set/Way

- DCCMVAC:Data Cache line Clean by Address to PoC

- DCCMVAU:Data Cache line Clean by address to PoU

- 清并失效缓存

- DCCISW, Data Cache line Clean and Invalidate by Set/Way

- DCCIMVAC, Data Cache line Clean and Invalidate by Address to PoC

B3.3 Memory system implementation-defined register summary

B3.4 Fault handling

取指可能触发的异常:

- SAU SecureFault.

- MPU MemManage.

- External C-AHB or S-AHB error (HRESP).

- TCM external error.

- TGU security fault.

- Breakpoints, and vector capture events.

数据访问可能触发的异常:

- SAU SecureFault.

- PU MemManage.

- Alignment UsageFault.

- External C-AHB or S-AHB error (HRESP).

- PPB and external PPB BusFault.

- TCM external error.

- TGU security fault.

- Watchpoints

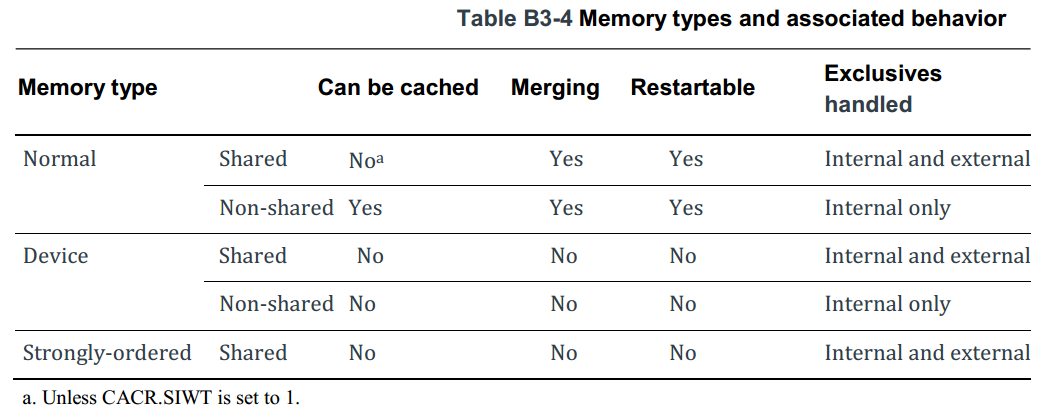

B3.5 Memory types and memory system behavior

- 仅Normal、Non-shared内存能够被缓存

B3.6 Code and System AHB interfaces

C-AHB接口用于对ARMv8-M内存映射Code区域的取指和数据访问。

S-AHB接口用于对内存映射区的SRAM、外设、External RAM、External设备的取指和数据访问。

B3.7 AHB slave for TCM interface

B3.9 L1 caches

被缓存的指令或数据是通过C-AHB或S-AHB接口从外部内存取到的。

任何不通过TCM或PPB接口的访问都会被缓存控制器合适的处理。

Cache的缓存填充分配有Read-Allocate和Write-Allocate两种。

Cache line缓存首先取请求的数据,并返回,然后再取其余的数据。

| Cache | Main memory | |

| Non-cacheable | N | N |

| Write-Back | Y | N |

| Write-Trhough | Y | Y |

数据缓存为4-way set-associative,指令缓存为2-way set-associative。

缓存行大小为32字节。

B3.9.1 Cache maintenance operations

通过写PPB内存中SCS区域寄存器执行cache维护操作,数据cache支持的操作有:

- 通过地址失效cache

- 通过Set/Way组合失效cache

- 通过地址清空cache

- 通过Set/Way组合清空cache

- 通过地址清空并失效

- 通过Set/Way组合清空并失效

指令cache支持的操作有:

- 所有指令失效

- 通过地址失效指令

B3.9.2 Cache interaction with memory system

Cache和内存系统交互:

- 使能或去使能指令cache后,必须使用ISB来flush pipeline,确保指令cache的使能或关闭对后续取指操作生效。

- 复位后,使用前必须是所有cache失效。如果复位释放后INITL1RSTDIS也被释放,那么硬件会自动使I、D缓存失效。

- 如果要关闭数据缓存,必须清空缓存来确保所有脏数据刷回到外部内存。

- 在使能数据缓存前,必须使所有数据缓存失效,因为外部内存有可能在数据缓存关闭期间修改。

- 在使能指令缓存前,必须是所有指令缓存失效,因为外部内存有可能在指令缓存关闭期间修改。

Chapter B4 安全属性和内存保护

SAU决定一个地址的安全属性,仅在支持ARMv8-M安全扩展时实现。支持的分区数可以是0、4、8。

当非安全状态发起安全地址数据访问,会产生一个SecureFault异常到CPU。

当安全状态发起非安全地址数据访问,相关的内存访问被认为是非安全访问。

MPU支持的工作包括:

- 保护一块区域,支持0、4、8、12、16块区域配置。

- 访问权限控制。

- 导出内存属性给系统。

MPU非法访问或不当使用会触发MemManage异常。

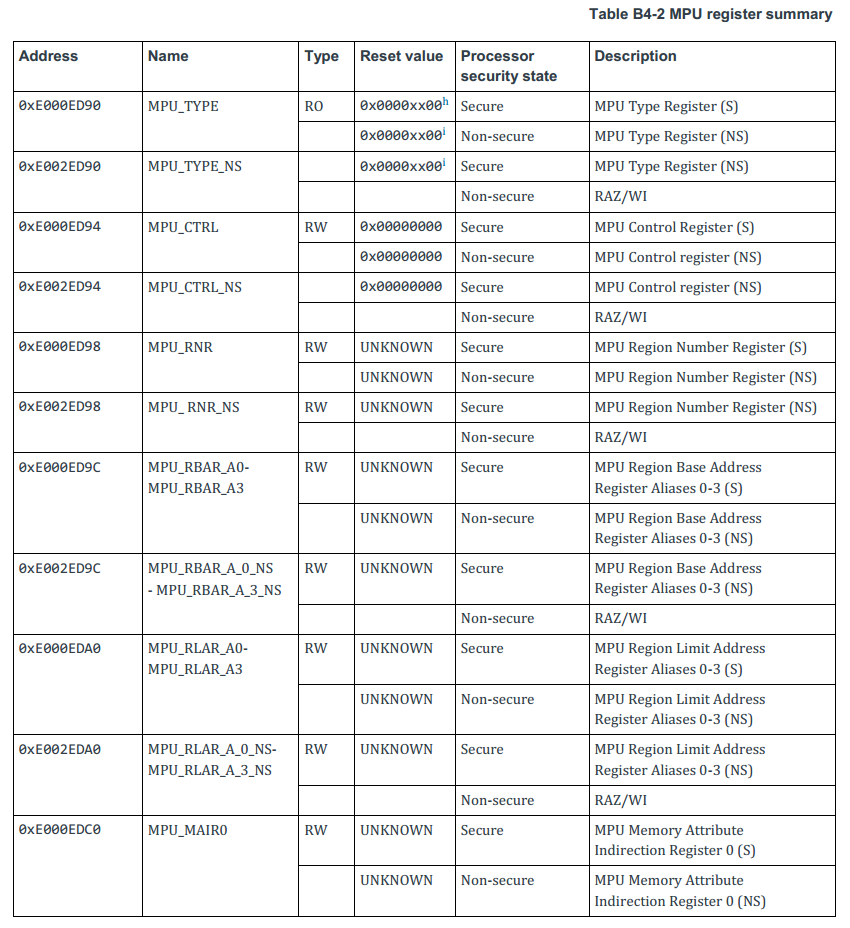

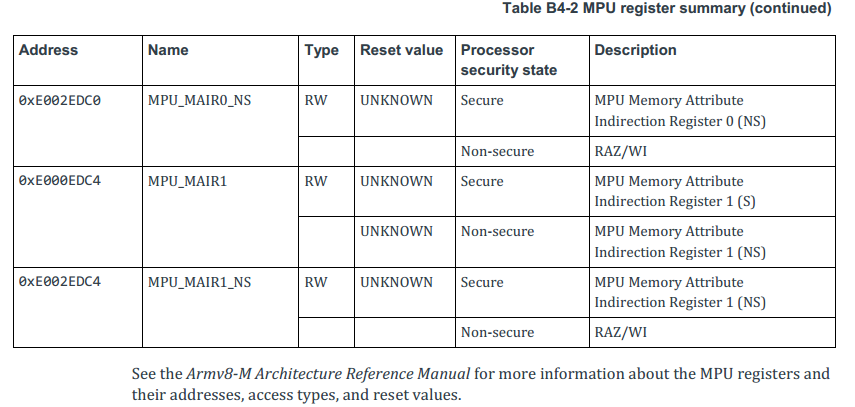

B4.3 MPU register summary

Star MPU相关寄存器如下:

- MPU_TYPR:为只读寄存器,表示当前安全等级下MPU分区数;ARMv8-M只支持一体分区,没有代码和数据独立分区。

- MPU_CTRL:用于对MPU使能、特权操作、HardFault和NMI异常等设置。

- MPU_RNR:设置当前要被设置MPU_RBAR和MPU_RLAR的分区。

- MPU_RBAR和MPU_RLAR:设置地址区域地址范围,以及共享特性、读写、执行权限、使能、特权执行、以及MPU_MAIR0和MPU_MAIR1属性索引。

- MPU_MAIR0和MPU_MAIR1:8组属性。

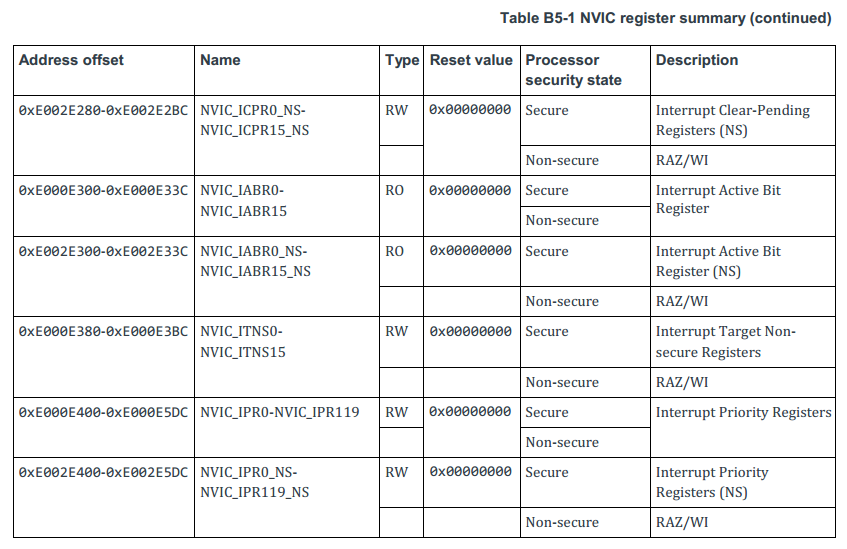

Chapter B5 Nested Vectored Interrupt Controller

中断相关寄存器如下,主要对中断进行Enable、Active、Pending、优先级、安全等设置。

- ICSR:对NMI、Pen的SV、SysTick和中断控制和状态获取。

- ICTR:指示系统中支持的最大中断数量。

- NVIC_IABRn:判断中断状态是否Active。读1为Active。

- NVIC_ISERn:中断使能设置,写1表示使能。

- NVIC_ICERn:中断去使能设置,写1表示关闭。

- NVIC_ISPRn:设置中断Pending状态,写1表示使中断Pending。

- NVIC_ICPRn:中断清Pending状态设置,写1表示清Pending状态。

- NVIC_IPRn:设置中断优先级。

- NVIC_ITNSn:配置中断为安全还是非安全中断。1为非安全。

Chapter C1 Debug

CTI control:CTI

Trace control:ETM、MTB

Debug control:SCS

Instrumentation trace control:ITM

Breakpoint control:BPU

Watchpoint control:DWT

浙公网安备 33010602011771号

浙公网安备 33010602011771号