ARM CoreSight Debug and Trace

关键词:CoreSight、DAP、ECT、STM、ETM、TPIU、TMC、ETB、ETF、ETR等等。

关联文档:《Linux Self-Hosted CoreSight分析》

Chapter 1 Introduction

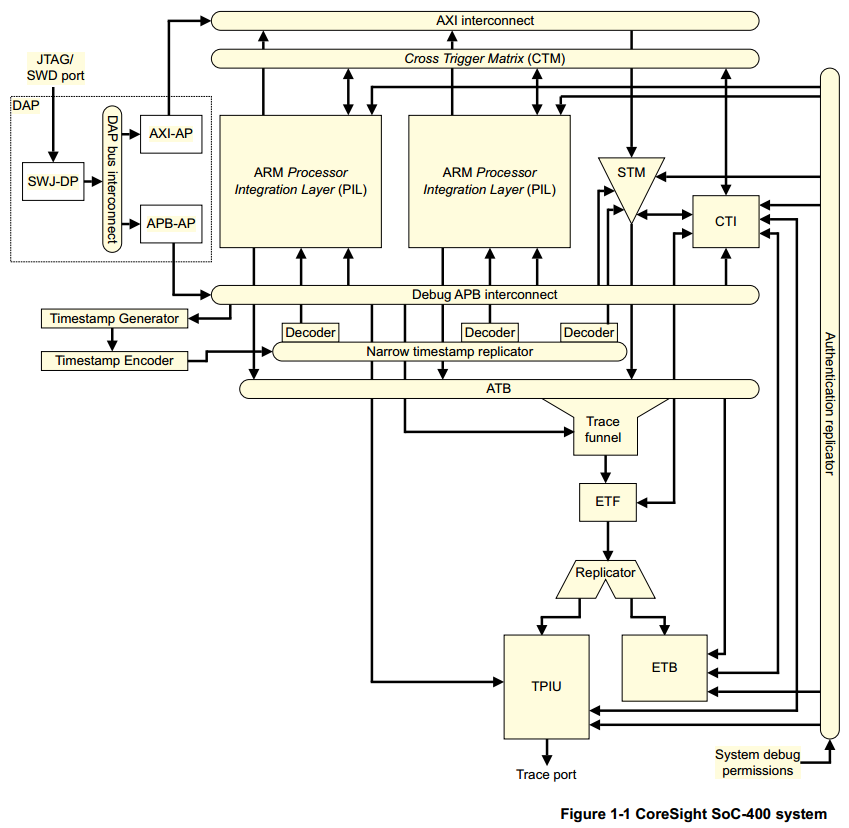

1.1.1 Structure of CoreSight SoC-400

CoreSight Soc-400一个完整的调试和跟踪解决方案,包括如下组件:

- 控制和接入组件:

- DAP(Debug Access Port):用来连接外部硬件调试工具的物理接口,允许外部调试工具访问芯片上CPU、CoreSight、DDR等。

- ECT(Embedded Cross Trigger)

- 跟踪数据源:跟踪源是CoreSight中用于产生跟踪信息的组件。每个跟踪源组件都会产生一种格式的信息,最终可以组合在一起并且通过跟踪链接到输出端口。

- PTM(Program Trace Macrocell):监控处理器运行状况,将处理器执行过的指令信息进行压缩传输。

- STM(System Trace Macrocell):捕捉系统的事件信息并以获取数据跟踪形式传输到跟踪漏斗或跟踪输出组件。

- ETM(Embedded Trace Macrocell):监控处理器运行状况,将处理器执行过的指令信息进行压缩传输。跟踪指令执行、数据搬运、PE(Processing Element)事件。

- 连接:

- Synchronous 1:1 ATB bridge:

- Replicator:可以把单个输入复用到两个分支输出,可以使得CoreSight系统跟踪信息同时传输到两个或多个输出。

- Trace Funnel:把CoreSight系统中多个跟踪源产生的信息组合在一起并以单个流输出到高级跟踪总线ATB。Funnel之间可以级联,一个Funnel最多可以支持6个跟踪源信息输入。

- 跟踪输出节点:

- TPIU(Trace Port Interface Unit):把捕捉到的数据导出到外部调试适配器,如DSTREAM。

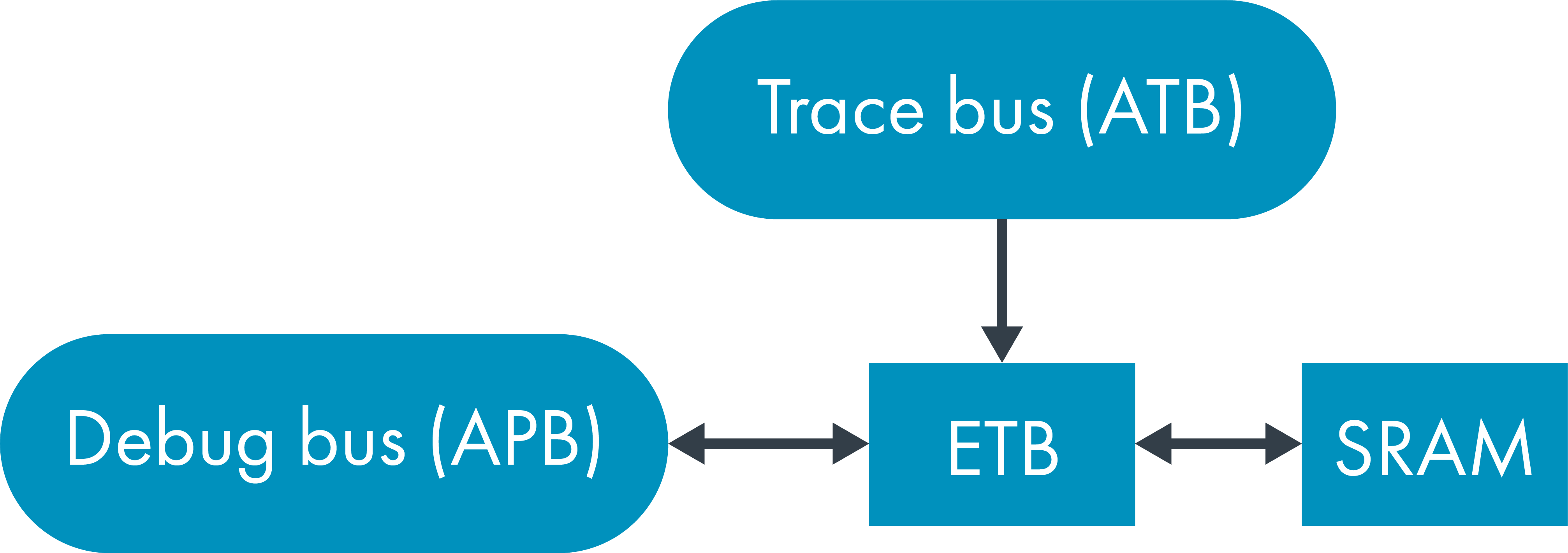

- ETB(Embedded Trace Buffer):是芯片内一块RAM,用来存储捕捉到的跟踪信息。可以通过DAP访问存储在ETB中的数据。

- TMC(Trace Memory Controller):在芯片设计时可配置,配置成ETB时跟上面介绍的ETB功能一致。还可以配置成ETR和ETF。

- ETR(Embedded Trace Router):把跟踪数据存储到调试目标平台的系统内存上,存储系统内存空间是可配置的。

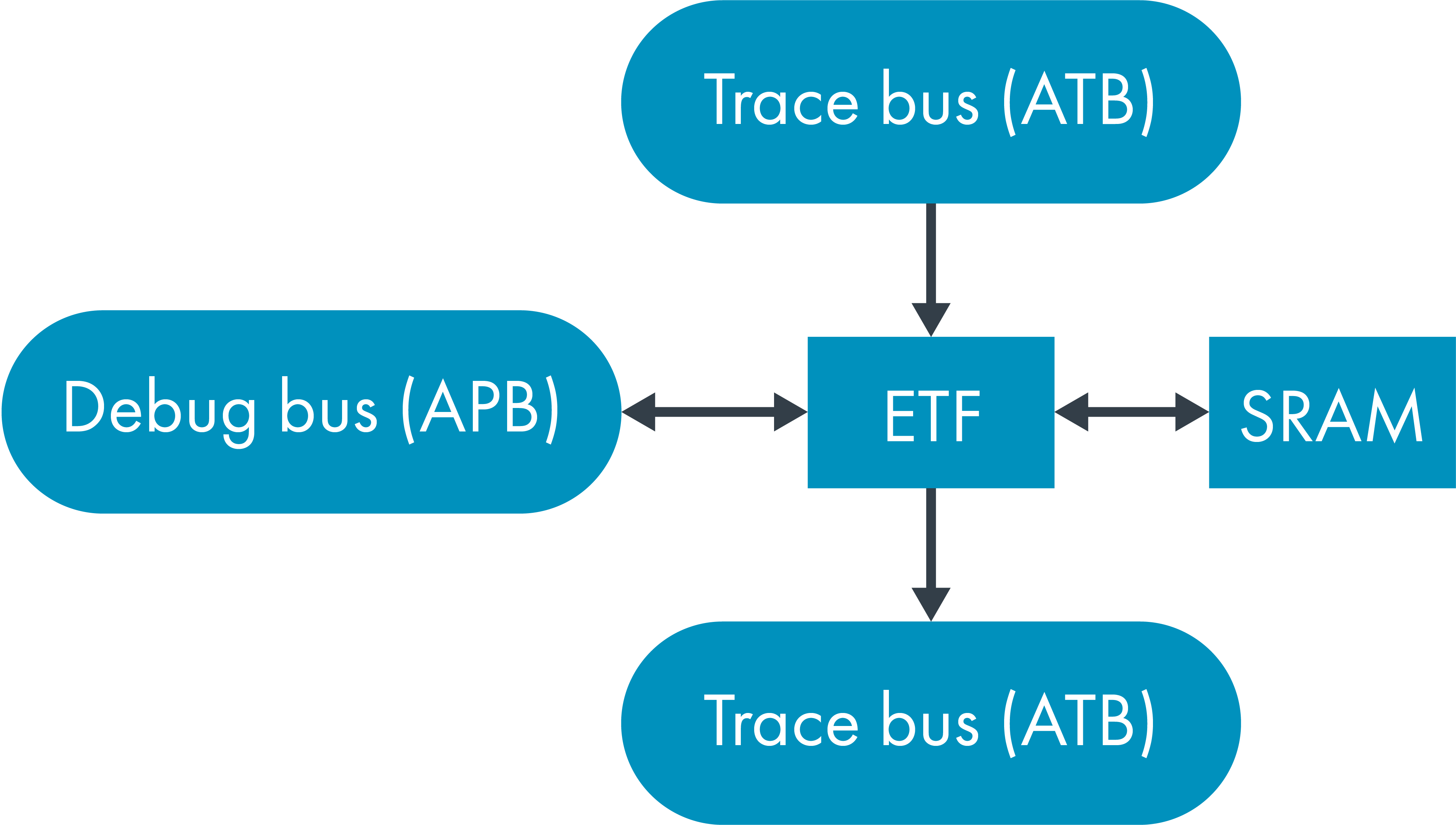

- ETF(Embedded Trace FIFO):主要是缓冲数据的输出,尤其当当量数据在瞬间产生式,通过ETF可以平滑数据的输出速率。缓存可以被配置为FIFO或Circular Buffer;FIFO满了之后就会反压,源头停止输出跟踪数据;Circular Buffer满了后则会覆盖。

时间戳组件:产生CoreSight或处理器所需的时间戳。通过Narrow timestamp replicator分发到多个目的设备。路径:时间戳发生器->时间戳编码器->Narrow timestamp replicator->时间戳解码器->CPU/CTI等。

- 时间戳发生器

- 时间戳编码器

- 时间戳解码器

1.1.3 Typical CoreSight SoC-400 system

2. Functional Overview

2.1 DAP组件

DAP是片外调试工具用于访问SOC的一系列组件统称。包括:

- Serial Wire or JTAG Debug Port

- DAP Bus interconnect

- DAP Bus async bridge

- DAP Bus sync bridge

- JTAG AP

- AXI/AHB/APB AP

2.2 APB组件

用于构建调试APB互联组件。

- APB interconnect with ROM table

- APB async bridge

- APB sync bridge

2.3 ATB interconnect components

通过ATB互联套件将跟踪数据在CoreSight中传输。

- ATB replicator

- ATB funnel

- ATB upsizer

- ATB downsizer

- ATB asynchronous bridge

- ATB synchronous bridge

- ATB Phantom Bridges

2.4 Timestamp components

生成CoreSight系统中使用的时间戳。

- Timestamp generator

- Timestamp encoder

- Narrow timestamp replicator

- Narrow timestamp asynchronous bridge

- Narrow timestamp synchronous bridge

- Timestamp decoder

- Timestamp interpolator

2.5 ECT组件

交叉触发组件用于将一个调试事件从一个调试组件传输到另一个:

- Cross Trigger Interface:合成并映射触发请求,并广播到ECT子系统其他接口。

- Cross Trigger Matrix:进行触发事件分发模块,最少连接两个CTI到其他CTM。

- Event async bridge

2.6 Trace Sink components

CoreSight使用TPIU/ETB等组件将接收调试信息并转发到调试设备或RAM中。

- TPIU:连接ATB和外部跟踪接口。

- ETB:将跟踪数据保存在片内RAM中。

2.7 Authentication bridges

在使能了安全功能的CoreSight系统中,authentication bridge提供经认证的调试控制连接。

- Authentication replicator:将认证信号从一个master传到多个slave。

- Authentication async bridge

- Authentication sync bridge

2.8 Granular Power Requester

3. Programmers Model

详细介绍了各模块的寄存器,包括GPR、APB、ATB Funnel、ATB Replicator、ETB、TPIU、CTI、DAP、Timestamp。

由于ETM属于CPU一部分,参照A55 TRM C3 ETM。

TMC

The Arm CoreSight Trace Memory Controller (TMC) is a configurable trace component to terminate trace buses into buffers, FIFOs, or alternatively, to route trace data over AXI to memory or off-chip to interface controllers.

TMC可以配置成3中模式:

- Embedded Trace Buffer:提供一个circular buffer存储trace。

- Embedded Trace FIFO:将trace存储到专用SRAM中,作为FIFO或者circular buffer通过APB接口访问。

- Embedded Trace Router:将trace数据路由到其他存储设备或者AXI从设备上。

浙公网安备 33010602011771号

浙公网安备 33010602011771号