《安富莱嵌入式周报》第298期:迷你火星探测器,开源单片机3D实时渲染库, 开源USB工业相机,VS2022开始支持MarkDown,PC-lint 2.0发布

往期周报汇总地址:http://www.armbbs.cn/forum.php?mod=forumdisplay&fid=12&filter=typeid&typeid=104

上周更一期视频教程:

BSP视频教程第25期:CAN/CANFD/CANopen专题,CAN知识点干货分享, 收发执行过程和错误帧处理(2023-01-03)

https://www.armbbs.cn/forum.php?mod=viewthread&tid=117387

视频版:

https://www.bilibili.com/video/BV1q44y1974V

1、迷你火星探测器

https://github.com/NikodemBartnik/Pico-Mars-Rover

非常有意思的设计,作者从3D打印,硬件,软件设计一条龙,作者全部开源了,大家有兴趣可以看看

动态效果(末尾是小车带的摄像头拍的)

整体效果:

2、全开源的交互式动画可视数学组件mafs

https://github.com/stevenpetryk/mafs

https://mafs.dev/

这个是基于React(用于构建用户界面的JS库)实现,方便大家构建自己可视化数学效果

比如这里向量场效果:

贝塞尔曲线

运动曲线

3、全开源单片机2D/3D渲染库EmberGL

https://github.com/EmberGL-org/EmberGL

EmberGL(Ember Graphics Library)是底层开源图形库,类似于OpenGL / DirectX / Vulkan,设计用于单片机和其他内存受限的非GPU系统上的实时2D / 3D渲染。图形 API 专为此类系统设计,利用现代技术能够在紧张的内存预算内最大限度地提高渲染性能,同时提供很大的灵活性和可定制性。

展示下DMA方式驱动ILI9341的效果:

4、总线接口知识点汇总

http://www.interfacebus.com/Interface_Bus_Types.html

网站还不错,汇总了一些常用接口知识点整理

比如I2C

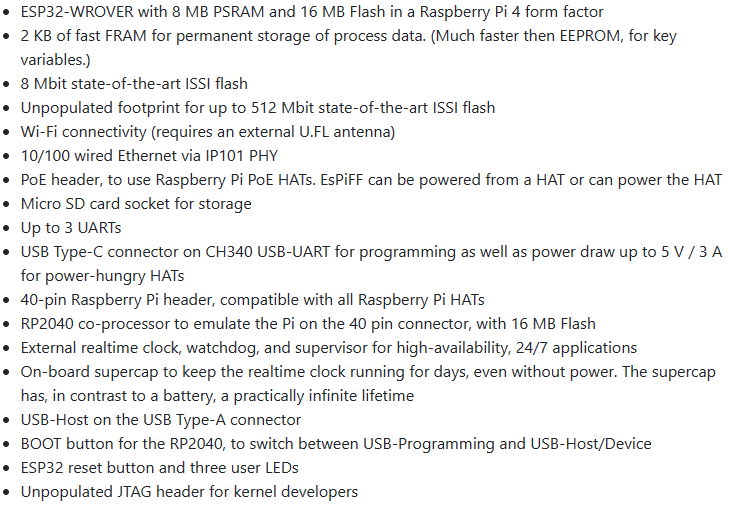

5、ESP32+RP2040的二合一设计板

https://github.com/MDCservice/EsPiFF

大家可以看看有没有可以参考的,整体设计不错

规格:

效果:

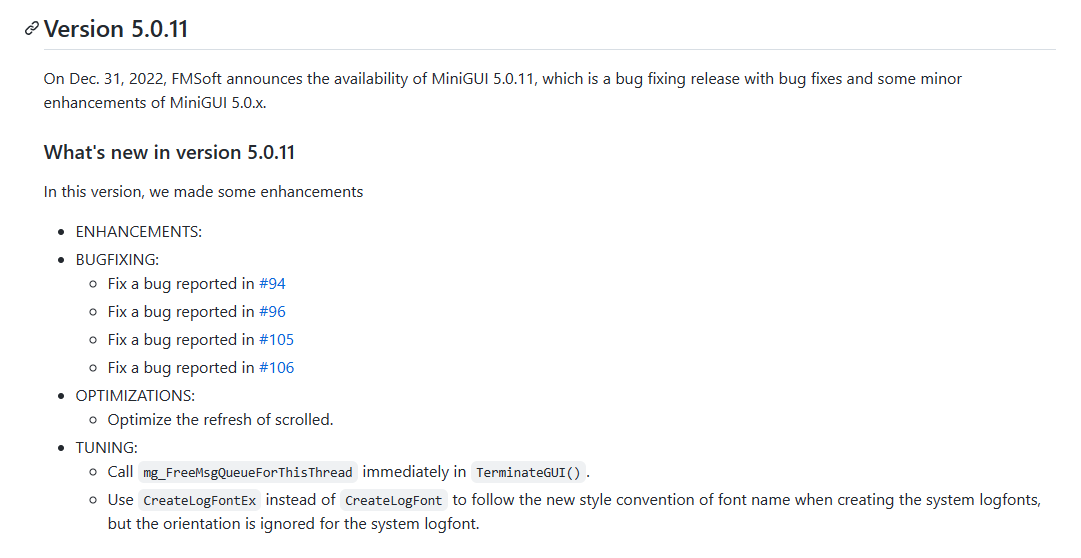

6、飞漫的MiniGUI发布5.0.11

不容易,还在持续的更新中,我们上学那会就是用的这个还有uCGUI3.X

https://github.com/VincentWei/minigui/blob/rel-5-0/RELEASE-NOTES.md#whats-new-in-version-5011

这个应该是我们国内最早的GUI组件了。

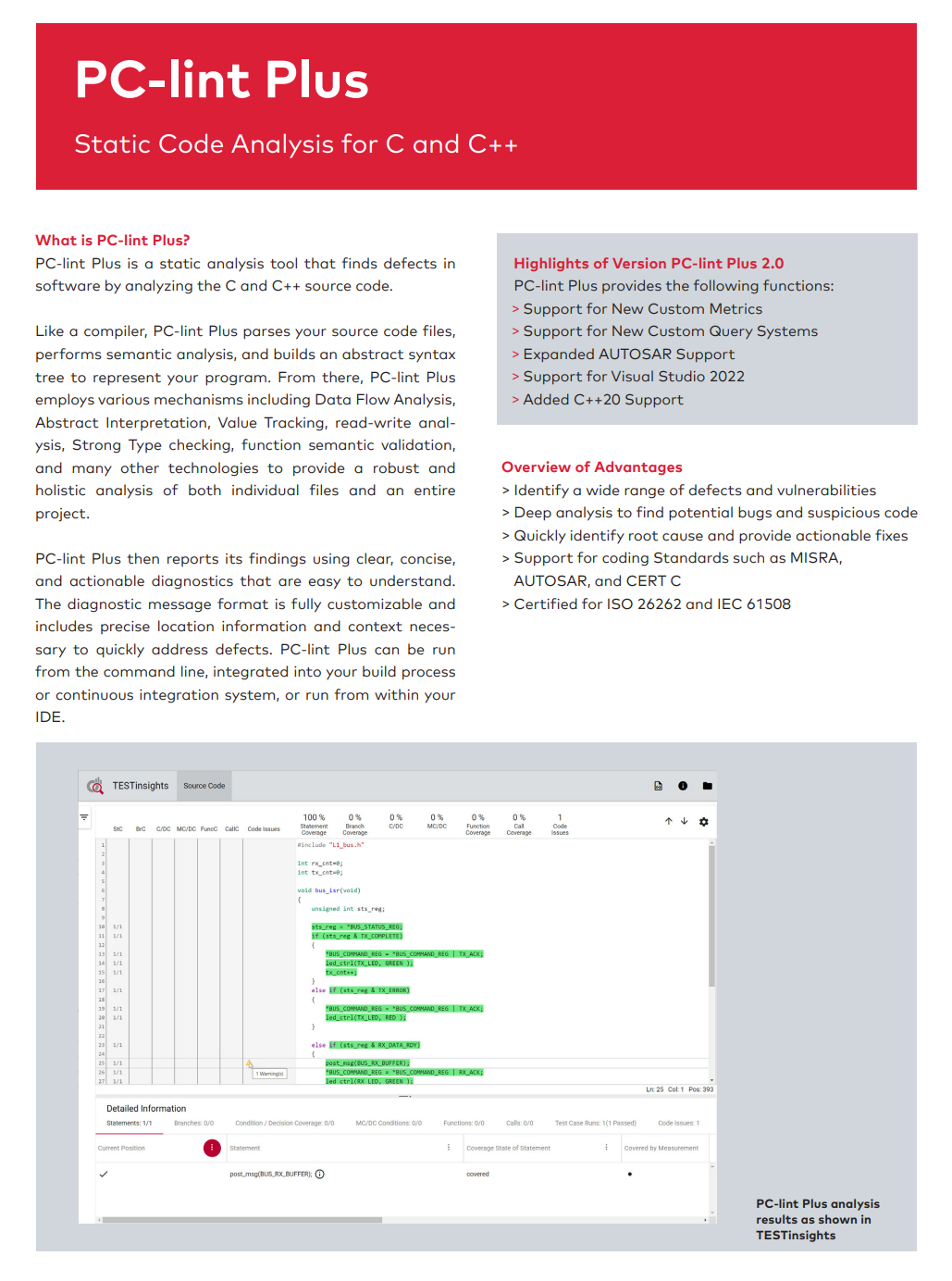

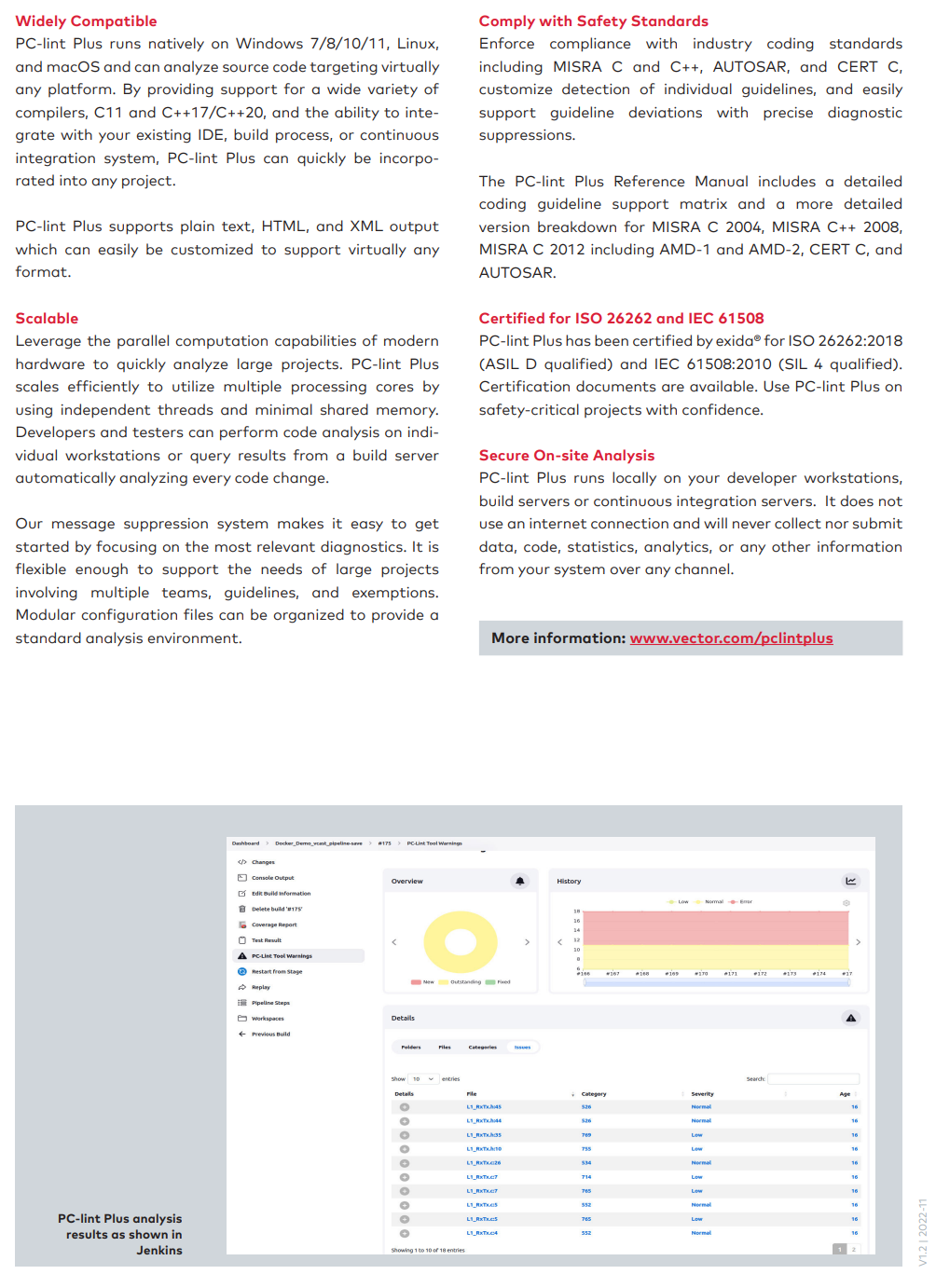

7、PC-lint Plus 2.0发布

https://pclintplus.com/downloads/

主要用于C/C++的静态代码分析。

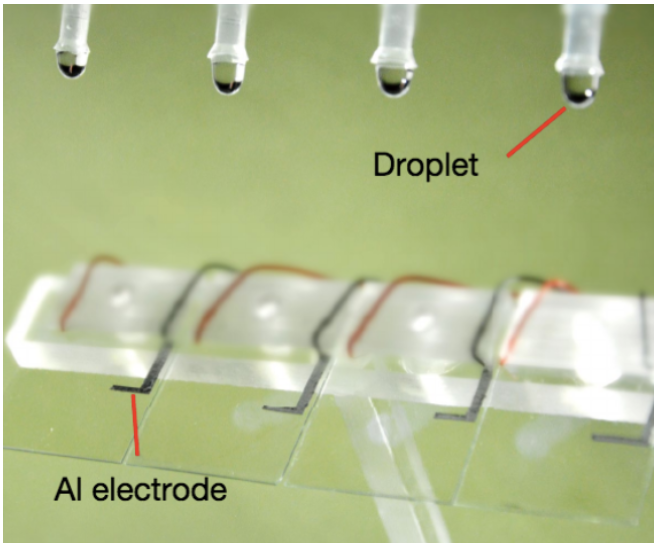

8、微型发电机可以用一个雨滴点亮100个LED灯泡

一项非常有意思的研究,研究人员设计了一种微小但高效的发电机,可以产生足够的电力,只需一滴水,雨水或海水即可点亮100个LED灯泡

9、Creative Commons知识共享许可

https://creativecommons.org/licenses/by-nc-nd/3.0/deed.zh

非常好的许可协议,文档资料等开源,可以考虑下这种开源协议

10、CiA联盟分享的2023年CAN总线工作安排

https://www.can-cia.org/services/publications/can-info-mail-2022/

主要是一些文档的更新,设备测试,研讨会等。当前CiA整理的CAN文件有2万多页

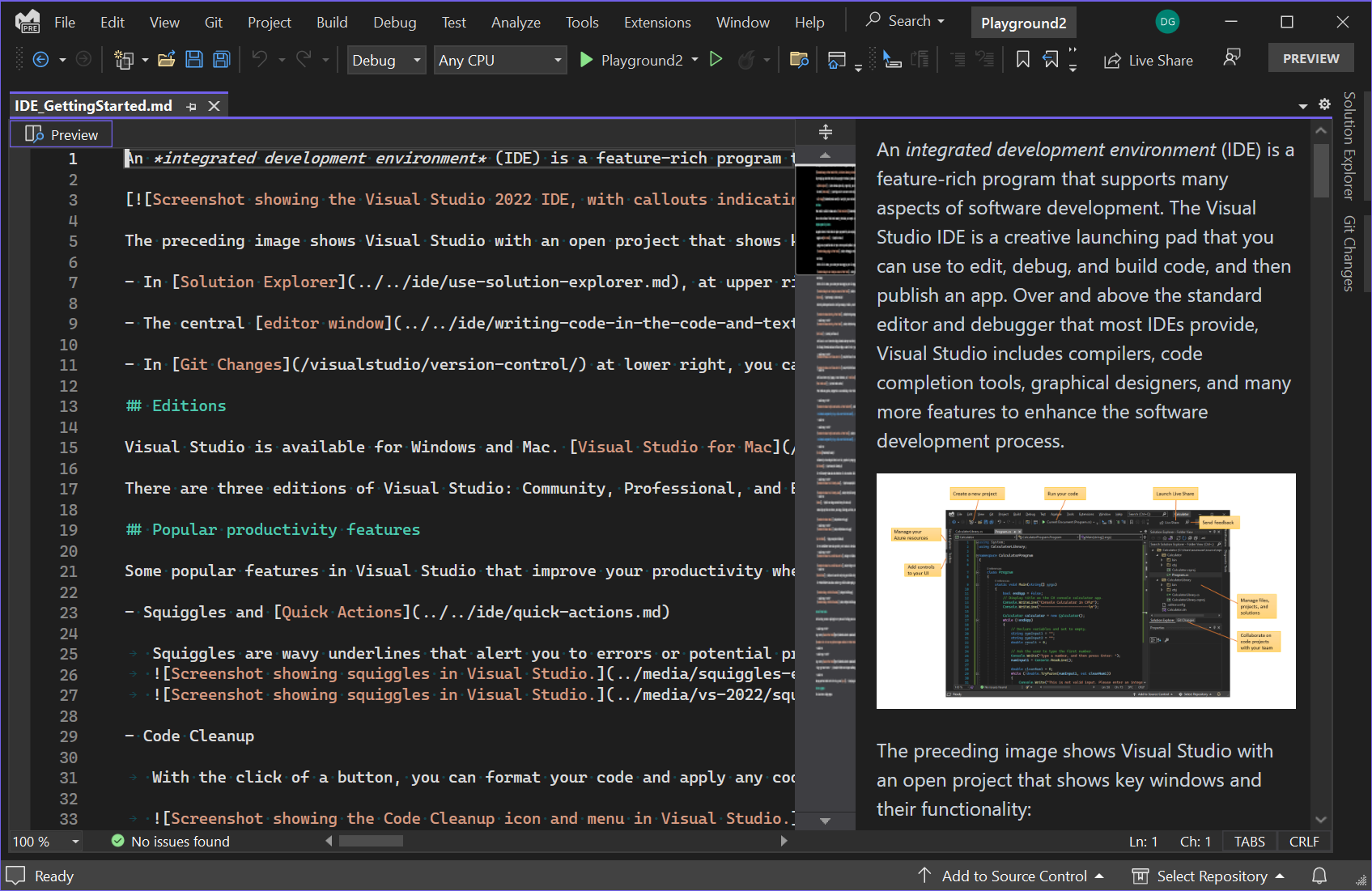

11、VS2022 17.5开始支持MarkDown格式编写

https://devblogs.microsoft.com/visualstudio/write-markdown-without-leaving-visual-studio/

这个功能更新很有意义,不需要再安装个别的软件做MD文件编写更新了。

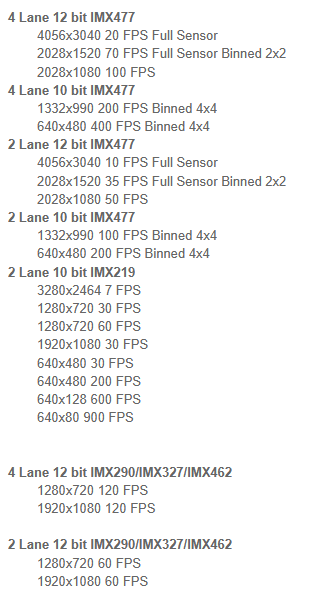

12、开源的C口镜头USB工业相机

https://www.circuitvalley.com/2022/06/pensource-usb-c-industrial-camera-c-mount-fpga-imx-mipi-usb-3-crosslinknx.html

https://github.com/circuitvalley/USB_C_Industrial_Camera_FPGA_USB3

效果

作者在自己的帖子里面进行了详细的设计介绍,当前测试的摄像头传感器如下:

13、H7-TOOL本周进展

H7-TOOL详细介绍:https://www.armbbs.cn/forum.php?mod=viewthread&tid=89934

(1)添加新的脱机烧录芯片支持

(2)H7-TOOL的RTOS Trace功能整理完毕FreeRTOS版就可以发布了,本周测试了以太网和WiFi接口方式

WiFi方式,测试1s刷新一次基本问题不大

以太网方式,可以250ms刷新

(3)纪念几套不断电的H7-TOOL第2轮测试已经整一年

两个测试贴,目的是长期开机不断电外网远程监控测试,以及意外断电后是否还可以正常启动,也方便我们测试下TOOL的耐操性。从而继续提升H7-TOOL的战斗力

https://www.armbbs.cn/forum.php?mod=viewthread&tid=108258

https://www.armbbs.cn/forum.php?mod=viewthread&tid=107825

这几套TOOL已经不断电测量两轮,第2轮测试已经整一年不断电,纪念下,分别测试了WiFi版和以太网版。

当时用的还是2.11版固件,等2.20版固件发布后,继续开启第3轮测试。

(4) H7-TOOL的CAN/CANFD助手实现SWD接口方式读取目标板CAN错误状态监测

近期做CAN/CANFD/CANopen专题视频教程,正好研究下这个实现。起初是打算采用这个功能(直接读取各个IC厂家提供的CMSIS SVD文件生成LUA程序,像MDK,IAR在线调试那样实时检测外设状态)实现,只是当前还没有好点的LUA转换方案。

方便起见,准备先手动整理了,直接通过HAL库的寄存器定义整理就行了,也非常方便。

#define FDCAN1_BASE (D2_APB1PERIPH_BASE + 0xA000UL) #define FDCAN2_BASE (D2_APB1PERIPH_BASE + 0xA400UL) #define FDCAN1 ((FDCAN_GlobalTypeDef *) FDCAN1_BASE) #define FDCAN2 ((FDCAN_GlobalTypeDef *) FDCAN2_BASE) #define FDCAN_CCU ((FDCAN_ClockCalibrationUnit_TypeDef *) FDCAN_CCU_BASE) /** * @brief FD Controller Area Network */ typedef struct { __IO uint32_t CREL; /*!< FDCAN Core Release register, Address offset: 0x000 */ __IO uint32_t ENDN; /*!< FDCAN Endian register, Address offset: 0x004 */ __IO uint32_t RESERVED1; /*!< Reserved, 0x008 */ __IO uint32_t DBTP; /*!< FDCAN Data Bit Timing & Prescaler register, Address offset: 0x00C */ __IO uint32_t TEST; /*!< FDCAN Test register, Address offset: 0x010 */ __IO uint32_t RWD; /*!< FDCAN RAM Watchdog register, Address offset: 0x014 */ __IO uint32_t CCCR; /*!< FDCAN CC Control register, Address offset: 0x018 */ __IO uint32_t NBTP; /*!< FDCAN Nominal Bit Timing & Prescaler register, Address offset: 0x01C */ __IO uint32_t TSCC; /*!< FDCAN Timestamp Counter Configuration register, Address offset: 0x020 */ __IO uint32_t TSCV; /*!< FDCAN Timestamp Counter Value register, Address offset: 0x024 */ __IO uint32_t TOCC; /*!< FDCAN Timeout Counter Configuration register, Address offset: 0x028 */ __IO uint32_t TOCV; /*!< FDCAN Timeout Counter Value register, Address offset: 0x02C */ __IO uint32_t RESERVED2[4]; /*!< Reserved, 0x030 - 0x03C */ __IO uint32_t ECR; /*!< FDCAN Error Counter register, Address offset: 0x040 */ __IO uint32_t PSR; /*!< FDCAN Protocol Status register, Address offset: 0x044 */ __IO uint32_t TDCR; /*!< FDCAN Transmitter Delay Compensation register, Address offset: 0x048 */ __IO uint32_t RESERVED3; /*!< Reserved, 0x04C */ __IO uint32_t IR; /*!< FDCAN Interrupt register, Address offset: 0x050 */ __IO uint32_t IE; /*!< FDCAN Interrupt Enable register, Address offset: 0x054 */ __IO uint32_t ILS; /*!< FDCAN Interrupt Line Select register, Address offset: 0x058 */ __IO uint32_t ILE; /*!< FDCAN Interrupt Line Enable register, Address offset: 0x05C */ __IO uint32_t RESERVED4[8]; /*!< Reserved, 0x060 - 0x07C */ __IO uint32_t GFC; /*!< FDCAN Global Filter Configuration register, Address offset: 0x080 */ __IO uint32_t SIDFC; /*!< FDCAN Standard ID Filter Configuration register, Address offset: 0x084 */ __IO uint32_t XIDFC; /*!< FDCAN Extended ID Filter Configuration register, Address offset: 0x088 */ __IO uint32_t RESERVED5; /*!< Reserved, 0x08C */ __IO uint32_t XIDAM; /*!< FDCAN Extended ID AND Mask register, Address offset: 0x090 */ __IO uint32_t HPMS; /*!< FDCAN High Priority Message Status register, Address offset: 0x094 */ __IO uint32_t NDAT1; /*!< FDCAN New Data 1 register, Address offset: 0x098 */ __IO uint32_t NDAT2; /*!< FDCAN New Data 2 register, Address offset: 0x09C */ __IO uint32_t RXF0C; /*!< FDCAN Rx FIFO 0 Configuration register, Address offset: 0x0A0 */ __IO uint32_t RXF0S; /*!< FDCAN Rx FIFO 0 Status register, Address offset: 0x0A4 */ __IO uint32_t RXF0A; /*!< FDCAN Rx FIFO 0 Acknowledge register, Address offset: 0x0A8 */ __IO uint32_t RXBC; /*!< FDCAN Rx Buffer Configuration register, Address offset: 0x0AC */ __IO uint32_t RXF1C; /*!< FDCAN Rx FIFO 1 Configuration register, Address offset: 0x0B0 */ __IO uint32_t RXF1S; /*!< FDCAN Rx FIFO 1 Status register, Address offset: 0x0B4 */ __IO uint32_t RXF1A; /*!< FDCAN Rx FIFO 1 Acknowledge register, Address offset: 0x0B8 */ __IO uint32_t RXESC; /*!< FDCAN Rx Buffer/FIFO Element Size Configuration register, Address offset: 0x0BC */ __IO uint32_t TXBC; /*!< FDCAN Tx Buffer Configuration register, Address offset: 0x0C0 */ __IO uint32_t TXFQS; /*!< FDCAN Tx FIFO/Queue Status register, Address offset: 0x0C4 */ __IO uint32_t TXESC; /*!< FDCAN Tx Buffer Element Size Configuration register, Address offset: 0x0C8 */ __IO uint32_t TXBRP; /*!< FDCAN Tx Buffer Request Pending register, Address offset: 0x0CC */ __IO uint32_t TXBAR; /*!< FDCAN Tx Buffer Add Request register, Address offset: 0x0D0 */ __IO uint32_t TXBCR; /*!< FDCAN Tx Buffer Cancellation Request register, Address offset: 0x0D4 */ __IO uint32_t TXBTO; /*!< FDCAN Tx Buffer Transmission Occurred register, Address offset: 0x0D8 */ __IO uint32_t TXBCF; /*!< FDCAN Tx Buffer Cancellation Finished register, Address offset: 0x0DC */ __IO uint32_t TXBTIE; /*!< FDCAN Tx Buffer Transmission Interrupt Enable register, Address offset: 0x0E0 */ __IO uint32_t TXBCIE; /*!< FDCAN Tx Buffer Cancellation Finished Interrupt Enable register, Address offset: 0x0E4 */ __IO uint32_t RESERVED6[2]; /*!< Reserved, 0x0E8 - 0x0EC */ __IO uint32_t TXEFC; /*!< FDCAN Tx Event FIFO Configuration register, Address offset: 0x0F0 */ __IO uint32_t TXEFS; /*!< FDCAN Tx Event FIFO Status register, Address offset: 0x0F4 */ __IO uint32_t TXEFA; /*!< FDCAN Tx Event FIFO Acknowledge register, Address offset: 0x0F8 */ __IO uint32_t RESERVED7; /*!< Reserved, 0x0FC */ } FDCAN_GlobalTypeDef;

浙公网安备 33010602011771号

浙公网安备 33010602011771号