80486微处理器引脚图

80486微处理器引脚图:

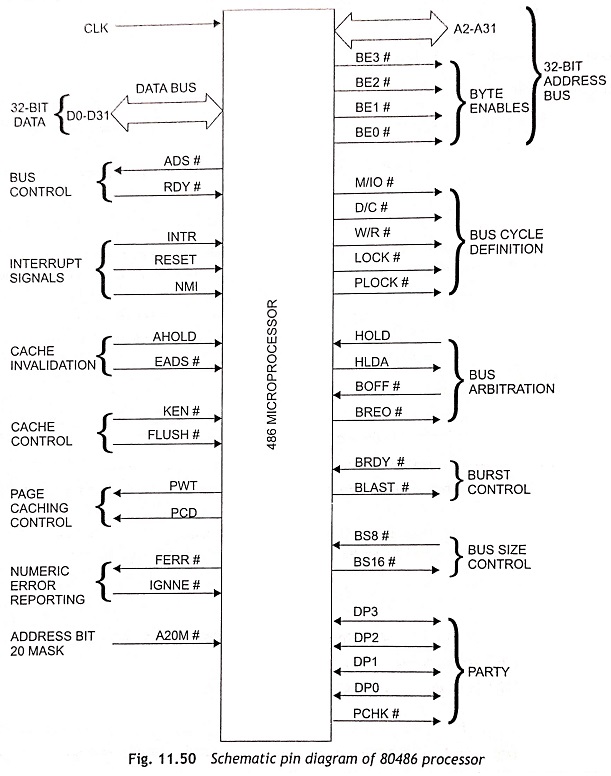

168 引脚 PGA(引脚网格阵列)封装 80486 的引脚图如图 11.49 所示,80486 微处理器的引脚示意图如图 11.50 所示。80486 的所有信号都按功能分组。本节解释了一些最重要的信号组。在今天也有些现实的参考和理解意义。

pin(引脚)视图

CLK: CLK 输入信号为 80486 的操作提供时序。

地址总线

A31 - A2 地址线 : A31 -A2 用于选择存储器和I/O设备。

B̅E̅ 3 - B̅E̅ 0 : 对于存储器和 I/O 寻址,需要字节使能信号 B̅E̅3 - B̅E̅0 。当字节使能信号B̅E̅3 -B̅E̅0为低电平有效时,这些信号指示 32 位数据总线的哪个字节在读取或写入周期中处于活动状态。例如,当 B̅E̅0 = 0 时,最低有效字节有效。同理,如果 B̅E̅ 3 = 0,则访问 32 位数据中的最高有效字节。

数据总线

D31 -D0 : 数据线D31 -D0 是双向数据总线。D31是最高有效数据位,D0是最低有效数据位。

Data Parity Group 这些引脚用于检测存储器读写操作期间的奇偶校验。

DP3-DP0四个数据校验输入/输出引脚为DP3 -DP 0。这些 80486 微处理器的引脚图用于表示数据总线的 32 位(4 字节)的各个奇偶校验。

总线周期定义组

M/I̅O̅ M/I̅O̅ 输出引脚用于区分存储器和 I/O 操作。

W/R̅ W/R̅ 输出引脚用于区分读取和写入总线周期。

D/C̅:此输出引脚可用于区分数据和控制操作。

L̅O̅C̅K̅此输出引脚用于声明当前总线周期被锁定。

P̅L̅O̅C̅K̅ P̅L̅O̅C̅K̅(伪锁定)输出引脚表示当前操作需要一个以上的总线周期才能完成任务。对于算术协处理器操作,该信号处于逻辑电平 0。

总线控制组

A̅D̅S̅ A̅D̅S̅(地址数据选通)输出引脚指示地址总线包含有效的存储器地址。

R̅D̅Y̅ R̅D̅Y̅(就绪)输入引脚用作就绪信号,该信号用于当前非突发周期。

突发控制组

B̅R̅D̅Y̅ B̅R̅D̅Y̅(突发就绪)输入引脚指示存储器读取或存储器操作的突发模式。在突发模式下,与正常的内存读/写操作相比,内存访问的速度可能会提高一倍。

B̅L̅A̅S̅T̅当B̅L̅A̅S̅T̅(burst last)输出信号为高电平时,表示CPU启动burst模式内存访问。如果此信号为低电平,则表示突发总线周期已完成,B̅R̅D̅Y̅ 信号接下来将被置位以开始下一个存储器访问操作。

总线仲裁组

HOLD HOLD 引脚用作本地总线保持输入。该引脚可以由另一个总线主控器(如 DMA 控制器)激活。该引脚在功能上类似于 BREQ 引脚。

HLDA HLDA 输出信号用于确认收到有效的 HOLD 请求。

BREQ当 BREQ(总线请求)输出信号为高电平有效时,表示 80486 CPU 产生了一个内部总线请求。

B̅O̅F̅F̅当 B̅O̅F̅F̅(回退)输入引脚处于逻辑电平 1 时,80486 CPU 将其总线置于保持状态。高电平有效回退输入信号强制 80486 CPU 的当前总线主机在下一个时钟周期释放总线。

中断

INTR INTR 引脚是可屏蔽中断输入。它由标志寄存器中的 IF 控制。

NMI这是 2 类不可屏蔽中断输入。

RESET RESET 输入引脚用于在其变为高电平时复位处理器。

缓存控制组

K̅E̅N̅ K̅E̅N̅(缓存启用)输入引脚用于决定当前周期是否可缓存。

F̅L̅U̅S̅H̅ F̅L̅U̅S̅H̅是缓存刷新输入信号。当此引脚被激活时,它会清除缓存内容和有效位。

缓存失效组

AHOLD AHOLD(地址保持请求)输入信号使其他总线主机能够使用 80486 系统总线进行高速缓存失效周期。

E̅A̅D̅S̅ E̅A̅D̅S̅(外部地址)输入信号用于指示地址总线上可获得外部总线周期的有效地址。

页面缓存能力组

PCD PCD(page cache disable)输出引脚反映了页表或页目录项中PCD属性位的状态。

PWT PWT(页面直写)输出引脚指示页表或页目录条目中 PWT 属性位的状态。

总线大小控制组

B̅S̅8̅ B̅S̅8̅(总线大小 8)输入引脚用于 80486 的 8 位动态总线大小调整功能,80486 可以与 8 位外部设备连接。

B̅S̅1̅6̅ B̅S̅1̅6̅(总线大小 16)输入引脚用于 80486 的 16 位动态总线大小调整功能,80486 可以与 16 位外部设备连接。

A̅2̅0̅M̅当 A̅2̅0̅M̅(地址位 20 掩码)输入引脚被激活时,80486 在执行任何存储器或缓存周期之前掩码物理地址线 A20。这对于将物理地址空间从 00FFFFH 包装到 000000H 非常有用,就像 8086 微处理器所做的那样,它工作在 1 MB 内存大小附近。即虚拟8086模式下8086的物理内存空间。

FPU 错误组

FERR当浮点单元产生任何错误时,FERR 输出信号被激活。

IGNNE当 IGNNE(忽略数字处理器扩展)输入引脚被激活时,80486 忽略浮动处理器(FPU)错误并连续执行非控制浮点指令。

测试接入端口组测试接入是一个独特的设施,在50 MHz 版本80486 中可用。测试接入信号用于检查主板上元件的故障情况。

TDI 80486 的 TDI(测试数据)输入是串行输入引脚,用于将 JTAG 指令和数据转移到组件中。

TCK TCK(测试时钟)输入提供边界测试功能所需的基本时钟信号。

TDO TDO(测试数据输出)引脚是串行输出引脚,用于将 JTAG 指令和数据移出被测组件。

TMS TMS(测试模式选择)输入由 JTAG TAP(tap 访问端口)解码,以选择此测试逻辑的操作。

补给线

V CC V CC引脚连接到+5 V电源。80486 处理器中有 24 V CC引脚。地线

https://www.eeeguide.com/pin-diagram-of-80486-microprocessor/

https://sunilbhagwat24.blogspot.com/2020/06/pin-layout-of-intel-486-microprocessor.html

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· DeepSeek 开源周回顾「GitHub 热点速览」

· 物流快递公司核心技术能力-地址解析分单基础技术分享

· .NET 10首个预览版发布:重大改进与新特性概览!

· AI与.NET技术实操系列(二):开始使用ML.NET

· 单线程的Redis速度为什么快?