什么是内存解码?

https://www.geeksforgeeks.org/what-is-memory-decoding/

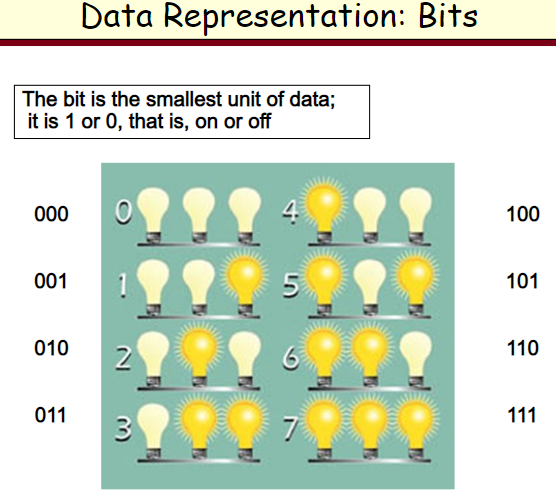

数据代表位,下面图就比较形象:(on 开启、off关闭)

数字电子电路是一种只处理两种状态信号的电路:0或1。电路中的晶体管用于执行各种布尔逻辑。

在数字电子产品中,当需要访问数字设备中的内存时,就会发生内存解码过程。在此过程中,生成二进制地址,以在系统中找到所需的内存。结果,在内存地址的帮助下,创建的内存单元可以找到请求的数据。这个过程包括多个步骤,我们必须遵循这些步骤才能找到确切的内存。

一、什么是内存?

计算机存储器可分为内部存储器或外部存储器。内部存储器是处理器可以通过系统总线直接访问的存储器,外部存储器是通过计算机的输入输出通道访问的。

内部存储器也称为计算机的主存储器或主存储器。内部存储器用于保存当前正在执行的指令或数据。

计算机的内部存储器由通常为硅的半导体材料制成。与外部存储器相比,这种存储器成本更高,而且通常尺寸较小。

在我们之前的内容中,半导体 RAM 存储器,我们讨论了半导体主存储器的内部组织,其中存储器的基本元素是存储单元。

尽管有不同的技术来构建半导体主存储器或内部存储器,但所有半导体单元都有一些共同的特性,如下所述:

- 每个存储单元都有两种状态,分别代表二进制 0 和 1。

- 可以读取每个存储单元以感知它所代表的状态。

- 可以写入每个存储单元以将其设置为特定状态,即 0 或 1。

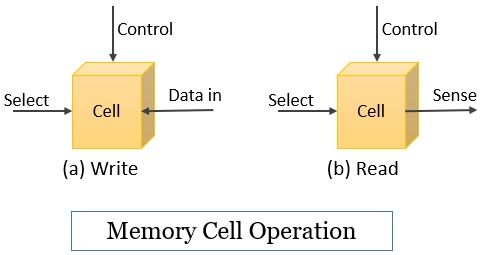

每个存储单元都有访问选择、控制和读/写三行。选择线指示特定存储单元是否已被选择用于读/写操作。控制线表示是读操作还是写操作。

为了写入单元,电信号通过读/写线传递,将单元的状态设置为 0 或 1。在读取时,相同的读/写线用于输出单元状态。

二、内存类型

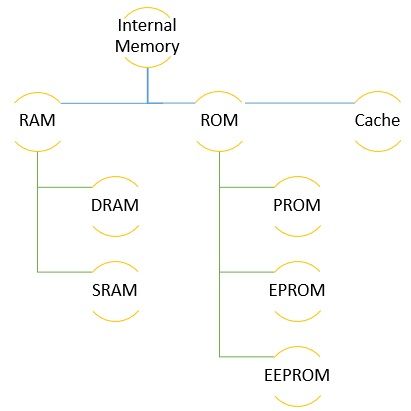

首先我们需要知道内存有哪些种类, 计算机的内部存储器可分为 RAM、ROM 和高速缓冲存储器。

下面分别来介绍,注意这些内存类型也是我们实际工作中会遇到的。

1、 随机存取存储器 (RAM)

RAM 内存是最快的,但它是易失性内存。这意味着要保留其内容,必须为 RAM 存储器提供恒定的电源。一旦这个存储芯片的电源被关闭,这个存储芯片就会丢失它的所有内容。

从 RAM 存储器读取数据和将数据写入 RAM 存储器很容易。使用电信号将数据读取或写入 RAM 存储器。此外,RAM存储器还有另外两种形式DRAM和SRAM。

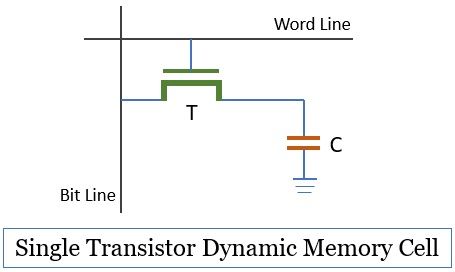

1)、在动态 RAM (DRAM)中,存储单元格是使用电容器制成的。当电容器充电时,该存储单元格的值被视为 1,而当电容器放电时,该存储单元格的值被视为 0。这意味着已充电或未充电的电容器分别代表二进制 1 或 0。

一段时间后电容器会自动放电,因此要将数据保留在电容器中,它必须定期充电。

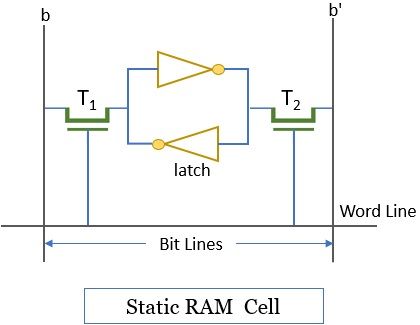

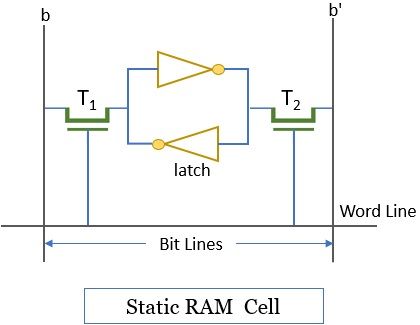

2)、在静态 RAM (SRAM)中,存储单元是使用两个交叉连接以形成锁存器的反相器实现的,而该锁存器又连接到连接到两个晶体管的两位线。在这里,晶体管充当一个开关,可以在字线的控制下关闭和打开。

存储单元的晶体管被接通以对该特定存储单元执行读取和写入操作。好吧,这两种形式的 RAM 都是易失性的,需要持续供电才能保持其位值。

2、ROM

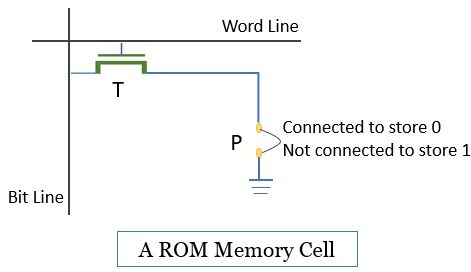

只读存储器 (ROM) 是一种非易失性存储器,这意味着该内存存储芯片的存储单元格不需要电源来保持其位值。由于这是一个只读存储器,因此只能读取该存储器的位值,而不能写入或修改。

下图显示了 ROM 存储单元的结构,如果晶体管处于地电平,则存储单元的位值为 0,否则为 1。

位线通过电阻连接到电源。为了读取存储单元的值,激活将晶体管连接到地的字线。如果晶体管接地,这会将位线的电压降至 0。如果晶体管和地之间没有连接,则位线保持高电压,指示 1。存储单元在接地连接处的状态在芯片制造期间定义。

ROM存储器可用于微程序,如存储库子程序、系统程序、函数表等。这种内部存储器的优点是所需的数据或程序始终存在于内部主存储器中,而不需要像 RAM 那样从任何辅助存储器加载数据。

在ROM内存芯片(也叫存储芯片)上,数据或程序是在芯片制造过程中嵌入的,因此无论您是制造单个副本还是多个副本,都会导致很大的固定成本。甚至连一个位的错误都没有余地,因为它会毁掉整批 ROM。

与RAM一样,ROM也有可编程ROM、可擦可编程ROM、电可擦可编程ROM、闪存等其他形式。

当特定内存内容需要少量 ROM 时,使用可编程 ROM (PROM ) 。PROM 只能使用电信号写入一次。

可以使用电信号读取和写入可擦除可编程只读存储器(EPROM )。在执行写操作之前,通过将存储芯片暴露在紫外线下,该存储芯片的存储内容被擦除以恢复其初始状态。

EPROM 可以重复擦除和更新,与 ROM 和 PROM 一样,即使没有电源,它也能保留其存储内容。与 ROM 和 PRM 相比,EPROM 更昂贵。

电可擦除可编程只读存储器(EEPROM)是可以选择性擦除和多次写入的ROM存储器。与 EPROM 不同,当暴露在紫外线下时,整个数据都会被擦除。

在 EEPROM 中,可以在不从系统中移除存储芯片的情况下擦除选择性数据,因为使用高于正常电压的数据将被擦除。与 EPROM 相比,EEPROM 有点复杂,因为它需要不同的电压来擦除数据。

闪存 在功能和成本方面介于 EPROM 和 EEPROM 之间。在闪存中,可以写入整个单元块。在写入闪存之前,必须擦除单元块,这与执行字节级擦除的 EEPROM 不同。闪存的擦除速度更快。

3、cache(高速缓存存储器)

高速缓冲存储器是一种易失性存储器,一旦存储器单元的电源中断,它就会丢失其存储器内容。高速缓冲存储器保留主存储器中最近访问的信息的副本。

每当再次需要相同的信息时,就会从高速缓存中访问它,从而提高系统的性能。高速缓冲存储器以这种方式存储经常使用的信息。缓存内存比 RAM 内存更快、更昂贵且更小。

因此,这些是计算机的内部存储器,比外部存储器更快、更小、更昂贵。通常,计算机的内部存储器由半导体材料制成,具有加速访问存储器内容的技术。

三、内存芯片的内部构造

在这篇文章中,我们将讨论静态 RAM (SRAM)内存芯片的内部构造、解码过程以及内存解码过程中发生的不同组件。

注意: 不同内存类型,内部构造原理有一定的差异。

内存的内部构造(二维阵列):

在内部结构中,二进制存储单元格和相关的用于选择单个字的解码机制构成了具有m个word和每个字n bit 的随机存取内存的内部结构。 在内存单元中,基本构建块是二进制单元格。

在内存单元格中,可以轻松存储一位(0/1)信息。内存芯片由排列成矩阵的多个单元格组成。

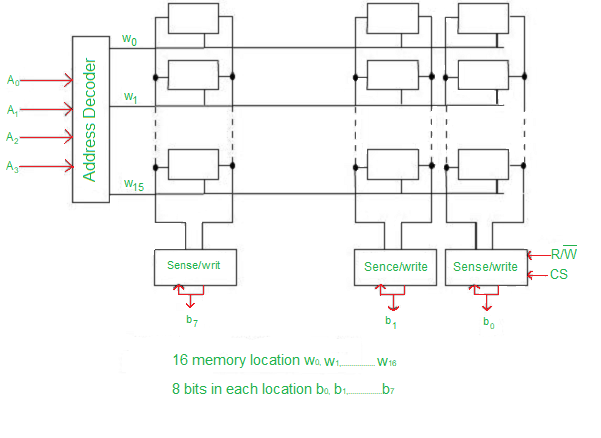

每行(row)的单元格(cells)生成一个存储字(memory word),每行单元格连接到一条公共线,也称为字线(word line)。字线(word line)由地址译码器控制。根据地址总线中存在的地址,单字线(one-word line )随时被激活。每列的单元格之间有两条线。这些就是所谓的位线(Bit lines)。感测/写入电路将这些位线(Bit lines)连接到数据输入和数据输出线。感测/写入或读取字线(word line)指定的单元中包含的信息,并在读取操作期间将其传输到输出数据线。感测/写入电路在写入操作期间获取信息。

要了解内存芯片(memory chip)的内部结构,可以看下图:

内存的内部构造

内存解码过程:

内存解码过程是一个多步骤过程,其中使用许多地址来标识特定的内存位置。发生了内存解码,其中需要访问数字电子设备中存储的内存。在下面的过程中。

需要内存解码器从内存单元格中选择内存指定的输入地址。在这里,内存在这个过程中起着至关重要的作用。

内存单元格:

内存单元格是内存基本构成单位,内存单元格是一种电路,包含四到六个晶体管。

1、读操作

选定的输入使单元格可以轻松处理读/写操作。在此过程中,通过创建从锁存器(latch )到输出端的line,读/写输入的 A 1执行读操作。

2、写操作

并且另一方面,通过构造从输入端到锁存器的路径,读写中的A 0可以进行写操作。

RAM cell 如下图所示。

至于单元的构造,通常,内存单元格能够以不同的单元格存储二进制信号,这些单元格被称为位。最初,一位等于 8 位,一个word有 2 位的值。数据输入和输出线通过读/写操作在存储器之间进行通信。最初,它有助于确定信息的传输。在内存中,每个word都有一个编号,称为地址。这些地址的范围从 0 到 2k-1。这里,k指的是地址行号( address line number)。

通常,小型 RAM(也被叫主存) 由四个word组成,每个字有四位,总共有 16 个二进制单元格。二进制单元格以及三个输入和一个输出代表小块的单元格 (BC)。在这里,用户需要两条地址线用于四个内存word。要从四个word中选择一个,地址输入需要通过一个 2:4 解码器,它可以通过内存使能输入来启用。

在这个过程中更进一步,在内存启用值为0的情况下,解码器中的所有输出都变为0,并且没有一个被选中。如果内存选择值为 1,则将选择 4 个字中的 1 个。

读/写操作:在这里,在选择字之后,读/写输入通过操作进行。在读操作过程中,被选中字的四位通过或门到达输出端。

另一方面,在写操作中,输入线中的可用数据被传输到所选字的四个二进制单元中。在此过程中,未选中的单元格变为虚拟单元格,并且它们的值保持不变。

内存地址解码:

在随机存取存储器中,有一个空闲空间,可以使用数千个字地址。每个内存字都有一个值,范围从 1 到 64 位。这里,2k 字以内的内存使用 k 条内存地址线,每个内存字有 n 位。解码器由 2k 个内存地址组成,其中每个解码地址输出标识一个 n 位字以供进一步读取或写入。

这里地址线代表数据输入,称为代码,输出代表字信号,可以是高电平也可以是低电平。在 PC 和微处理器中,有一个定位的存储芯片,每个芯片都有一个选定的输入。现在,要选择,需要指定存储芯片。

单芯片同时选择和操作时。它允许用户为某个内存地址位置选择正确的内存地址编码设备。

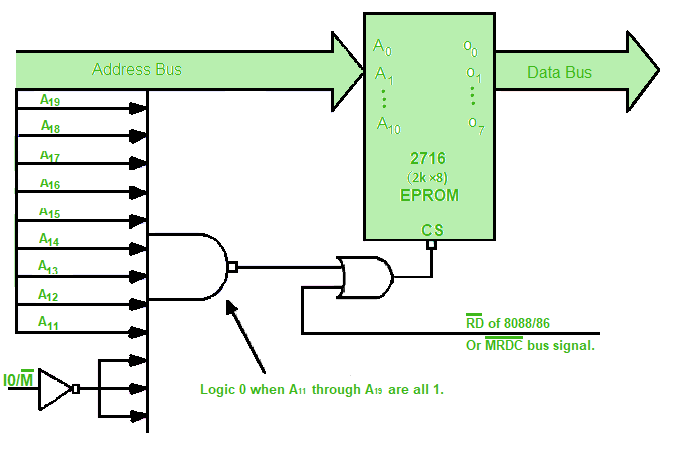

示例:现在我们以 8088 为例,它为 1MB 内存地址空间创建 20 位地址作为输出。另一方面,EPROM BIOS 2716 只有 2KB 内存和 11 个地址引脚。现在,这里的 EPROM 可以放在 1MB 地址空间的任何 2KB 部分,因为这里的解码器可以解码额外的 9 个地址引脚。

这可以借助下图来理解:

记忆译码电路

重合解码:

在同步解码中,具有 k 个输入的解码器创建具有 2k 个值的输出。这种类型的解码器需要 2k 个与门,以及每个门的 k 个输入。在这里,通过将两个解码器组合成一个二维方案,可以减少门的总数和每个门的输入。

此外,在二维矩阵方法中,一个解码器用于行选择,另一个用于列选择。在这种情况下,使用两个 2k 输入而不是一个 k 输入。

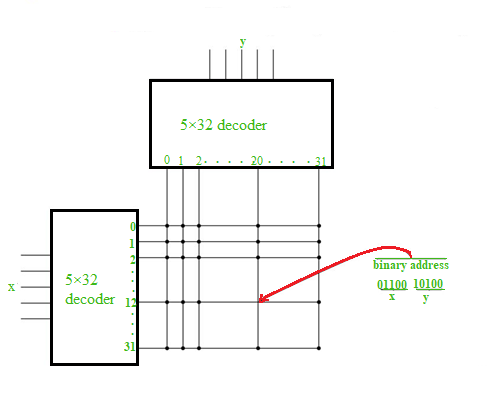

这可以借助下图来理解:

1k 字内存的二维解码结构

例:这里,1K 字内存的选择方法不是使用 10 x 1,024 解码器,而是可以选择两个 5 x 32 解码器。我们需要 1,024 个与门,每个解码器中有 10 个输入。

在两个解码器的情况下,我们需要 64 个与门,每个有五个输入。前五个最高有效位分配给输入 X,最后五个最低有效位分配给输入 Y。存储器阵列中的每个字都被选择为一个 X 行和一个 Y 输入的重合结果。

结果,内存中的单个单词由 32 行中的 1 和 1 或 32 列之间的重合因子选择,总共将近 1,024 个单词。在特定行和列的交叉点找到所需的词。之后,读取/写入所有需要的字位。

地址复用:

地址多路复用允许用户使用较少的引脚,因此,使用处理器上的几条总线。可以将地址放在数据线上,而不是为地址和数据设置单独的总线,其中读取数据并将其保存在先前读取的地址处。

具体来说,SRAM 或静态随机存取存储器中有六个晶体管。当晶体管的尺寸较小时,就会创建高密度存储单元。

DRAM 或动态随机存取存储器,还包括一个晶体管,使其具有比 SRAM 更大的存储容量。SRAM 数据存储比 DRAM 数据存储更昂贵。DRAM 更节能。

因为DRAM的字位大小是一个,所以需要多个芯片。主要是因为容量增加了;所有DRAM位的解码都是在一个二维数组中进行的,如果一个cell中的内存数据较多,则需要多个数组。设计人员使用地址多路复用来减少集成电路中的引脚数量。

在这里,地址被分成两部分,用于二维数组中不同的时间组。首先列出行的地址,然后列出列的地址。由于内存地址的两侧使用了相同的引脚集,因此总大小有意减小。

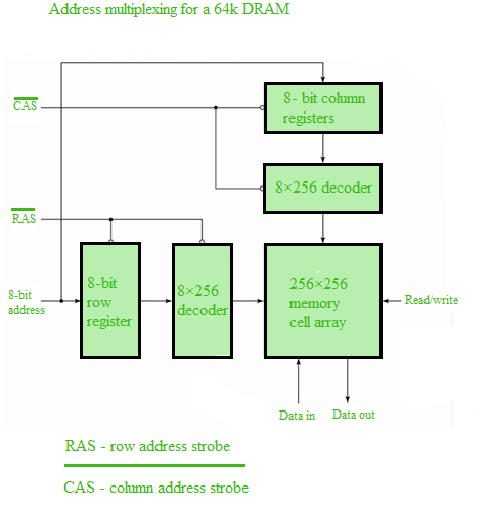

例:在多路复用中,需要一个 64K 字的存储器。二维单元阵列被组织成 256 行和 256 列,然后构成内存地址。这给出了总共 64K 字的存储器。有两个地址选通、一个数据输入线、一个数据输出线、一个具有八位地址输入的读/写控制和一个数据输入线。行地址选通缩写为 RAS,它激活八位内存行寄存器。列地址选通被截断,因为 CAS 启用 8 位列寄存器。选通符号顶部有一个条,表示寄存器为空或处于信号的零电平。

这可以通过下图来理解:

地址复用示意图

到目前为止,我们已经介绍了内部构造和内存解码过程,以及本文中解码的不同方面。最后,我们可以说内存解码是访问数字电子电路内存的一个重要但基本的方面。

参考:

https://www.geeksforgeeks.org/what-is-memory-decoding/

https://www.ques10.com/p/39305/explain-dram-operation-1/

http://www.cs.emory.edu/~cheung/Courses/170/Syllabus/01/binary.html

https://courses.cs.vt.edu/csonline/MachineArchitecture/Lessons/DataStorage/index.html

https://binaryterms.com/internal-memory-in-computer-architecture.html

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· 阿里巴巴 QwQ-32B真的超越了 DeepSeek R-1吗?

· 【译】Visual Studio 中新的强大生产力特性

· 【设计模式】告别冗长if-else语句:使用策略模式优化代码结构

· AI与.NET技术实操系列(六):基于图像分类模型对图像进行分类