VSCODE自定义代码风格

VSCode启用代码风格修正

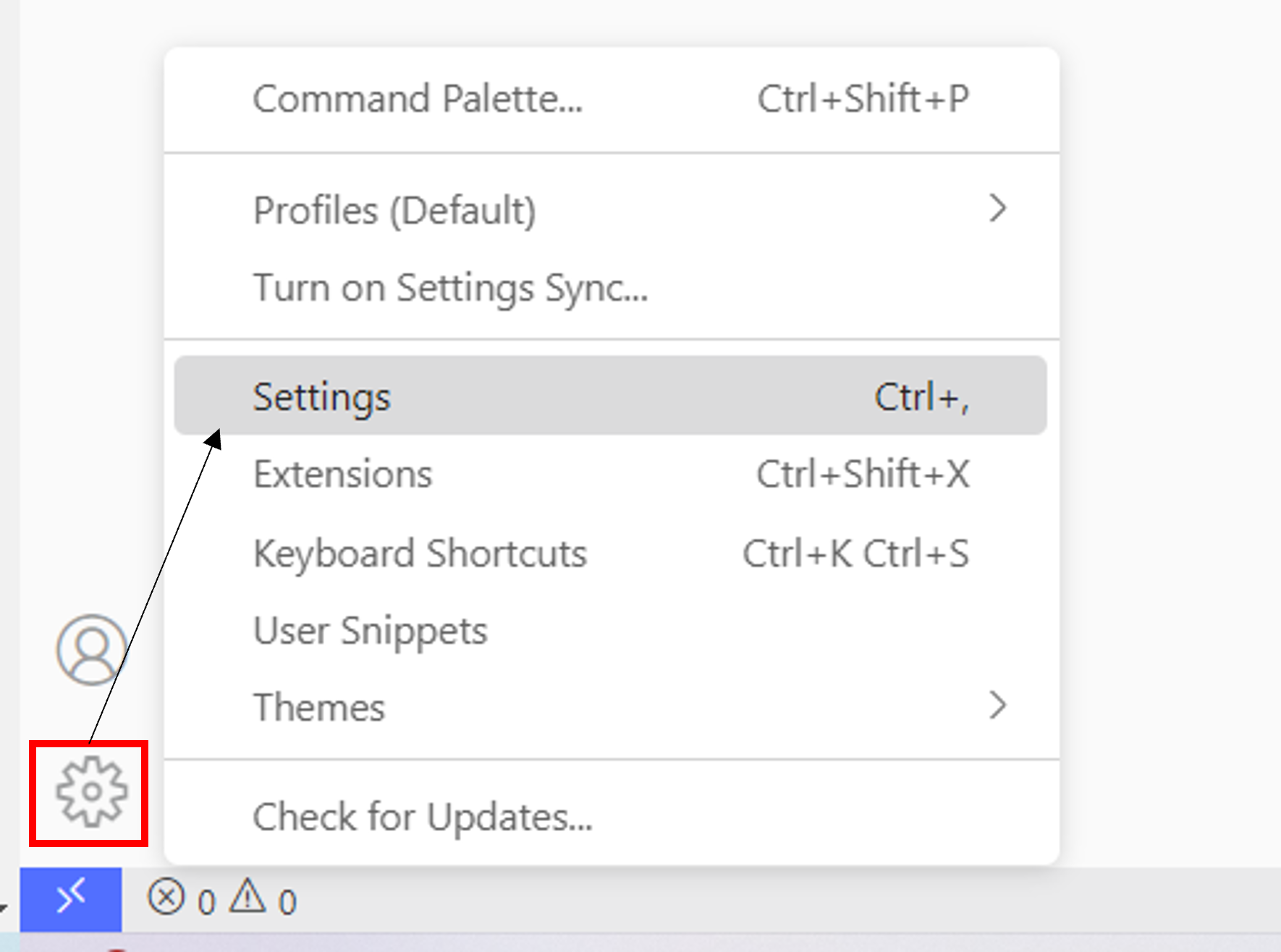

1.打开Settings

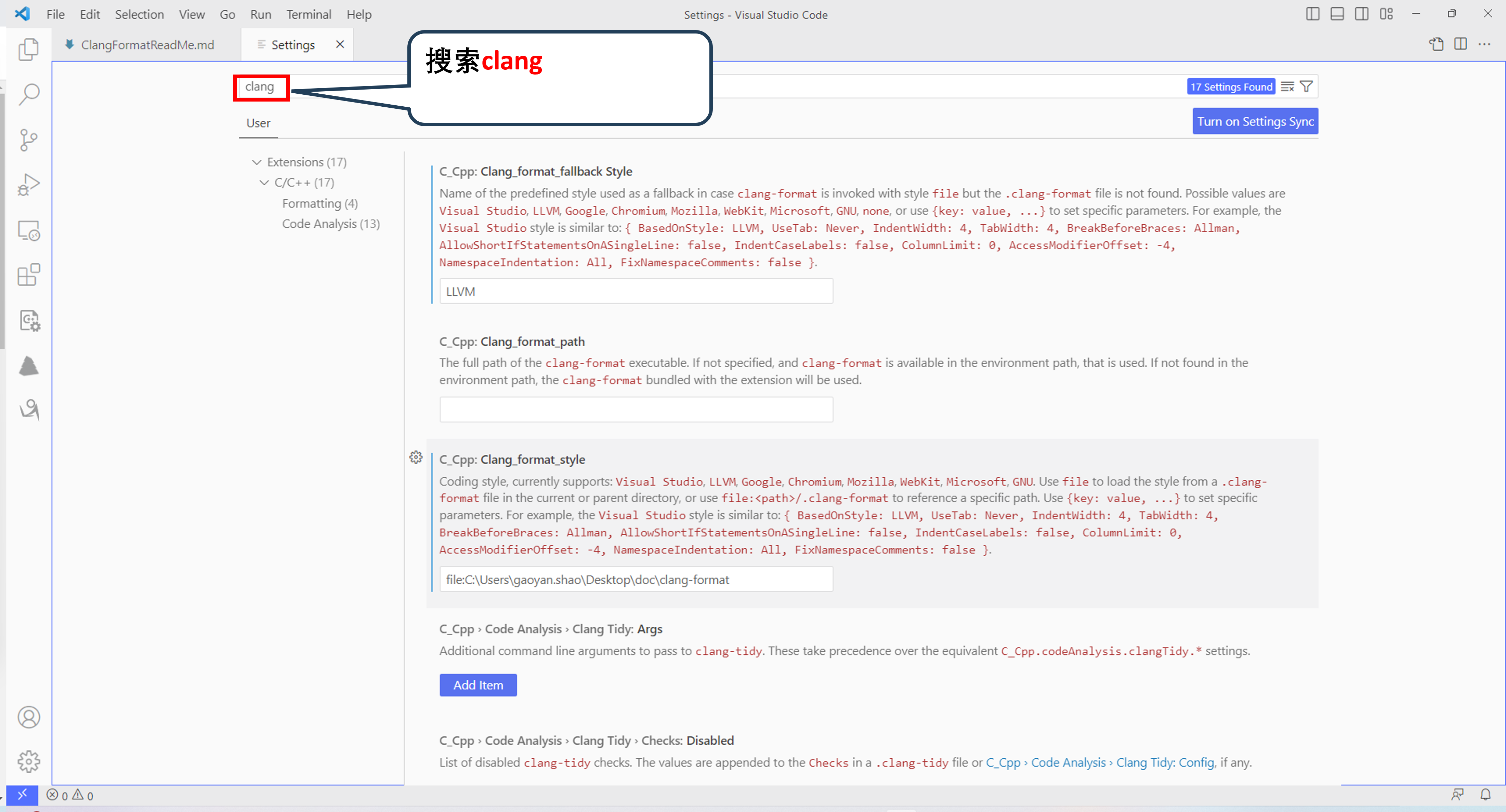

2.设置Clang_format

搜索clang_format相关配置

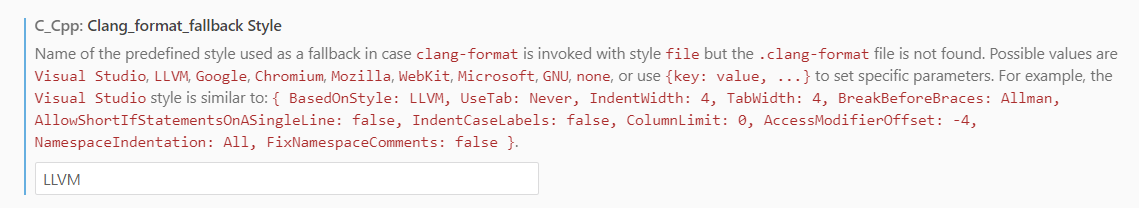

设定clang_format基础风格

基础风格中LLVM与Google都是缩进为2,所以还需要自定义风格。

设定clang_format自定义风格文件的路径

指定自定义分割文件的路径(XXX\.clang-format)。自定义风格可以参考后续章节

clang-format文件编写

Clang-format格式化及配置参数(说明)

https://blog.csdn.net/Once_day/article/details/127761573

Clang-format格式化及配置参数(效果展现)

调整为自己的想要的个时候可以导出文件,将文件所在路径填入VSCode,即可完成定制。

https://zed0.co.uk/clang-format-configurator/

VSCode使用效果

windows: Shift+Alt+F

Linux: Ctrl+Shift+I

调整前

euint32 Fpga_MdioWrite(euint8 uchSlotSel, euint16 DevAddr, euint16 regAdrr, euint16 eushData)

{

euint32 ulRet = 0;

volatile euint32 i = 0;

euint32 ulMdioCtrl = 0;

euint32 ulMdioPhyAddr = 0;

euint32 ulMdioWrData = 0;

euint32 ulMdioRdData = 0;

euint32 ulMdioIndAddr = 0;

euint32 ulMdioRst = 0;

euint32 ulRegCtrlVal=0;

euint16 phyDevAddr = 0;

euint8 mdioMode = 0;

ulRet = Fpga_MdioSel(uchSlotSel, &phyDevAddr, &mdioMode);

if(FPGA_ERR_SUCCESS != ulRet)

{

return FPGA_ERR_PARA;

}

ulRet |= Fpga_MdioAddrSel(uchSlotSel, &ulMdioCtrl, &ulMdioPhyAddr, &ulMdioWrData, &ulMdioRdData, &ulMdioIndAddr, &ulMdioRst);

if(FPGA_ERR_SUCCESS != ulRet)

{

return FPGA_ERR_PARA;

}

//优化MDIO驱动,Fpga write时使用非掩码写,节省掩码读时的回读步骤,节省MDIO读写时间

Fpga_Write_Reg_No_Mask(ulMdioPhyAddr, phyDevAddr&0x7f);

if (FPGA_MDIO_CLAUSE22 == mdioMode)

{

ulRegCtrlVal=regAdrr&0x1f;

Fpga_Write_Reg_No_Mask(ulMdioCtrl, ulRegCtrlVal);

}

else

{

ulRegCtrlVal=BIT(10)|(DevAddr&0x1f);

Fpga_Write_Reg_No_Mask(ulMdioCtrl, ulRegCtrlVal);

Fpga_Write_Reg_No_Mask(ulMdioIndAddr, regAdrr&0xffff);

}

//write data

Fpga_Write_Reg_No_Mask(ulMdioWrData, eushData&0xffff);

for (i=0;i<800;i++)

{

//pclint

}

Fpga_Write_Reg_No_Mask(ulMdioCtrl, ulRegCtrlVal|BIT(15));//trigger

ulRet += Fpga_MdioBusy(uchSlotSel);

if (ulRet != FPGA_ERR_SUCCESS)

{

/* record log */

//printf("\n MDIO read faild, enter reset process \n");

Fpga_MdioInit(uchSlotSel);

return ulRet;

}

return ulRet;

}

调整后

euint32 Fpga_MdioWrite(euint8 uchSlotSel, euint16 DevAddr, euint16 regAdrr, euint16 eushData)

{

euint32 ulRet = 0;

volatile euint32 i = 0;

euint32 ulMdioCtrl = 0;

euint32 ulMdioPhyAddr = 0;

euint32 ulMdioWrData = 0;

euint32 ulMdioRdData = 0;

euint32 ulMdioIndAddr = 0;

euint32 ulMdioRst = 0;

euint32 ulRegCtrlVal = 0;

euint16 phyDevAddr = 0;

euint8 mdioMode = 0;

ulRet = Fpga_MdioSel(uchSlotSel, &phyDevAddr, &mdioMode);

if (FPGA_ERR_SUCCESS != ulRet) {

return FPGA_ERR_PARA;

}

ulRet |= Fpga_MdioAddrSel(uchSlotSel, &ulMdioCtrl, &ulMdioPhyAddr, &ulMdioWrData, &ulMdioRdData,

&ulMdioIndAddr, &ulMdioRst);

if (FPGA_ERR_SUCCESS != ulRet) {

return FPGA_ERR_PARA;

}

// 优化MDIO驱动,Fpga write时使用非掩码写,节省掩码读时的回读步骤,节省MDIO读写时间

Fpga_Write_Reg_No_Mask(ulMdioPhyAddr, phyDevAddr & 0x7f);

if (FPGA_MDIO_CLAUSE22 == mdioMode) {

ulRegCtrlVal = regAdrr & 0x1f;

Fpga_Write_Reg_No_Mask(ulMdioCtrl, ulRegCtrlVal);

} else {

ulRegCtrlVal = BIT(10) | (DevAddr & 0x1f);

Fpga_Write_Reg_No_Mask(ulMdioCtrl, ulRegCtrlVal);

Fpga_Write_Reg_No_Mask(ulMdioIndAddr, regAdrr & 0xffff);

}

// write data

Fpga_Write_Reg_No_Mask(ulMdioWrData, eushData & 0xffff);

for (i = 0; i < 800; i++) {

// pclint

}

Fpga_Write_Reg_No_Mask(ulMdioCtrl, ulRegCtrlVal | BIT(15)); // trigger

ulRet += Fpga_MdioBusy(uchSlotSel);

if (ulRet != FPGA_ERR_SUCCESS) {

/* record log */

// printf("\n MDIO read faild, enter reset process \n");

Fpga_MdioInit(uchSlotSel);

return ulRet;

}

return ulRet;

}

我目前使用的格式

BasedOnStyle: Google

AccessModifierOffset: '-4'

AlignAfterOpenBracket: Align

AlignConsecutiveMacros: 'true'

AlignConsecutiveAssignments: 'true'

AlignConsecutiveDeclarations: 'true'

AlignEscapedNewlines: Left

AlignTrailingComments: 'true'

AllowShortBlocksOnASingleLine: 'false'

AllowShortCaseLabelsOnASingleLine: 'false'

AllowShortFunctionsOnASingleLine: None

AllowShortIfStatementsOnASingleLine: Never

AllowShortLambdasOnASingleLine: None

AllowShortLoopsOnASingleLine: 'false'

AlwaysBreakAfterReturnType: None

BinPackArguments: 'true'

BinPackParameters: 'true'

BreakBeforeBraces: Linux

ColumnLimit: '110'

ContinuationIndentWidth: '4'

IndentCaseLabels: 'true'

IndentWidth: '4'

Language: Cpp

浙公网安备 33010602011771号

浙公网安备 33010602011771号