51上拉电阻(P1)的由来

目录

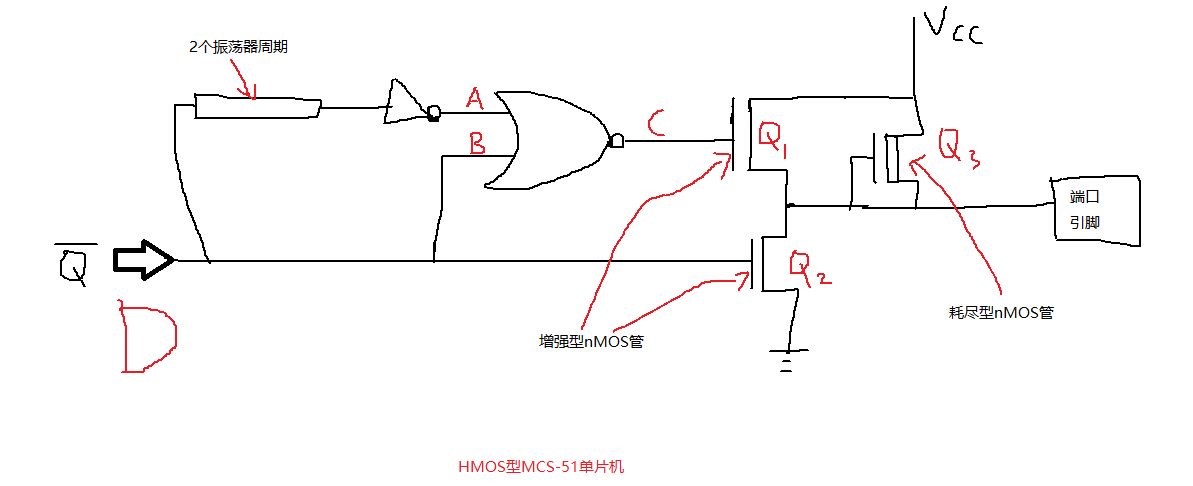

一、HMOS型MCS-51单片机P1口

(1)P1作为普通I/O发送0数据时

(2)P1作为普通I/O发送1数据时

(3)总结

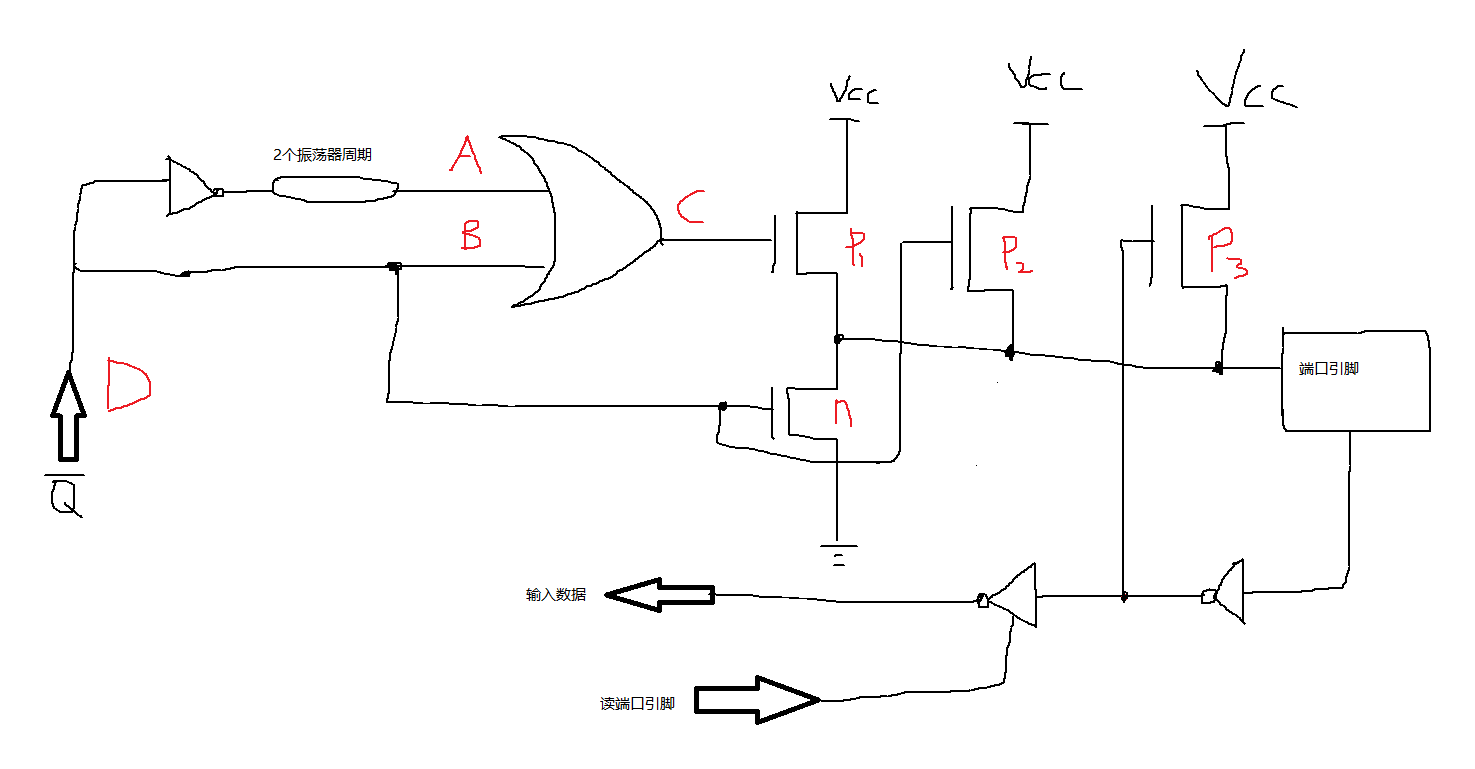

二、CHMOS型MCS-51单片机P1口

(1)P1作为普通I/O发送数据0时

(2)P1作为普通I/O发送数据1时

(3)P1作为普通I/O接收数据0

(4)P1作为普通I/O接收数据1

一、HMOS型MCS-51单片机P1口

Q1和Q2均为N型增强型MOS管,Vg-s>0时管子导通,Vg-s=0时管子截止,图中Q1源极串联Q2漏极。

Q3为耗尽型nMOS管,Vg-s>Voff (Voff 为夹断电压,小于0) ,管子导通,当Vg-s>=0时,Is>=Idss >0;

对于Is和Idss看不懂的小伙伴要补一补模电呀 嘻嘻。

(1)作为普通I/O发送0数据时:

当想往引脚外部发送数据0时,数据先到达锁存器使得锁存器 =1, 图中

=1, 图中

为D点处;这时Q2管导通,端口引脚被拉低接地,此时外部端口引脚即为输出0数据,跟内部想要发送的0数据一致;

Q3耗尽管nMOS的栅极与源极电平相等,也即电压差Vg-s=0,管子导通,但是源极接地了,所以对端口引脚没啥影响;

或非门输出点C处等于0(图中),使得Q1管截止;

(2)作为普通I/O发送1数据时:

当想往引脚外部发送数据1时, =0,Q2的栅极处迅速等于0,Q2截止;但是,由于延时线和反相器的影响,数据

=0,Q2的栅极处迅速等于0,Q2截止;但是,由于延时线和反相器的影响,数据 在2个震荡器周期内或非门的上端输入并没有刷新数据,A点保持上一次数据,即A=0,或非门的两输入端均为0使得或非门的输出点C=1;此时Q1管导通,Vcc迅速接到端口引脚,即此时端口引脚为1;

在2个震荡器周期内或非门的上端输入并没有刷新数据,A点保持上一次数据,即A=0,或非门的两输入端均为0使得或非门的输出点C=1;此时Q1管导通,Vcc迅速接到端口引脚,即此时端口引脚为1;

此时Q3管的栅极和源极电压差为0,Q3管导通,但由于Q2截止,Q1导通迅速从0提高Q1源极的电压到达VCC,Q3管此时也导通,端口引脚数据已经由0变为VCC;

等2个震荡器周期的时间过了之后,数据终于刷新了, =0的数据终于到达反相器,取反后输入到或非门,此时或非门的上端输入为1,下端输入为0,所以或非门输出点C=0,Q1截止,但是Q3的导通状态并没有停止,因为Q3的栅极电压并没有那么快下降,这使得Q3的栅极减去源极电压的压差仍然为VCC-VCC=0, 又因为Q3的源极又迅速源源不断补充Q3的栅极,所以Q1就算截止撤去,端口引脚仍然等于1; (这有点类似电流镜像的原理)

=0的数据终于到达反相器,取反后输入到或非门,此时或非门的上端输入为1,下端输入为0,所以或非门输出点C=0,Q1截止,但是Q3的导通状态并没有停止,因为Q3的栅极电压并没有那么快下降,这使得Q3的栅极减去源极电压的压差仍然为VCC-VCC=0, 又因为Q3的源极又迅速源源不断补充Q3的栅极,所以Q1就算截止撤去,端口引脚仍然等于1; (这有点类似电流镜像的原理)

由此,内部发送的数据1经过一系列流通后,端口引脚处也输出了1;

(3)总结:

从(2)看出,P1输出1时,外部的端口引脚并不需要人为加 上拉电阻 也具有输出1的能力,表明P1内部具有上拉功能,而内部上拉电阻就是Q3提供,为20KΩ~40KΩ

二、CHMOS型MCS-51单片机P1口

P1、P2、P3均为P沟道增强型MOS管,当正逻辑1加到P沟道增强型MOS管的栅极时,管子截止;记 P1、P2、P3为pFET1、pFET2、pFET3;

N为N沟道增强型MOS管,当正逻辑1加到N沟道增强型MOS管的栅极时,管子导通;记N为nFET;

(1)P1作为普通I/O发送数据0时:

设原始稳定状态下,端口上的数据为0,即端口引脚应该为0,那么内部稳定状态下的0数据在内部如何往外部引脚流通使得外部端口引脚也保持为0?

内部发送的0数据到达锁存器 变为1,即图中D=1,

变为1,即图中D=1,

nFET导通,pFET2截止,端口引脚短接到nFET的源级地,即端口引脚的数据为0;

端口引脚0经过反相器到达pFET3,此时pFET3的栅极变为1,pFET3截止;

=1经过反相器、或门并最终使得反相器的输出点C出为1,pFET1截止; 此时A=0,B=1, C=1,pFET1截止;

=1经过反相器、或门并最终使得反相器的输出点C出为1,pFET1截止; 此时A=0,B=1, C=1,pFET1截止;

所以,发送0时,端口引脚上的数据也为0.

(2)P1作为普通I/O发送数据1时:

在平时,总是保持稳定输出0,即端口引脚总是保持0,此刻当要往外部发送1数据时,数据由0翻转为1;

所以内部数据1到达锁存器 后,

后, =0,图中D处即为

=0,图中D处即为 ;

;

nFET截止,pFET2导通,pFET2源极等于1,端口引脚也等于1,端口引脚1数据经反相器到达nFET3的栅极电压为0,所以nFET3导通,VCC又经过nFET3加到端口引脚上,所以端口引脚仍然是1,输出电流非常强;

但是,在这2个振荡器周期内,或门的上端输入端A点仍未刷新,即 =0时本该有A=1,但是此刻A仍为0,所以或门上端输入0、下端输入0使得或门的输出点C=0,pFET1导通;

=0时本该有A=1,但是此刻A仍为0,所以或门上端输入0、下端输入0使得或门的输出点C=0,pFET1导通;

这样,pFET1、pFET2、pFET3全部导通使得端口引脚快速上升到高电平;

其实pFET2导通时,端口引脚并不是一下子就上升到VCC,而是缓慢升起,当端口引脚升到2V以上时,才认为是高电平,把这高电平经反相器转换到达pFET3栅极变成低电平,pFET3这才导通。而pFET1加速了端口引脚的电压上升速度

接着讲,

当2个震荡器周期过了之后,或门的上端输入端A处开始刷新数据,此刻,A=1; =0;或门的下端输入点B=0,或门的端输出C=1;所以pFET1截止,相当撤去pFET1;

=0;或门的下端输入点B=0,或门的端输出C=1;所以pFET1截止,相当撤去pFET1;

最后,为端口引脚提供数据1的只剩下pFET2和pFET3,而pFET3又是最主要的,pFET2只提供辅助小的电流,pFET1只是起到pFET3加快导通的作用。

所以,P1的内部上拉就是这么得来,而且是针对发送数据1的情况下。

(3)P1作为普通I/O接收数据0:

当51作为接收模式的时候,仍然需要预先从51内部往外部引脚发送1数据,使得端口引脚保持上面的发送1数据模式状态,当外部设备发送一个低电平给51的时候,端口引脚上的电平变为低电平,此时端口引脚的低电平(低于2V以下)通过反相器后使得pFET3截止,而端口引脚的低电平经过两个反相器输入到单片机内部完成51的读操作。

pFET3截止,导致大电流不会流给外部设备造成损坏,而pFET2虽然还保持内部上拉作用,并对外部设备输出1,但是对51单片机的读操作没影响,pFET2的电流非常小(弱上拉)被外部设备拉低,pFET2的小电流流入外部设备因为太小也不会造成外部设备的损坏。所以51内部读到外部设备数据也将为0;

(4)P1作为普通I/O接收数据1:

当51作为接收模式的时候,内部仍然预先发送1;

此刻,外部设备给端口引脚一个高电平,送到51内部,这没什么问题,但是假如外部设备是由0变1给端口引脚,此刻pFET2导通,pFET3还在截止(端口电压没上升到2V以上的原因),由于外部设备高电平的上升电压过慢时,pFET2给端口引脚提供的从0到1电压的上升过程非常慢,这就导致51内部读取外部设备有延迟。

当端口引脚的电压上升到2V以上后,pFET3重新导通,大电流的pFET3加速了端口引脚的的电压的上升速度,把延迟降低;而外部设备的电流是输出的,和pFET3的大电流一同输入到51内部,所以对外部设备没影响,

侧面来看,当作为51输入模式时,应该格外注意外部设备的电流,过大会烧坏51芯片

浙公网安备 33010602011771号

浙公网安备 33010602011771号