verilog编写“11010”序列检测器

序列检测器是时序数字电路中非常常见的设计之一。它的主要功能是将一个指定的序列从数字码流中识别出来。序列检测器实现主要有两种方法:状态机和移位寄存器。

本设计要求:

序列检测器,din每个clk都会输入0或1,当检测到连续5个周期输入的din序列是11010时,dout会输出一个周期的脉冲。

1、状态机

1.1 实现原理

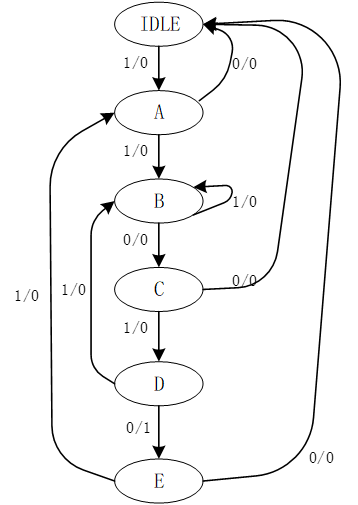

状态机实现序列检测器,其实就是每一bit的跳转都需要一个状态,顾状态机共有6个状态,分别是IDLE, A, B, C, D, E,状态机实现图如下所示:

图1 状态机

1.2 verilog代码:

-

module seq_checker (

-

input din,

-

input clk,

-

input rst_b,

-

output dout

-

);

-

parameter DLY = 0.1;

-

parameter IDLE = 3’d0;

-

parameter A = 3’d1;

-

parameter B = 3’d2;

-

parameter C = 3’d3;

-

parameter D = 3’d4;

-

parameter E = 3’d5;

-

reg [2:0] state;

-

assign dout = (state == E) ? 1’b1 : 1’b0;

-

always @(posedge clk or negedge rst_b) begin

-

if(!rst_b)

-

state <= IDLE;

-

else

-

case(state)

-

IDLE :

-

if(din == 1’b1)

-

state <= #DLY A;

-

else

-

state <= #DLY IDLE;

-

A :

-

if(din == 1’b1)

-

state <= #DLY B;

-

else

-

state <= #DLY IDLE;

-

B :

-

if(din == 1’b1)

-

state <= #DLY B;

-

else

-

state <= #DLY C;

-

C :

-

if(din == 1’b1)

-

state <= #DLY D;

-

else

-

state <= #DLY IDLE;

-

D :

-

if(din == 1’b1)

-

state <= #DLY B;

-

else

-

state <= #DLY E;

-

E :

-

if(din == 1’b1)

-

state <= #DLY A;

-

else

-

state <= #DLY IDLE;

-

default :

-

state <= #DLY IDLE;

-

endcase

-

end

-

endmodule

2、移位寄存器

2.1 实现原理

定义5bit寄存器shift_reg[4:0],通过左移的方式采样数据,当shift_reg[4:0]=5'b11010时,立即拉高dout。

2.2 verilog 代码:

-

module seq_checker(

-

input din,

-

input clk,

-

input rst_b,

-

output dout

-

);

-

parameter DLY 0.1;

-

parameter SEQ 5'b11010;

-

reg [4:0] shift_reg;

-

always @(posedge clk or negedge rst_b) begin: cache_data

-

if(!rst_b)

-

shift_reg <= 4'b0;

-

else

-

shift_reg <= {shift_reg[3:0], din};

-

end

-

assign dout = (shift_reg == SEQ) ? 1'b1 : 1'b0; //check target data

-

endmodule

综上所述:状态机和移位寄存器都能够实现序列检测器功能,且移位寄存器方案更简便,资源更少,且方便移植;而状态机方案则难以归一,浪费资源。

浙公网安备 33010602011771号

浙公网安备 33010602011771号