二分频电路

分频器还是比较简单的,一般的思路是:每数几个时钟就输出一个时钟。最简单的当数二分频器了,每当时钟上升沿(或下降沿)就把输出翻转一下。

这样就刚好实现了二分频器了。

网上也搜到了最简实现”二分频最简单了,一句话就可以了: always @ (negedge clk) clk_2<=~clk_2;“

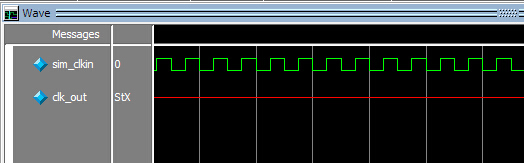

但仿真时却发现无法输出

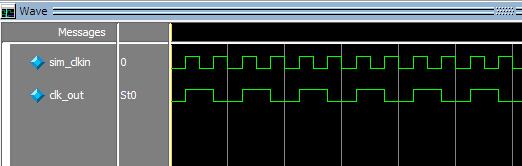

分析是因为输出信号的初始状态不确定造成的,于是加了一句初始化,就可以正常分频了

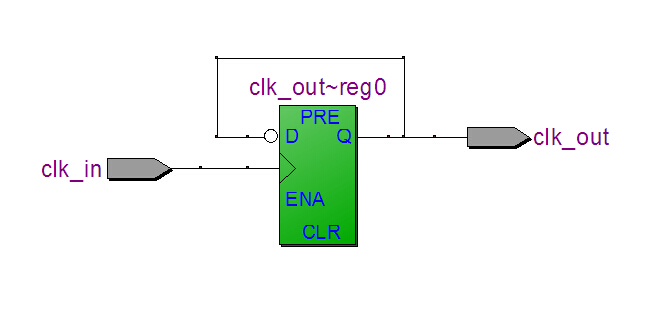

但观察他们生成的逻辑结构图是一样的

完整代码如下:

module divider2(clk_in, clk_out); input clk_in; output clk_out; reg clk_out; initial clk_out <= 1'b0; always@(posedge clk_in) clk_out <= ~clk_out; endmodule

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· 没有Manus邀请码?试试免邀请码的MGX或者开源的OpenManus吧

· 园子的第一款AI主题卫衣上架——"HELLO! HOW CAN I ASSIST YOU TODAY

· 【自荐】一款简洁、开源的在线白板工具 Drawnix