iic地址

IIC,两根线,SCL时钟线,SDA数据线。

一个主机master,一个或多个从机slave。

主机通常就是MCU,从机会有一个地址,这个地址通常前4位是器件本身固定的,5-7位可以硬件选择,最后一位通常是WP位,一般此位低电平表示正常读写,此位高电平表示读保护,只能读。如常用的EEPROM 24C02,地址高四位是1010,5-7位硬件连接决定,即是将其A0-A2引脚接地为000,这样设备地址是0xA0或者0xA1(读)。

IIC的指令:

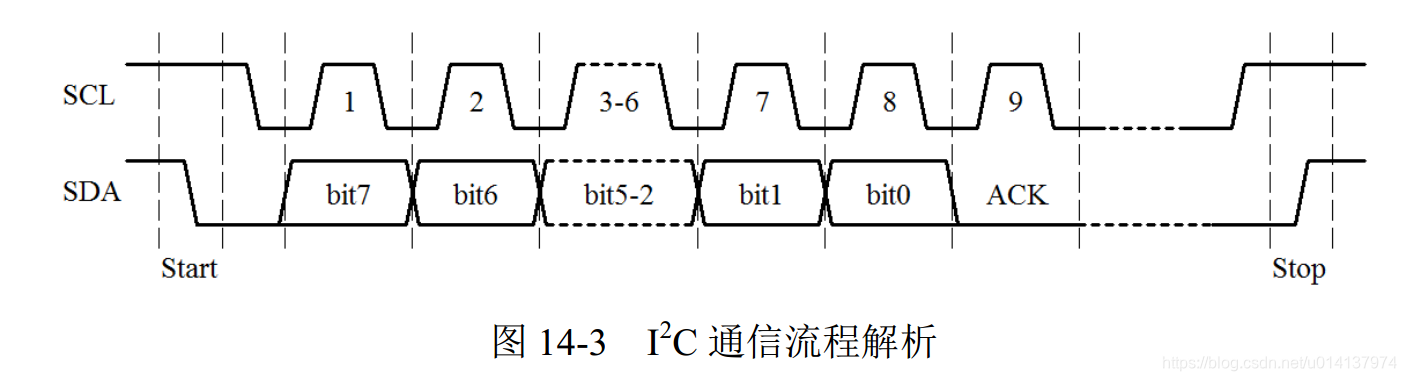

默认下(无数据传输):SCL=1,SDA=1;

Start:当SCL=1时,SDA由1向0跳变;

Stop:当SCL=1时,SDA由0向1跳变;

数据位:当SCL由0向1跳变时,由发送方控制SDA,此时SDA为有效数据,不可改变SDA;当SCL保持为0时,SDA上的数据可改变。也就是说,不管是主机发从机,还是从机发主机,只要想发送或者读取数据,必须有一个scl上升的过程,此时SDA数据有效,数据来自于发送方。

地址位:定义同数据位,但只由Master发给Slave;

应答位(ACK):发送SDA=0,可以是主机主动发送,也可以是从机发送主机接收。

否应答位(NACK):发送SDA=1,可以是主机主动发送,也可以是从机发送主机接收。

注意:

1,SCL一直由Master控制。

2,Start和Stop,只能由Master发出。

3,地址的8位传送完毕后,成功配置地址的Slave设备必须发送“ACK”。否则否则一定时间之后Master视为超时,将放弃数据传送,发送“Stop”。

4,当写数据的时候,Master每发送完8个数据位,Slave设备如果还有空间接受下一个字节应该回答“ACK”,Slave设备如果没有空间接受更多的字节应该回答“NACK”,Master当收到“NACK”或者一定时间之后没收到任何数据将视为超时,此时Master放弃数据传送,发送“Stop”。

5,当读数据的时候,Slave设备每发送完8个数据位,如果Master希望继续读下一个字节,Master应该回答“ACK”以提示Slave准备下一个数据,如果Master不希望读取更多字节,Master应该回答“NACK”以提示Slave设备准备接收Stop信号。

6,当Master速度过快Slave端来不及处理时,Slave设备可以拉低SCL不放(SCL=0将发生“线与”)以阻止Master发送更多的数据。此时Master将视情况减慢或结束数据传送。

在实际应用中,并没有强制规定数据接收方必须对于发送的8位数据做出回应,尤其是在Master和Slave端都是用GPIO软件模拟的方法来实现的情况下,编程者可以事先约定数据传送的长度,slave不检查NACK,有时可以起到减少系统开销的效果。但是如果slave方是硬件i2c要求一定要标准的NACK,master方是GPIO软件模拟i2c并没有正确的发送NACK,就会出现“slave收不到stop”导致i2c挂死。

浙公网安备 33010602011771号

浙公网安备 33010602011771号