ZYNQ PS端MIO的使用——FPGA Vitis篇

1. 前言

本实验介绍如何使用ZYNQ芯片PS端的MIO。MIO是ZYNQ芯片PS端的基础外设IO,可以连接诸如SPI,I2C,UART,GPIO等,通过Vivado软件设置,软件可以将信号通过MIO导出,同样也可以将信号通过EMIO(后续试验会介绍EMIO)连接到PL端的引脚上。

MIO共有两个BANK,BANK0有16个引脚,BANK1为38个引脚,共54个引脚,两个BANK的电压需要注意选择正确。

本实验通过实现PS端LED灯的闪烁演示MIO的操作。

2. MIO介绍

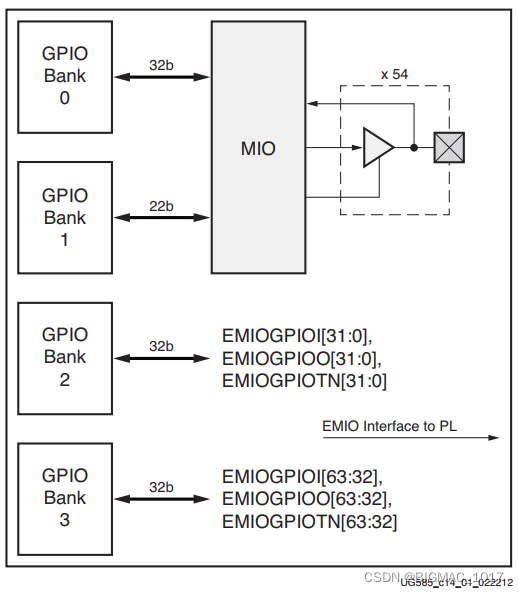

先来了解GPIO的BANK分布,在UG585文档GPIO一章中可以看到GPIO是有4个BANK,注意与MIO的BANK区分。

GPIO的BANK0控制32个信号,BANK1控制22个信号,总共是MIO的54个引脚,也就是诸如SPI、I2C、USB、SD等PS端外设接口;

BANK2和BANK3共能控制64个PL端引脚,注意每一组都有三个信号,输入 EMIOGPIOI,输出EMIOGPIOO,输出使能EMIOGPIOTN,类似于三态门,共192 个信号。可以连接到PL端引脚,通过PS控制信号。

3. Vivado工程编写

虽然本实验仅仅使用了FPGA的PS端,但是还要建立一个Vivado工程,用来配置PS管脚。虽然PS端的ARM是硬核,但是在ZYNQ当中也要将ARM硬核添加到工程当中才能使用。本实验使用的Vivado版本为Vivado2021.1。

(1)本实验使用的Vivado工程延用《ZYNQ 串口打印输出——FPGA Vitis篇》中使用的Vivado工程,大家可以查看该文章来了解Vivado工程的建立。

(2)Vivado工程唯一需要修改的地方如下:控制PS的MIO是需要将GPIO MIO 勾选,如下图所示。

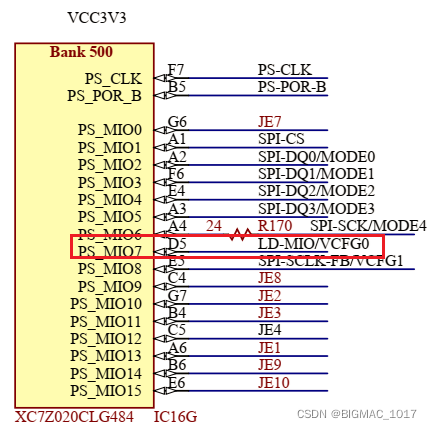

(3)实验使用的硬件为ZedBoard,根据ZedBoard的原理图可知,MIO bank0上的 MIO7管脚连接了1个LED外设。

因此,根据原理图,需要将Bank0 I/O Voltage设置为LVCMOS3.3V,由于该管脚接的为LED外设,可以将“Speed”选为“slow”。

(4)至此,Vivado工程编写结束,保存工程,点击Vivado “Flow Navigator”一栏里的“Generate Bitstream”,等待Vivado生成好bit文件后,在菜单栏“File -> Export -> Export Hardware…”导出硬件信息(.xsa文件),这里就包含了PS端的配置信息。该步骤如有疑问,可以参考以前的文章《ZYNQ串口打印输出——FPGA Vitis篇》。

4. Vitis工程编写

(1)点击 Vivado 菜单“Tools-> Launch Vitis IDE”,启动 Vitis。

(2)新建 Vitis平台工程。Vitis工程的建立可以参考以前的文章《ZYNQ串口打印输出——FPGA Vitis篇》。

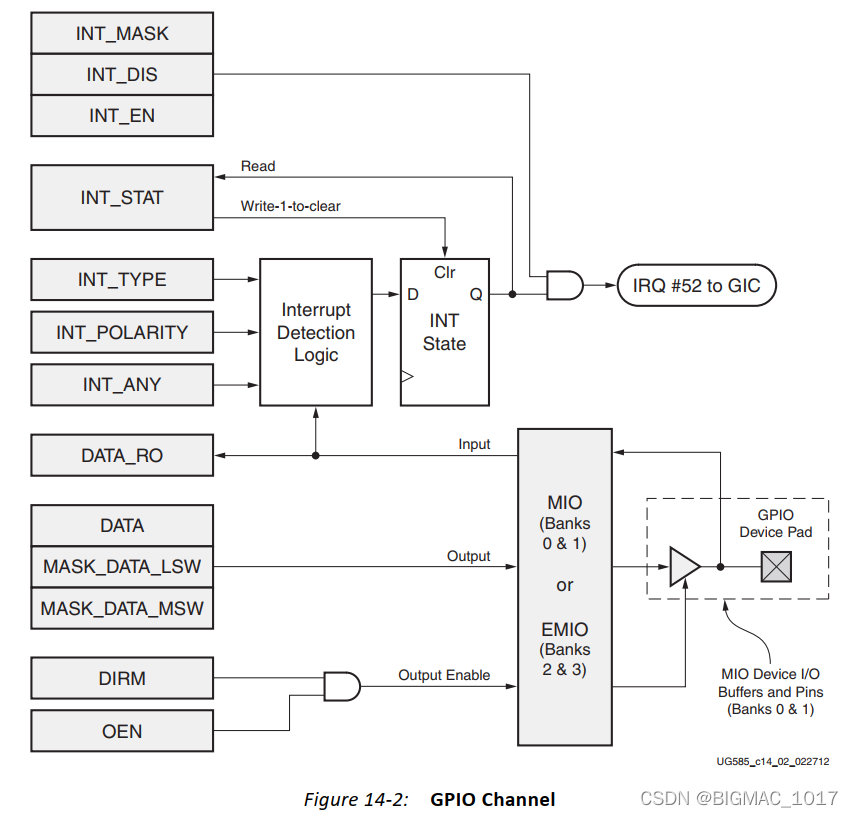

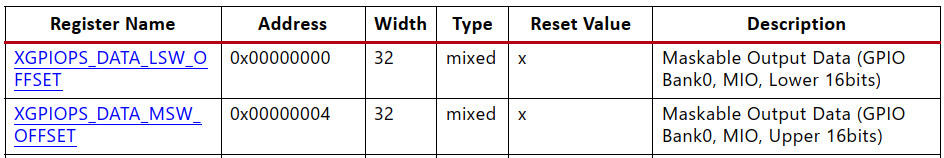

(3)下图为GPIO的控制框图,实验中会用到输出部分的寄存器,数据寄存器 DATA,数据掩码寄存器MASK_DATA_LSW,MASK_DATA_MSW,方向控制寄存器 DIRM,输出使能控制器OEN。

UG585手册中,在“Appx. B: Register Details”中的“General Purpose I/O (gpio)”能查询到关于GPIO寄存器的详细使用说明。

(4)实验中可能会用到的寄存器:

数据掩码寄存器: 例如接LED的MIO 7管脚在GPIO的BANK0,可以通过以下寄存器来屏蔽其他BANK0中的其他31位。

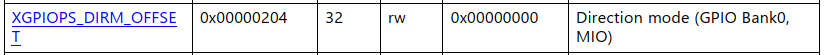

方向寄存器: 控制数据的方向

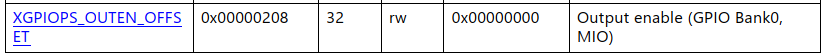

输出使能寄存器:

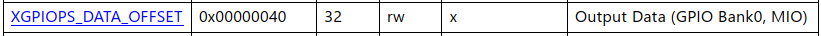

数据寄存器:

(5)新建 Vitis应用工程:一开始编写代码可能会无从下手,我们可以导入Xilinx提供的example工程。打开刚建立的Vitis工程,点击“Board Support Package”,通过选择“ps7_gpio_0”的“Import Examples”,可以导入官方提供的PS端GPIO例程。

由于本实验只是通过PS端的GPIO来点亮LED灯,不涉及中断使用,因此我们选择“xgpiops_polled_example”工程。

(6)这个example工程是测试PS端MIO的输入输出的,由于ZedBoard开发板PS端的LED是MIO7,因此我们需要在文件中修改Output_pin为7,测试 MIO7的LED灯。

(7)编译工程,将工程下载到硬件板卡上(编译和下载方式见《ZYNQ 串口打印输出——FPGA Vitis篇》),打开串口助手。

实验结果为板卡的MIO7灯会闪烁;

串口助手打印信息如下:

注:Xilinx官方MIO测试工程里也包含了MIO输入测试代码,用户要将其注释掉,以免串口打印错误信息同时会阻塞“main”主函数正常运行。

5. 实验小结

本实验介绍了ZYNQ如何使用PS端的MIO进行输入输出控制。

实验使用Xilinx官方的例子比较方便,但是它的代码看起来比较臃肿,我们可以通过学习它的方法,简化下工程。简化的工程见附录。

A. 附录

本小结介绍如何简化官方的工程,来建立一个MIO输出控制的测试工程。

(1)延用第4章建立的Vitis平台工程。

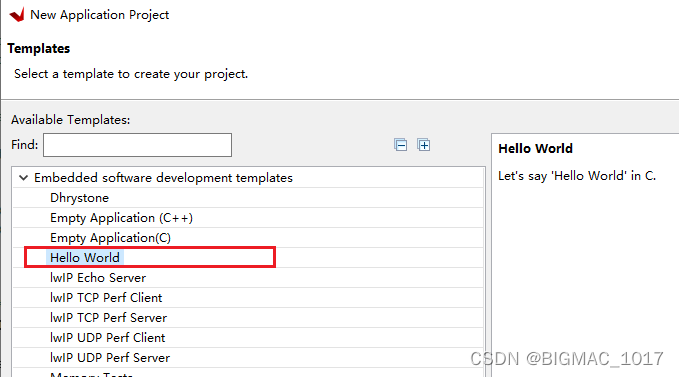

(2)新建Vitis应用工程,这里我们套用官方的“Hello World”模板工程。

(3)修改Vitis应用工程的代码:在“Hello World”模板工程的“helloworld.c”文件中修改。

程序步骤如下:

- 初始化GPIO;

- 设置方向;

- 输出使能;

- 控制GPIO输出值;

代码修改如下:

(4)编译工程,将工程下载到硬件板卡上。实验结果为LED每秒会闪烁一次。

B. 工程源码下载

如果大家对我们的文章感兴趣,可以关注我们的微信公众号:“图灵研究院”:

该工程对应的源码可以通过关注该微信公众号,在公众号输入ZYNQ_PS_MIO来获取工程的下载链接,工程采用的是Vivado2021.1版本。

参考文献:

[1] http://www.alinx.com.cn/.

[2] Zynq-7000 SoC Technical Reference Manual(UG585). Xilinx官方文档

[3] ZYNQ 串口打印输出——FPGA Vitis篇. 图灵研究院

浙公网安备 33010602011771号

浙公网安备 33010602011771号