硬件debug指南][1] - Vivado调试工具介绍 - 知乎

本专栏旨在为使用Xilinx FPGA/SoC + Vivado设计硬件的小伙伴们提供一系列教程, 主要以Zedboard为平台介绍Vivado提供的几种硬件调试工具. 文章内容主要源自对官方文档的归纳整理, 读过本教程后应该能更容易读懂官方文档. 推荐之后读一下官方手册来获得更全面的信息.

1. Vivado提供的硬件调试工具 (Debug Features in Xilinx Vivado)

这里简要介绍Vivado中常用的调试工具, 主要介绍几种工具都适合于什么样的应用. 每一个工具详细的使用方法会在后续的文章中用实际的栗子来说明.

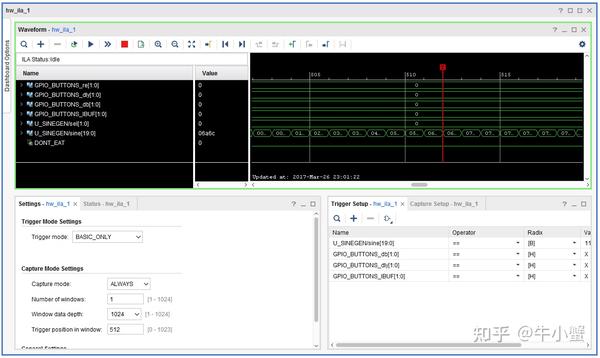

1.1 ILA/System ILA (Integrated Logic Analyzer)

这个应该是硬件调试中最常用的工具了. 顾名思义, ILA就是FPGA上的逻辑分析仪, 可以用来监测设计中的任何一个线网(net)上的信号波动. 而且ILA不仅支持对单一的信号线或者bus来进行检测, 还特别提供对AXI总线调试的支持, 可以很方便的观察AXI总线上的信号传递(配合Vivado波形观察窗口里面的自动标注功能). 此外ILA能够很方便的设计复杂的触发(trigger)条件来满足各种需求. 总而言之, 如果需要观察信号的话, 主要使用ILA.

Vivado提供ILA和System ILA, 这二者在我看来差别不大(特别是新版的ILA). 细微的差别在于ILA只能配置成检测普通信号(Native Mode)或者AXI总线信号(AXI Mode)中的其中一种; 而System ILA可以同时检测两种信号. 此外ILA可以在不同的阶段被插入到设计中, 但是System ILA只能作为IP在源码(RTL Code)阶段插入到设计中. 这一点我会在后面进行介绍.

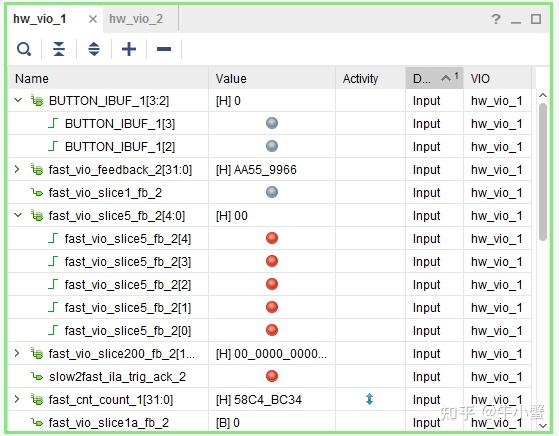

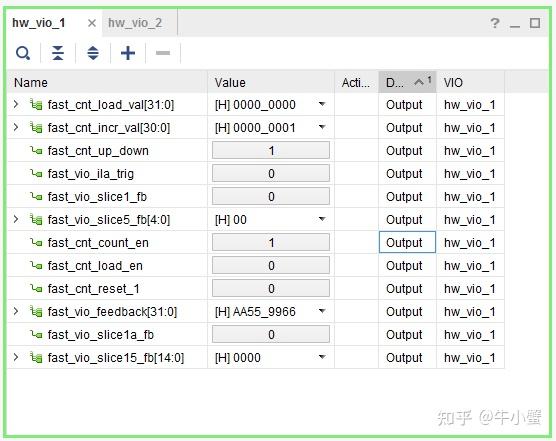

1.2 VIO (Virtual Input/Output)

VIO是用来监测和驱动信号的, 它最主要的用途是来在调试的过程中来模拟外设. 可以把它理解为虚拟的PCB上的拨动开关+LED (从性能上也停留在开关和LED层面). 因此VIO的监测功能主要用作状态指示, 与ILA的区别在于VIO是不能够显示波形的, 只能显示每次手动/自动刷新(500ms)时候的当前值; 此外VIO是不能配置触发(trigger)条件的. 同样, VIO的信号驱动功能类似于我们在设计时用一个拨动开关来控制FPGA上电路, VIO的输出主要用作低速控制信号, 不适合(速度达不到)用来输出高速数据信号.

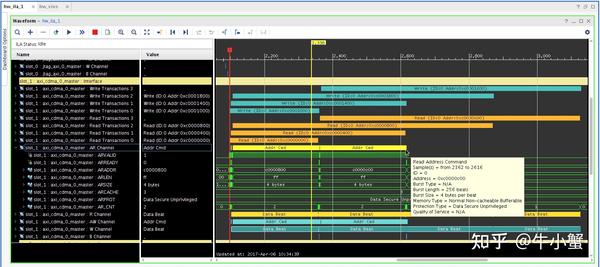

1.3 JTAG-to-AXI Master

这个工具是专门用来调试AXI总线的, 它的一端是AXI的主端口(Master), 另一端是JTAG端口(由Vivado自动控制). 进而它可以在Tcl命令的控制下向AXI奴端口(Slave)发送数据/指令包. 与ILA/System ILA的AXI调试功能不同之处在于, JTAG-to-AXI Master是没有图形界面的, 只能够在terminal里面通过输入Tcl命令来操作; 而ILA/System ILA是有图形界面, 就像时序仿真时那样可以观察信号波形. 此外ILA/System ILA只能用来监测AXI总线上的信号; 而JTAG-to-AXI Master是为了驱动AXI总线, 并发送/读取数据. 在我看来, 如果是为了验证AXI的协议是否被正确implement, 用ILA/System ILA来调试; 如果是为了验证包含AXI奴端口的IP的功能是否正确(譬如memory的地址是否正确), 则用JTAG-to-AXI Master来调试.

1.4 几种调试工具的对比

这里总结一下几种工具的差别:

- ILA/System ILA:

- 只能用来观察信号, 但是可以观察线网上的任意信号, 有存储深度, 可以显示波形

- 可以配置复杂的触发条件 -> "数字示波器"

- 可以(以FPGA上时钟的速率)观察高速的信号

- 观察AXI总线时用来调试通信协议是否正确

- VIO:

- 模拟拨动开关+LED灯, 没有存储深度, 不可以显示波形

- 可以用来观察+驱动信号, 但是速率大大受限(最高500ms的刷新率)

- 适用于驱动控制(低速)信号, 适用于观察状态指示(低速)信号

- JTAG-to-AXI Master

- 用来调试包含AXI奴端口的电路, 通过命令行来使用

- 可以驱动AXI总线, 发送/接受AXI的包(数据+命令)

- 主要用来验证电路的功能, 即AXI与内部电路的连接是否正确

2. Vivado是如何实现硬件调试的

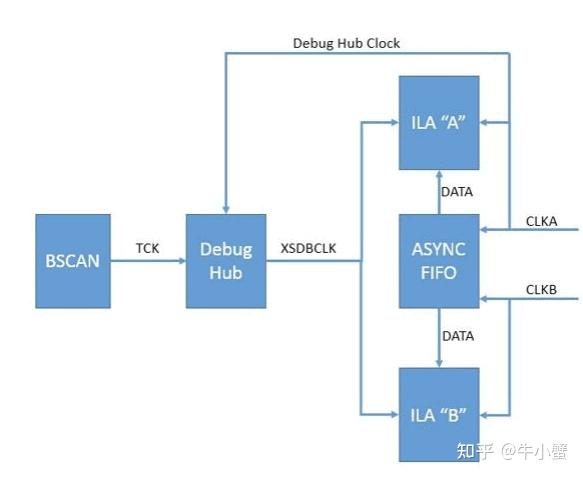

最后简要介绍一下Vivado是如何利用上面的工具来实现硬件调试的. 上面几种工具在FPGA上被称作Debug Core, 我们在调试时插入合适的Debug Core, 然后在综合的时候Vivado会自动插入一个叫做Debug Hub的模块. 它的作用是连接JTAG (JTAG Boundary Scan, BSCAN)和Debug Cores (ILA/VIO/JTAG-to-AXI). 这样在我们生成bitstream并烧到FPGA上之后, Vivado Hardware Manager可以通过JTAG来控制Debug Core并接受数据. 下面这张图显示了JTAG(BSCAN), Debug Hub和Debug Cores(ILA "A"和ILA "B")的关系. 这里ASYNC FIFO是被调试的设计.

当我们烧入bitstream并用Vivado Hardware Manager来连接我们的FPGA板时, Hardware Manager会首先用JTAG通信来扫描是否有Debug Hub, 然后Debug Hub会继续去扫描是否有Debug Core.

从时钟而言, JTAG的时钟用在JTAG和Debug Hub通信, Debug Hub的时钟用在Debug Hub和Debug Core之间的通信, 而各个Debug Core的时钟则用在采样需要监测的信号.

3. End

以上就是Vivado中常见的调试工具, 下一篇教程我们将介绍具体如何在设计中插入调试工具. 具体来说, 配置调试工具有两种方式: 基于流程的方法(Netlist Insertion Debug Flow)和基于IP的方法(HDL Instantiation Debug Probing Flow). 我也会尝试讨论两种方法的差别.

才疏学浅, 欢迎指正

4. 参考文献

- UG908 Vivado Design Suite User Guide: Programming and Debugging (v2022.1)

浙公网安备 33010602011771号

浙公网安备 33010602011771号