AXI总线

AXI总线简介

AXI总线是一种总线协议,是ARM公司提出的AMBA3.0协议(目前已AXI4已发布) 中的最重要的部分,是一种高性能、高带宽、低延时的片内总线。支持不对齐的数据传输和突发传输。在突发传输中只需要首地址,并且支持同时分离的读写数据通道、支持显著传输访问和乱序访问。

AXI的前两代分别是AHB(2.0)、ASB(1.0)。其中AMBA还包含一个APB总线,该总线是专门连接IIC、UART等低带宽接口而设计的。

AXI协议的几个关键特性

- 读写地址、数据分开;

- 通过字节选通信号(WSTRB)实现支持非对齐数据传输功能;

- 使用突发模式时,只需要传输首地址和设置突发长度即可;

- 读数据和写数据通道独立,从而支持低功耗DMA;

- 支持outstanding功能,可以发送多个地址进行读写;

- 支持out-of-order传输(即乱序传输);

- 可以比较容易的添加寄存器级,以此来实现时序收敛;

- 每个信道都有一对握手信号;

- 读数据和写数据通道都包含一个LAST信号,用来指明事物传输的最后一个数据;

AXI总线的基本架构

AXI总线的5个传输通道

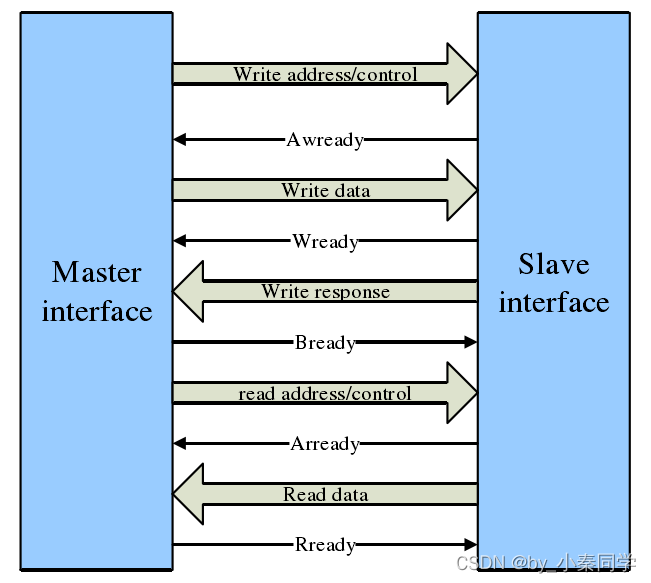

AXI总线通过5个通道实现读写操作,这5个通道分别是:读地址通道、写地址通道、读数据通道、写数据通道和写响应通道。

- 这5条独立的通道各自都包含一个双路的valid和ready握手信号。

- 在读数据和写数据通道中还包含一个last信号,表示事务传输的最后一个数据。

- 读数据通道中包含读数据和读响应信号,读响应信号表示读事务的完成。

- 写数据通道中,每8位数据都会有一个byte lane,该信号表示数据总线上哪些byte数据有效(因为AXI支持不对齐的数据传输);写响应信号表示从设备响应写事务。

- AXI支持乱序传输,会给每个事务一个IDtag,协议会要求相同IDtag的事务必须有序完成,不同IDtag之间可以乱序完成。

![请添加图片描述]()

AXI总线的读写流程

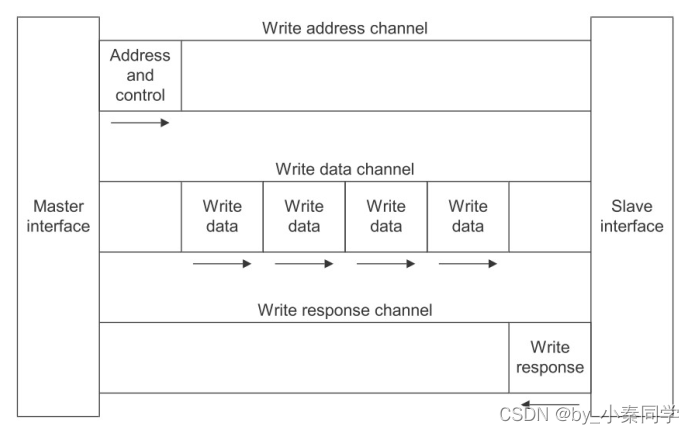

- 主设备向从设备写数据:首先,主设备通过写地址通道向从设备说明要控制的寄存器地址,以及一些突发模式和控制信号;主设备通过写数据通道向从设备写入数据;最后从设备通过写响应通道进行应答;完成向从设备的写数据操作。

![请添加图片描述]()

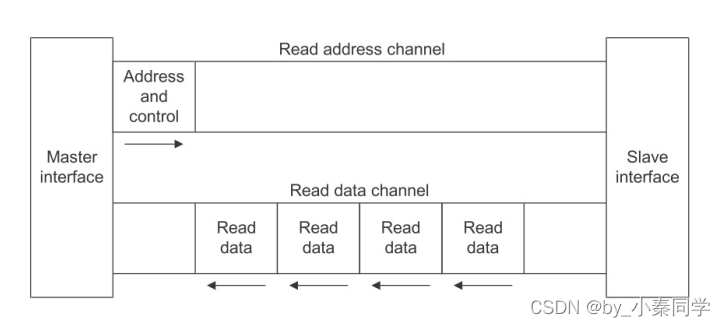

- 主设备从从设备读数据:首先,主设备通过读地址通道向从设备说明要控制的寄存器地址和控制信号;当从设备接收到这些信息后偶,会根据这些信息进行读取数据的处理;完成这些处理后,从设备会通过读数据通道将数据发送给主设备。

![请添加图片描述]()

信号描述

1. 全局变量

| 信号 | 源 | 描述 |

|---|

| ACLK |

时钟源 |

全局复位时钟 |

| ARESETn |

主复位信号 |

全局复位信号,低电平有效 |

2. 写地址通道(AW)

| 信号 | 源 | 描述 | 个人理解 |

|---|

| AWID [3 :0] |

主机 |

写地址ID ,表示写地址信号组的IDtag。 |

可以联想到刚才的AXI支持乱序传输的功能 |

| AWADDR[31:0] |

主机 |

写地址。 |

这个就是我们的主要数据 |

| AWLEN [3 :0] |

主机 |

突发式写的长度 。 |

AXI支持突发模式,表示突发模式的数据个数,最大支持16,但是每次突发的长度需要该信号发送给从设备 |

| AWSIZE[2:0] |

主机 |

突发式写的大小 |

每次传输的数据大小,2^(AWSIZE),既可以是1-128宽度 |

| AWBURST[1:0] |

主机 |

突发式写的类型 |

固定式的突发读写(00)、增值式突发读写(01)、包装式突发读写(10) |

| AWLOCK[1:0] |

主机 |

锁类型 |

ARLOCK[1:0]或 AWLOCK[1:0]来选择独占式存取,用信号RRESP[1:0]或 BRESP[1:0]来指明独占式存取的成功与否 |

| AWCACHE[3:0] |

主机 |

Cache类型。这信号指明事务的bufferable、cacheable、write-through、write-back、allocate attributes信息 |

|

| AWPROT[2:0] |

主机 |

保护类型 |

1.正常存取或者特权存取,AWPROT[0]2.安全性存取或者没有安全性存取,AWPROT[1] 3.指令存取或者数据存取,AWPROT[2] |

| AWVALID |

主机 |

写地址有效。1表示有效,该信号会一直保持,知道AWREADY变为高 |

个人认为这个信号也和AWADDR同步,因为该信号表示的是AWDDR数据的有效性 |

| AWREADY |

设备 |

从设备应答。1表示设备准备好,0则没准备号 |

表示从设备能够接收地址信号了,拉高应该也就代表着地址接收成功了(或者说只要准备好标志拉高,经过一个时钟周期就默认从设备接收成功了) |

3. 写数据通道

| 信号 | 源 | 描述 | 个人理解 |

|---|

| WID[3:0] |

主机 |

写IDtag,WID的值必须与AWID的值匹配 |

联想到AXI支持乱序传输的功能;需与WID匹配,匹配才能表示地址和数据是写到相同的从设备上 |

| WDATA[31:0] |

主机 |

写数据 |

该通道的主要信息 |

| WSTRB[3:0] |

主机 |

写阀门。标志的区间为WDATA[(8n)+7:(8n)] |

表示WDATA中的某个字节 |

| WLAST |

主机 |

写的最后一个数据 |

应该是突发模式的时候表示该次突发的最后一个数据 |

| WVALID |

主机 |

写有效,1表示有效 |

表示写数据有效,写数据已经放到总线上了 |

| WREADY |

设备 |

写就绪,1表示就绪 |

和AWREADY同样的道理 |

4. 写通道响应

| 信号 | 源 | 描述 | 个人理解 |

|---|

| BID[3:0] |

设备 |

响应ID,必须与AWID匹配 |

也是为了支持乱序传输服务(也不止于此,因为一般都是多个从设备) |

| BRESP[1:0] |

设备 |

写响应 |

这个信号指明事务的状态。可能有的响应:OKAY、EXOKAY、SLVERR、DECERR |

| BVALID |

设备 |

写响应有效 |

这个就解释了我在理解AWREADY信号时的纠结,该信号应该是辅助判断写操作是否成功 |

| BREADY |

主机 |

接收响应就绪,1表示主机继续 |

该信号用来表示主机准备好接收响应通道的信号了,感觉就是多级反馈信号,以避免数据出错 |

5. 读地址通道

| 信号 | 源 | 描述 | 个人理解 |

|---|

| ARID [3:0] |

主机 |

读地址ID ,表示读地址信号组的IDtag。 |

可以联想到刚才的AXI支持乱序传输的功能 |

| ARADDR[31:0] |

主机 |

读地址。 |

这个就是我们的主要数据 |

| ARLEN [3:0] |

主机 |

突发式读的长度 。 |

AXI支持突发模式,但是每次突发的长度需要该信号发送给从设备 |

| ARSIZE[2:0] |

主机 |

突发式读的大小 |

突发式写的大小 |

| ARBURST[1:0] |

主机 |

突发式读的类型 |

突发式写的类型 |

| ARLOCK[1:0] |

主机 |

锁类型 |

ARLOCK[1:0]或 AWLOCK[1:0]来选择独占式存取,用信号RRESP[1:0]或 BRESP[1:0]来指明独占式存取的成功与否 |

| ARCACHE[3:0] |

主机 |

Cache类型。这信号指明事务的bufferable、cacheable、write-through、write-back、allocate attributes信息 |

|

| ARPROT[2:0] |

主机 |

保护类型 |

1.正常存取或者特权存取, ARPROT[0] 2.安全性存取或者没有安全性存取, ARPROT[1] 3.指令存取或者数据存取 ARPROT[2] |

| ARVALID |

主机 |

读地址有效。1表示有效,该信号会一直保持,知道AWREADY变为高 |

个人认为这个信号也和ARADDR同步,因为该信号表示的是ARADDR数据的有效性 |

| ARREADY |

设备 |

从设备应答。1表示设备准备好,0则没准备号 |

表示从设备能够接收地址信号了,拉高应该也就代表着地址接收成功了(或者说只要准备好标志拉高,经过一个时钟周期就默认从设备接收成功了) |

6. 读数据通道

| 信号 | 源 | 描述 | 个人理解 |

|---|

| RID[3:0] |

设备 |

读IDtag,WID的值必须与AWID的值匹配 |

联想到AXI支持乱序传输的功能;需与WID匹配,匹配才能表示地址和数据是读到相同的从设备上 |

| RDATA[31:0] |

设备 |

读数据 |

该通道的主要信息 |

| RRESP[1:0] |

设备 |

读响应。指明传输的状态:OKAY(00)、EXOKAY(01)、SLVERR(10)、DECERR(11) |

写响应有专门的通道,但是读响应包含在读数据通道内 |

| RLAST |

设备 |

读的最后一个数据 |

应该是突发模式的时候表示该次突发的最后一个数据 |

| RVALID |

设备 |

读有效,1表示有效 |

表示读数据有效,读数据已经放到总线上了 |

| RREADY |

主机 |

读就绪,1表示就绪 |

和ARREADY同样的道理 |

7. 低功耗接口

| 信号 | 源 | 描述 | 个人理解 |

|---|

| CSYSREQ |

时钟源 |

系统低功耗请求。此信号来自系统时钟控制器,使外围设备进入低功耗状态 |

低功耗信号 |

| CSYSACK |

外围设备 |

低功耗请求应答 |

|

| CACTIVE |

外围设备 |

clock active。1表示外围设备时钟请求 |

|

| CSYSREQ |

时钟源 |

系统低功耗请求。此信号来自系统时钟控制器,使外围设备进入低功耗状态 |

低功耗信号 |

| CSYSACK |

外围设备 |

低功耗请求应答 |

|

| CACTIVE |

外围设备 |

clock active。1表示外围设备时钟请求 |

![请添加图片描述]()

浙公网安备 33010602011771号

浙公网安备 33010602011771号