AXI

注:本文转自赛灵思中文社区论坛,源文链接在此。本文原作者为XILINX工程师。

以下为个人译文,仅供参考,如有疏漏之处,还请不吝赐教。

AXI 是赛灵思器件设计中广泛使用的处理器接口。这一全新的博客系列将介绍有关 AXI 接口的一些基础知识。

本篇作为此系列首篇博文,将提供有关 AXI 标准的综述。

引言

近来,几乎每个赛灵思 IP 都使用 AXI 接口。Zynq®、Zynq MP、MicroBlaze™ 和全新的 Versal™ 处理器都无一例外使用 AXI 接口。因此,AXI 接口已成为几乎所有新的赛灵思器件设计中不可或缺的一部分。充分了解其基础知识对于赛灵思器件的设计和调试都很有帮助。

本篇博文将介绍赛灵思器件上的 AXI3/AXI4 的相关基础知识。首先,我们将从一些通俗易懂的知识、理论和术语开始讲解。

何谓 AXI?

AXI 表示 Advanced eXtensible Interface(高级可扩展接口),它是由 Arm 定义的接口协议,包含在“高级微控制器总线架构 AMBA”标准中。

AXI3/AXI4 规格可通过 Arm 网站免费获取(链接),因此如果您对其感兴趣,我鼓励您务必下载。

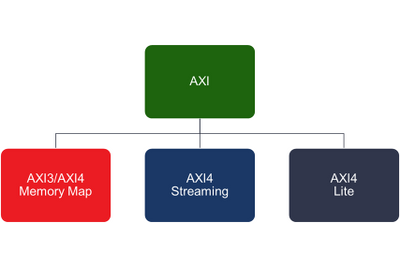

AXI4 接口 (AMBA 4.0) 分 3 种类型:

- AXI4 (AXI4-Full):用于满足高性能存储器映射需求。

- AXI4-Lite:用于简单的低吞吐量存储器映射通信(例如,往来于状态寄存器的通信)。

- AXI4-Stream:用于高速数据流传输。

注 1 :本文不涵盖 AXI4-Stream 相关内容。此处“AXI”表示 AXI3、AXI4 和 AXI4-Lite。

注 2:AXI3 接口与 Full AXI 接口接近。

AXI 读写通道

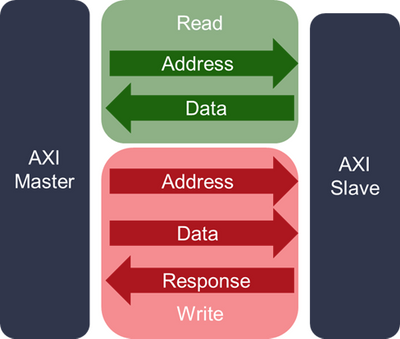

AXI 协议定义了 5 条通道:

- 其中 2 条用于读取传输事务

- 读地址

- 读数据

- 另 3 条用于写入传输事务

- 写地址

- 写数据

- 写响应

通道 (channel) 是与 VALID 和 READY 信号关联的 AXI 信号的独立集合。

注:AXI4/AXI3/AXI4-Lite 接口只能用于读取(仅包含 2 条读取通道)或者只能用于写入(仅包含 3 条写入通道)。

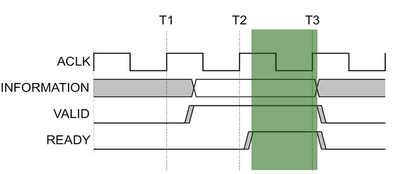

任一通道上发射的每一条数据都称为一次传输 (transfer)。当 VALID 和 READY 信号均处于高位并且时钟存在上升沿时,就会发生传输。例如,在下图中,在 T3 处正在发生传输:

AXI 读取传输事务

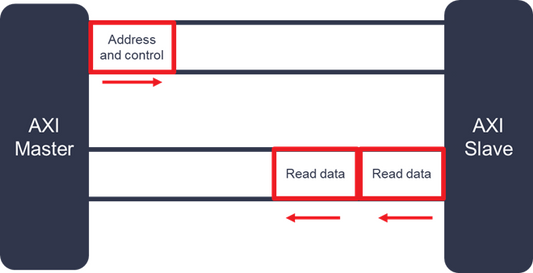

AXI 读传输事务需要在 2 条读取通道上发生多次传输。

- 首先,地址读通道 (Address Read Channel) 从主接口 (Master) 发送到从接口 (Slave),以便设置地址和部分控制信号。

- 然后,此地址的数据通过读数据通道 (Read data channel) 从从接口发射到主接口。

请注意,根据下图所示,每个地址中可发生多次数据传输。此类型的传输事务称为突发 (burst)。

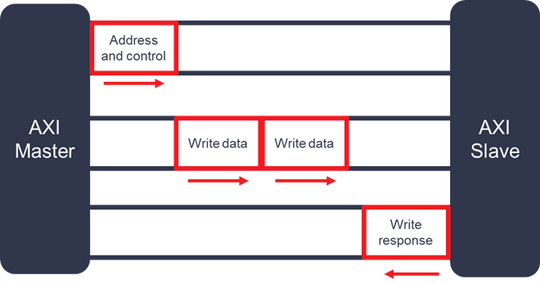

AXI 写入传输事务

AXI 写入传输事务需要在 3 条读取通道上存在多次传输。

- 首先,写地址通道 (Address Write Channel) 从主接口发送到从接口,以便设置地址和部分控制信号。

- 然后,此地址的数据通过写数据通道 (Write data channel) 从主接口发射到从接口。

- 最后,写入响应通过写响应通道 (Write Response Channel) 从从接口发送到主接口,以指示传输是否成功。

写响应通道 (Write Response Channel) 上可能的响应值包括:

- OKAY (0b00):正常访问成功。表示已成功完成正常访问

- EXOKAY (0b01):专属访问成功。

- SLVERR (0b10):从接口错误。已成功访问从接口,但从接口希望向发端主接口返回错误条件(例如,数据读取无效)。

- DECERR (0b11):解码器错误。通常由互连组件生成,用于指示传输事务地址处没有任何从接口

注:读取传输事务同样包含响应值,但此响应通过读响应通道 (Read Response Channel) 来发射

AXI4 接口要求

在 AXI4 规格中记录了部分要求。

最值得注意的是:

- 当 VALID (AxVALID/xVALID) 信号断言有效时,它必须保持处于已断言有效状态直至从接口断言 AxREADY/xREADY 有效后出现上升时钟沿为止。

- 发送信息的 AXI 接口的 VALID 信号不得从属于接收该信息的 AXI 接口的 READY 信号。但是,READY 信号的状态可从属于 VALID 信号

- 写响应必须始终位于所属的写入传输事务中最后一次写入传输之后

- 读数据必须始终位于数据相关的地址之后

- 从接口必须等待断言 ARVALID 和 ARREADY 有效后,才能断言 RVALID 有效以指示该有效数据可用

在下一篇 AXI 基础系列文章中,我们将使用 AXI Verification IP (AXI VIP) 对 AXI4 接口进行仿真。

浙公网安备 33010602011771号

浙公网安备 33010602011771号