system ila的使用

片内逻辑分析仪的使用原理 使用ILA观测AXI总线以及用户逻辑

学习内容

本课 重点介绍片内逻辑分析仪的使用原理,以及如何使用 ILA 对 AXI 总

线进行观测分析,实现对 FPGA 设计的全局规划和细节分析。

实现步骤

逻辑分析仪主要有以下几个阶段:

1,预触发阶段。

2,触发并采集阶段。

3,采集结束并上传到电脑。

4,用户界面显示并解析。

在vivado 中可以使用 ILA IP 核,使用片内的任意时钟来观测片内的任意信号。

Step1 建立 vivado 工程,添加 IP ,进行布线。

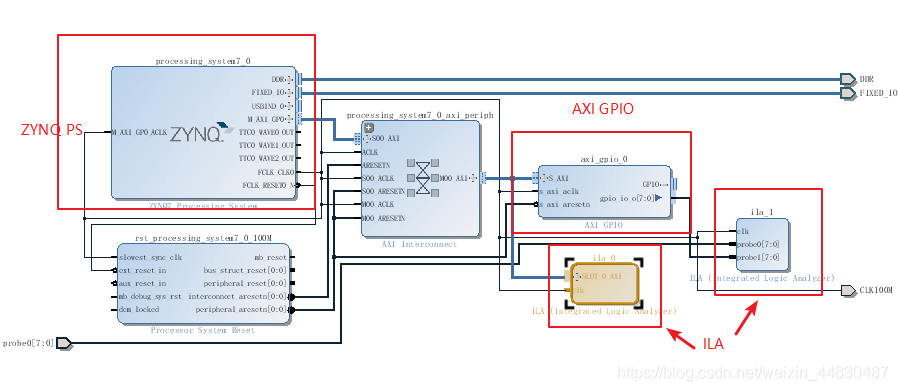

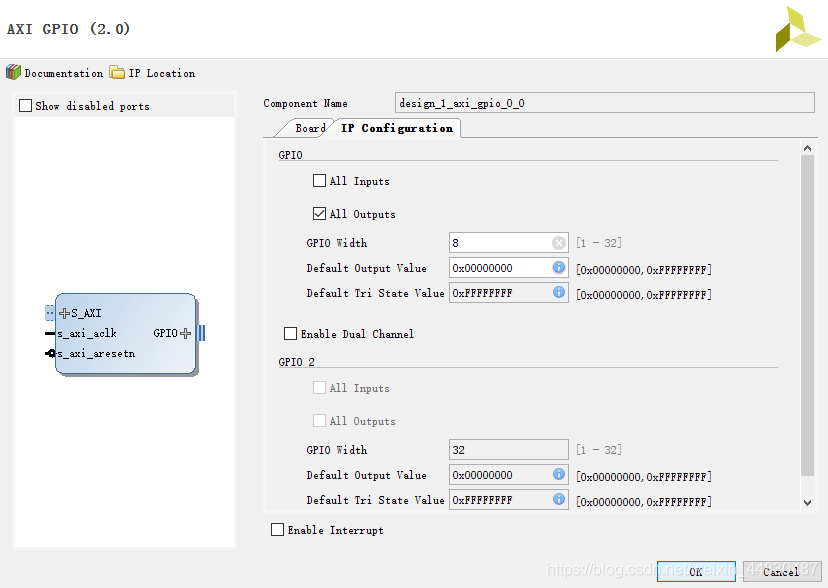

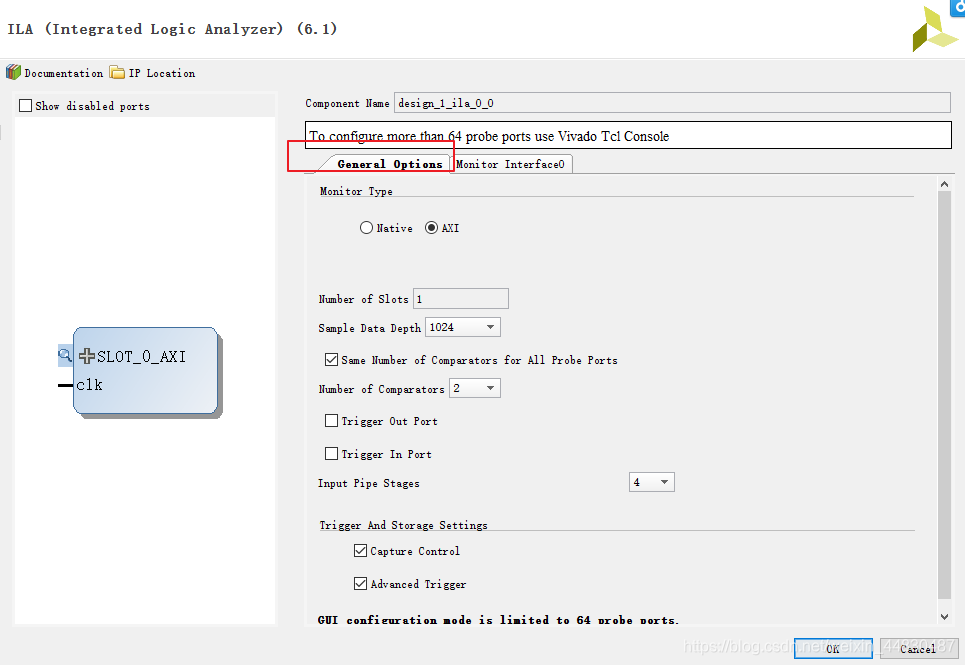

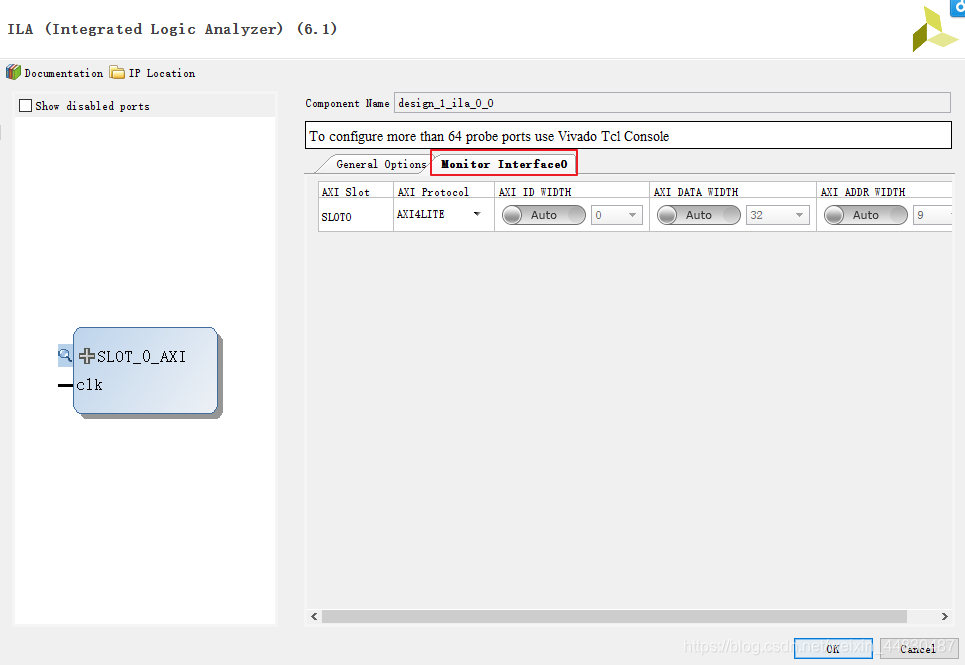

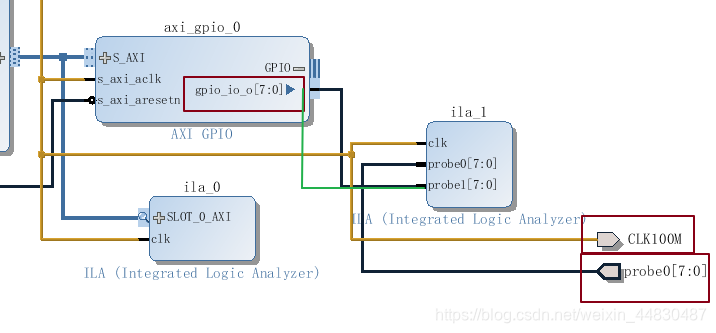

添加Processor System AXI GPIO 2个 ILA IP 核,其中 ILA0 用于观察 AXI GPIO 的 AXI 总线, ILA1用于观察 AXI GPIO 的 GPIO 输出。

其中AXI GPIO IP 和 ILA IP 设置如下:

在连线过程中,将ILA0 的 AXI 观测接口与 AXO GPIO 的 AXI 总线连接,

clk 与 AXO GPIO s_axi_clk 连接,且是与 ZYNQ PS 的 FCLK_CLK0 连接。

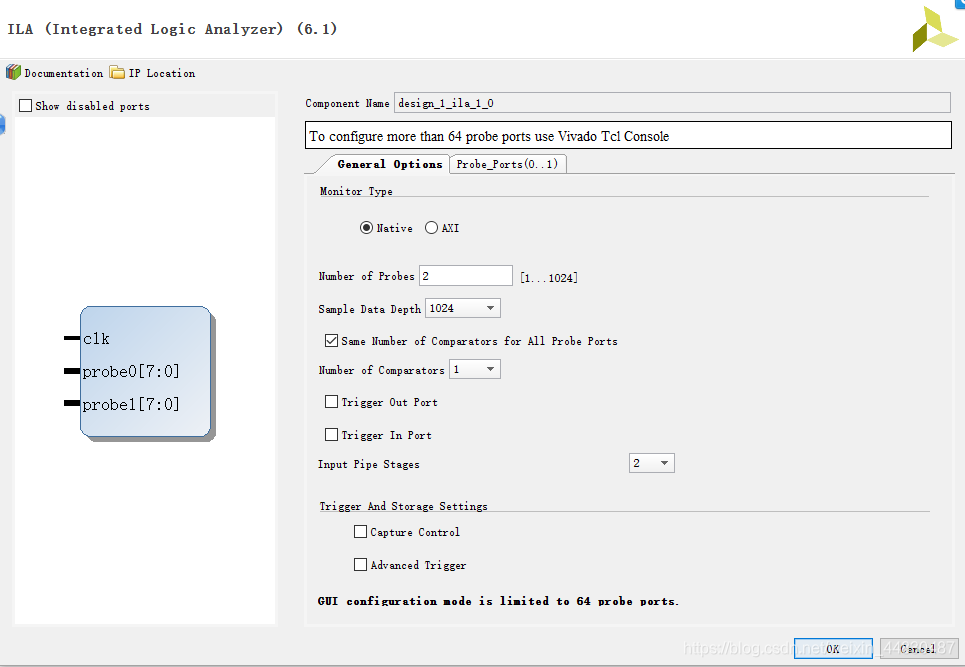

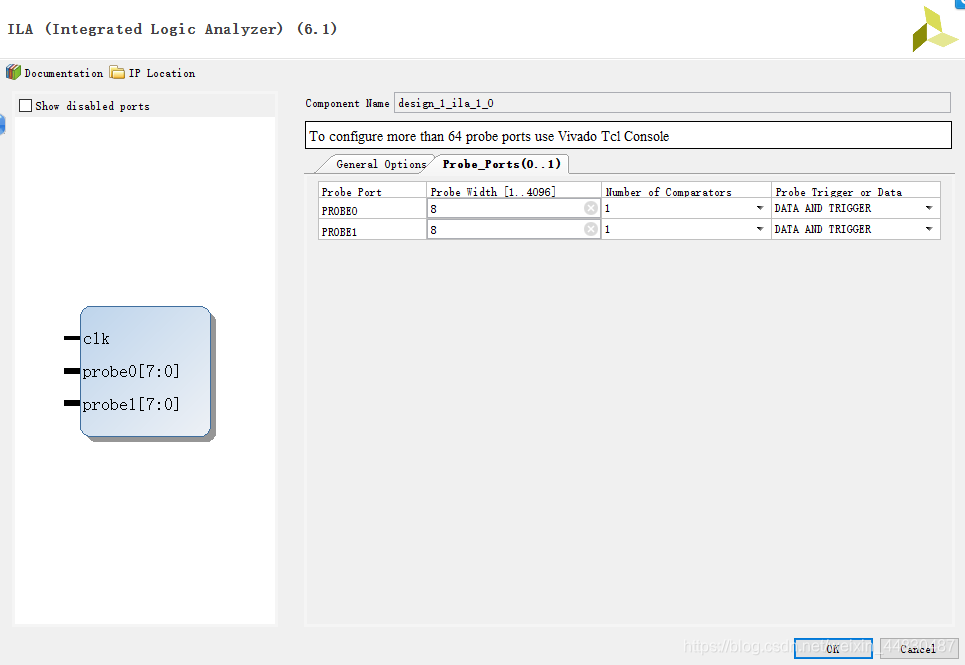

ILA1 设置:

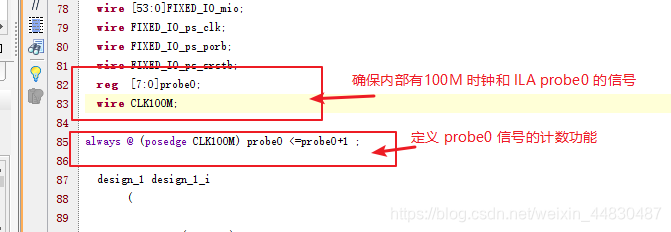

将ILA1 的一组端口与 AXI GPIO 的 GPIO 输出连接,一组接口引出端口,在

顶层文件中编写计数器,同时将 clk连接到 PS 的 FCLK_CLK0 并引出。

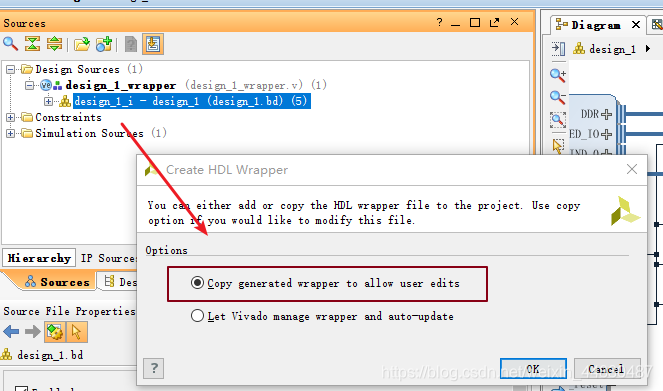

Step2 生成 block_design 的输出文件,产生 wrapper 文件,注意选择 Copy generated wrapper to allow user edits 选项。

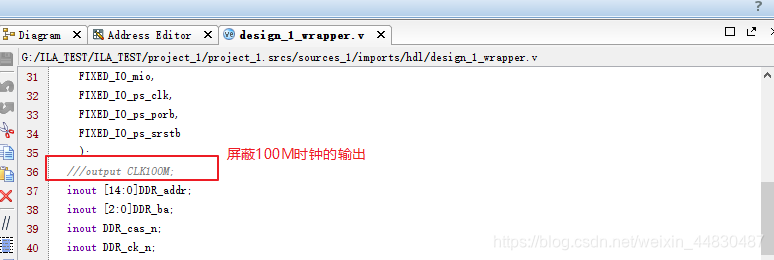

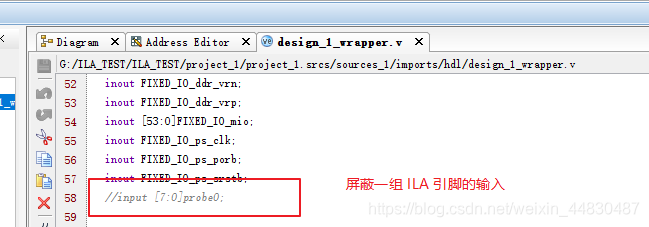

Step3 编辑 wrapper 文件,做以下修改:

Step4 生成 bitstream 文件,导出硬件,打开 SDK

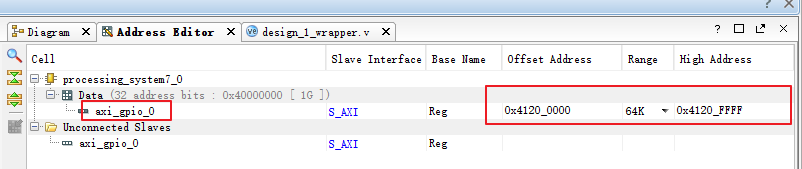

观察AXI GPIO 的地址

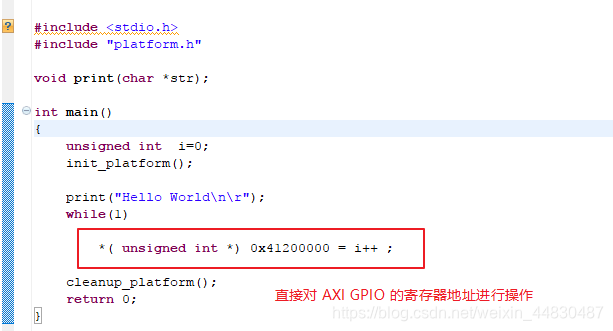

新建Application Project,修改 main 函数。

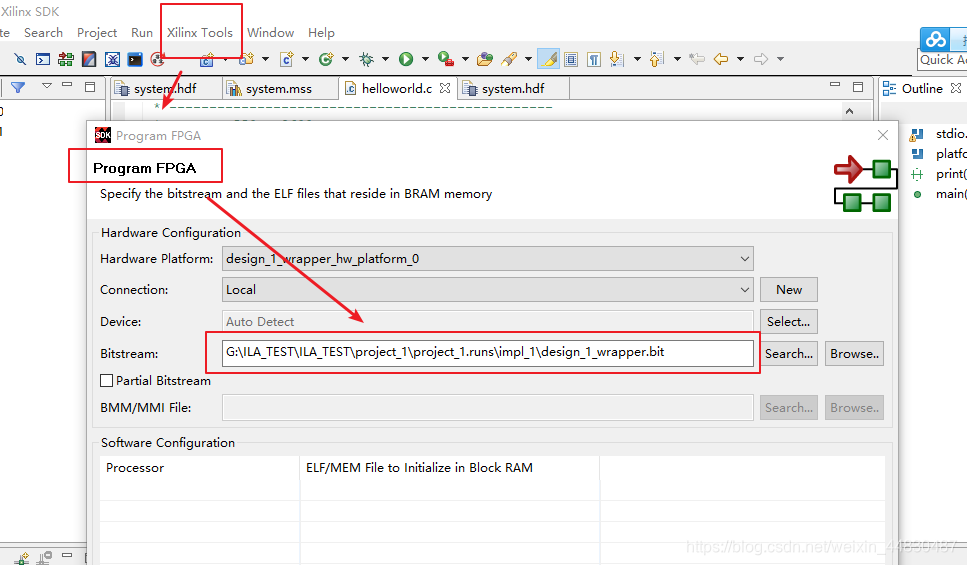

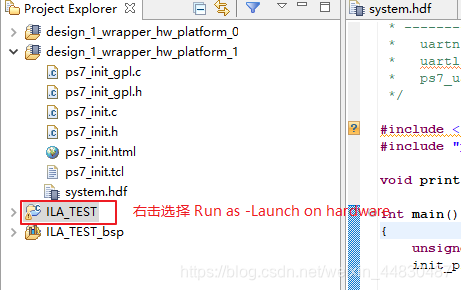

Step5 将程序下载到开发板运行观测 。

下载PS 代码到板上运行

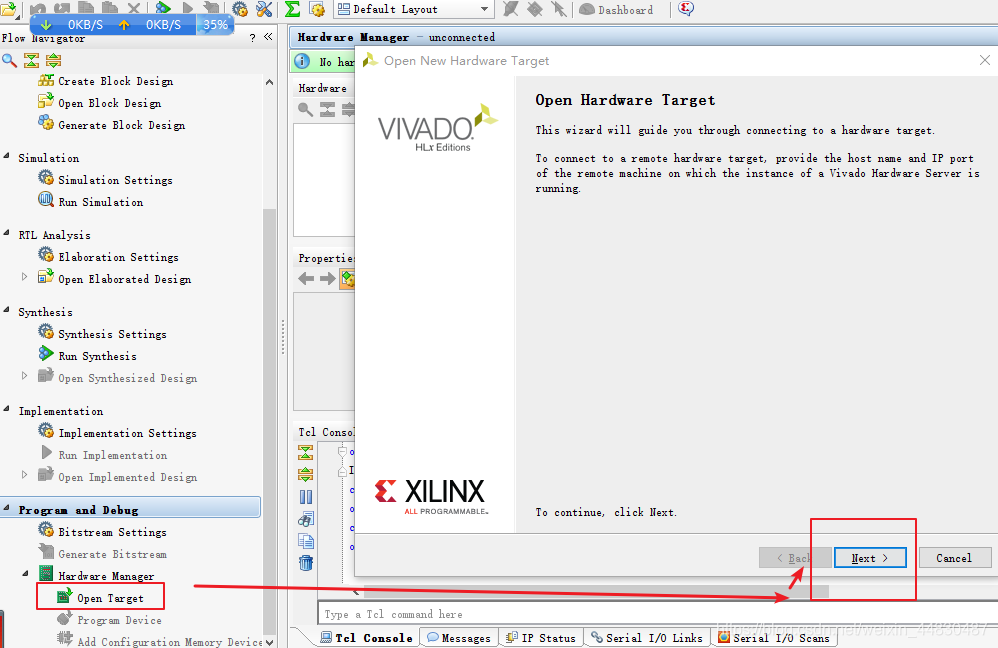

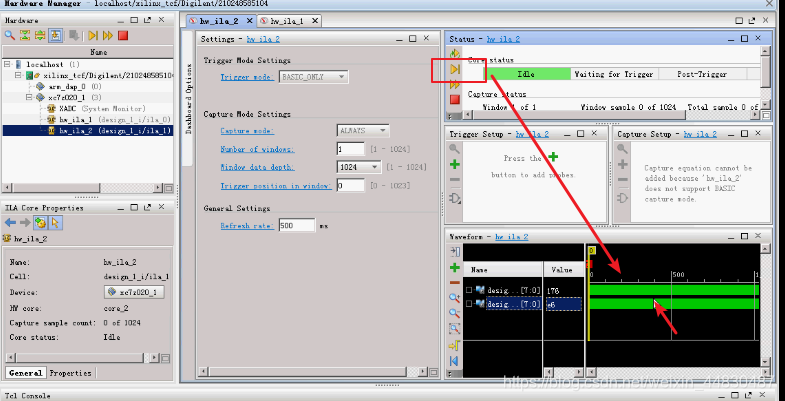

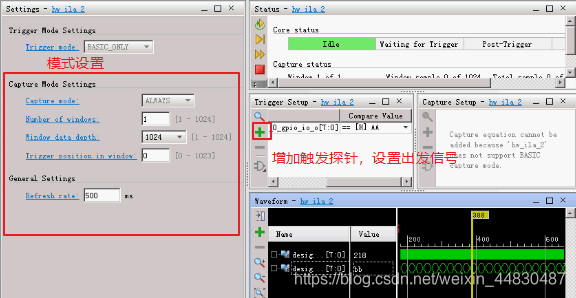

在vivado 中 open target ,打开 ILA 界面,分析 AXI 时序:

一定注意:要想扫描到

ILA必须在扫描 ILA之前有时钟输入给 ILA. 官方文档里

面提到的是有一个 FREE RUNNING的时钟。在纯 FPGA系统里面这需要一个外

部输入的 FPGA时钟,在 Z7系统中我们使用 PS输出的时钟做采样时候可以让

PS先运转起来就可以。

浙公网安备 33010602011771号

浙公网安备 33010602011771号