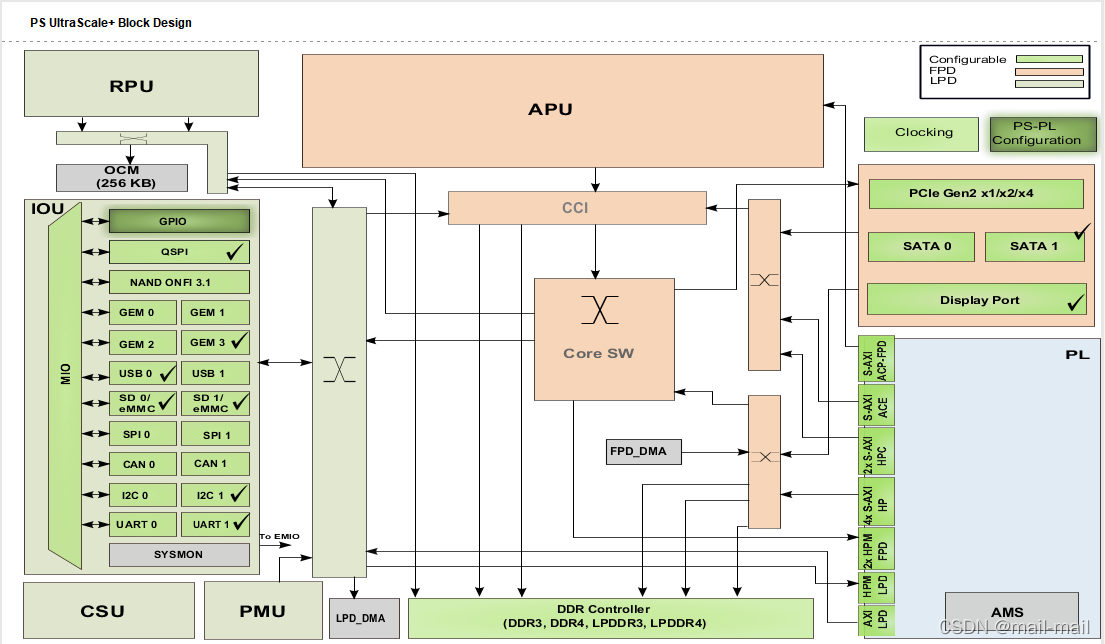

ZYNQ 中PS与PL交互的硬件接口

一、ZYNQ整体框图

二、细节图

三、PL与PS交互接口

1、接口介绍

在 ZYNQ 芯片内部用硬件实现了 AXI 总线协议,包括 12 个物理接口,分别为

S_AXI_HP{0:3}_FPD -------> (PL为master,PS为slave),

S_AXI_LPD -------> (PL为master,PS为slave),

S_AXI_ACE_FPD -------> (PL为master,PS为slave),

S_AXI_ACP_FPD -------> (PL为master,PS为slave),

S_AXI_HPC{0,1}_FPD -------> (PL为master,PS为slave),

M_AXI_HPM{0,1}_FPD -------> (PS为master,PL为slave),

M_AXI_HPM0_LPD 接口-------> (PS为master,PL为slave)。

2、接口功能说明:

S_AXI_HP{0:3}_FPD 接口,是高性能/带宽的 AXI4 标准的接口,总共有四个,PL 模块作为主设备连接。主要用于 PL 访问 PS 上的存储器(DDR 和 FPD Main Switch)。

S_AXI_LPD 接口,高性能端口,连接 PL 到 LPD。低延迟访问 OCM 和 TCM,访问 PS 端DDR。

S_AXI_HPC{0,1}_FPD 接口,连接 PL 到 FPD,可连接到 CCI,访问 L1 和 L2 Cache,由于通过 CCI,访问 DDR 控制器会有较大延迟。

M_AXI_HPM{0,1}_FPD 接口,高性能总线,PS 为 master,连接 FPD 到 PL,可用于CPU, DMA, PCIe 等从 PS 推送大量数据到 PL。

M_AXI_HPM0_LPD 接口,低延迟接口总线,PS 为 master,连接 LPD 到 PL,可直接访问 PL 端的 BRAM,DDR 等,也经常用于配置 PL 端的寄存器。

只有 M_AXI_HPM{0,1}_FPD 和 M_AXI_HPM0_LPD 是 Master Port,即主机接口,其余都是 Slave Port(从机接口)。主机接口具有发起读写的权限,ARM 可以利用两个主机接口主动访问 PL 逻辑,其实就是把 PL 映射到某个地址,读写 PL 寄存器如同在读写自己的存储器。

其余从机接口就属于被动接口,接受来自 PL 的读写,逆来顺受。在 PS 与 PL 互联应用,用的最多的接口为 S_AXI_HP{0:3}_FPD、M_AXI_HPM{0,1}_FPD 和 M_AXI_HPM0_LPD。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· 没有Manus邀请码?试试免邀请码的MGX或者开源的OpenManus吧

· 园子的第一款AI主题卫衣上架——"HELLO! HOW CAN I ASSIST YOU TODAY

· 【自荐】一款简洁、开源的在线白板工具 Drawnix