ZYNQ接口分析

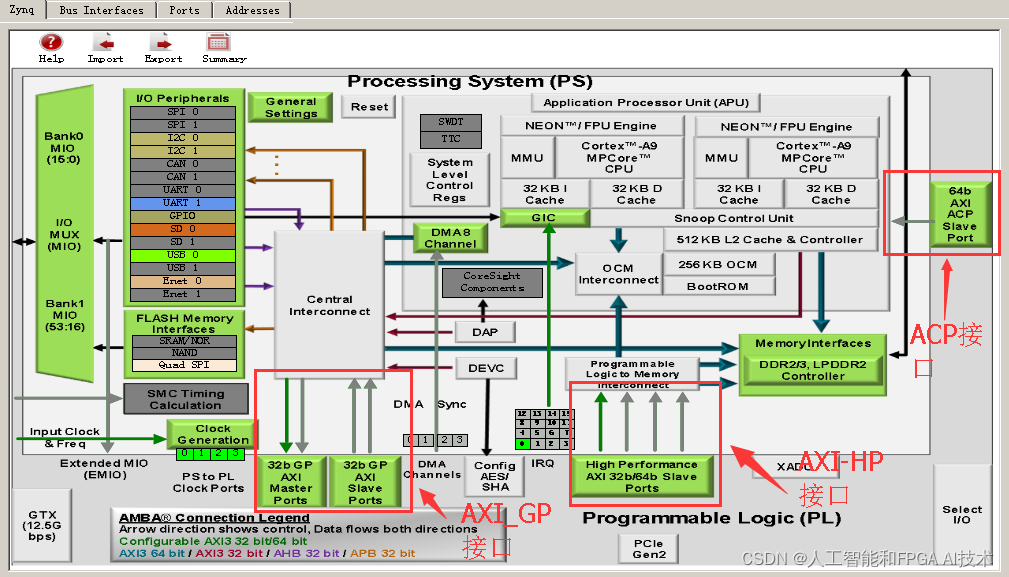

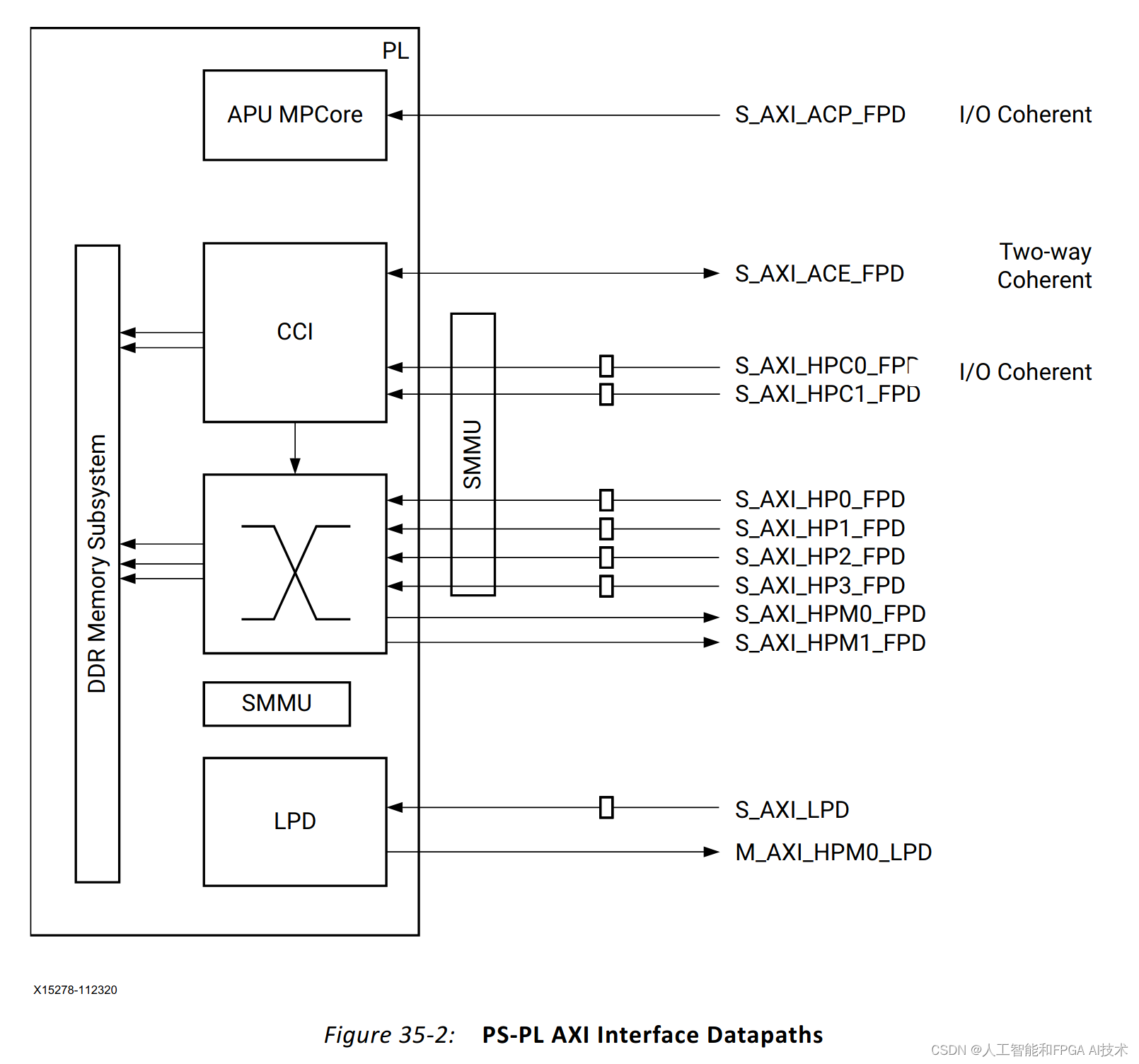

PS整体互连框图

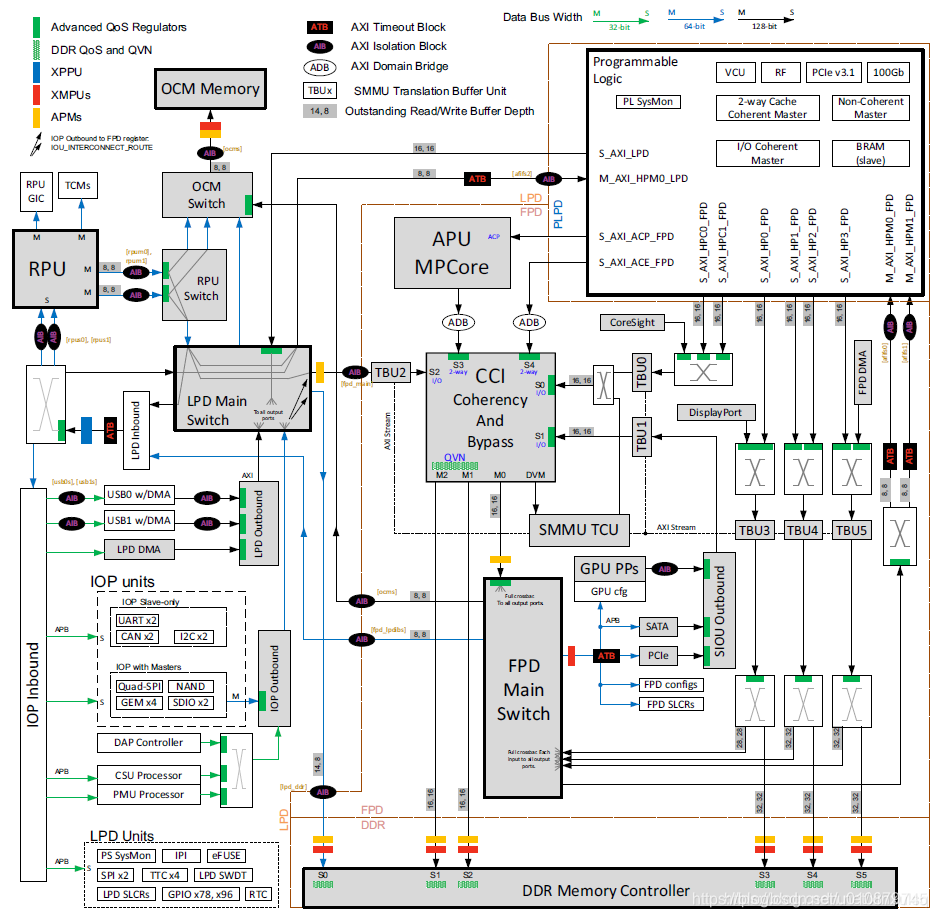

(1)S_AXI_HPC[0:1]_FPD和S_AXI_HP[0:3]_FPD:可以被PL端AXI主口访问的高性能AXI从口

(2)M_AXI_HPM0/1_FPD:低延迟的可以访问PL端AXI从口的AXI主口

(3)S_AXI_ACE_FPD:可以被PL端AXI主口访问的双向AXI一致性扩展口

(4)S_AXI_ACP_FPD:可以被PL端AXI主口访问的缓存一致性加速从口

(5)S_AXI_LDP:低功耗域内可以被PL端AXI主口访问的AXI从口

(6)M_AXI_HPM0_LPD:低功耗域内可以访问PL端AXI从口的AXI主口

(98条消息) ZYNQ入门(一)-AXI总线_今日你学左米啊-CSDN博客_s_axi_hp zynq https://blog.csdn.net/weixin_38071135/article/details/81009045

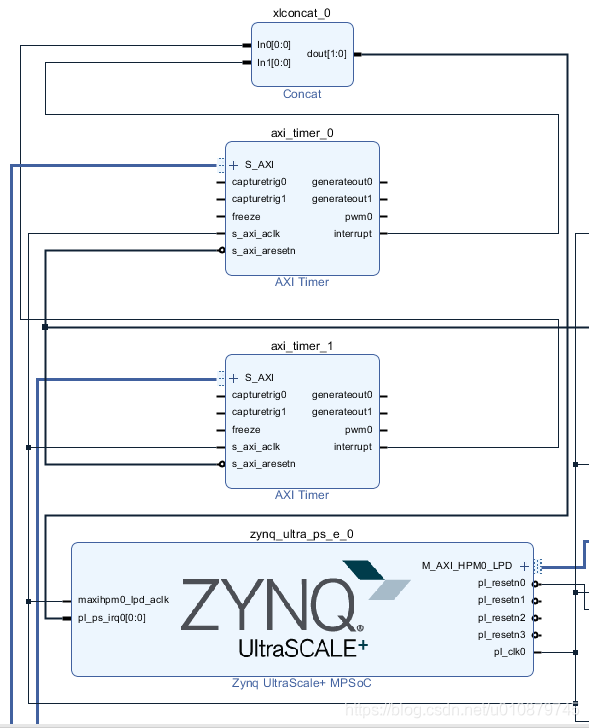

Concat IP实现总线自动匹配,这里实现多个中断信号与CPU的连接

FPGA系列之“Zynq MPSoC PS-PL AXI Interfaces” | 电子创新网赛灵思社区 http://xilinx.eetrend.com/content/2020/100047405.html

FPD Main Switch

128位的FPD主开关是FPD主机和LPD从机(包括OCM和TCM)的top互连中的一个开关。该开关的主要作用为:(1)提供到OCM的直接路径(绕过LPD互连),可以使延迟最小并提高FPD到OCM的吞吐量(2)提供了一个单独的路径来访问FPD主机的LPD外设寄存器。

(2条消息)【Zynq UltraScale+ MPSoC解密学习10】Zynq UltraScale+的PS互连_嵌入式_xinxulsq的博客-CSDN博客 https://blog.csdn.net/xinxulsq/article/details/103313920

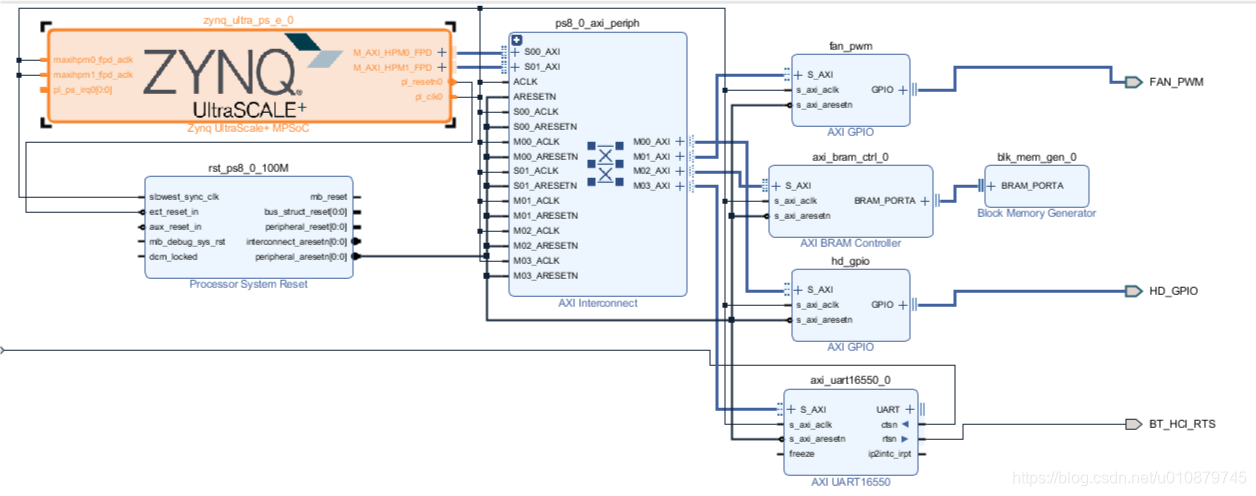

有人说,自动生成工程时,有可能将所有axi-lite连接到了zynq_us的m_axi_hpm0_lpd上,好像默认lpd不能用,需要开启时钟、电源?还是什么使能信号才可以用,所以会导致sdk中的例子不能直接访问pl上的外设,并导致cpu挂死。可以将lpd改为fpd,这样应该就没问题了。

是否是这个原因,未确认,还有可能是“ID转换”无法实现,APU无法访问m_axi_hpm0_lpd。

(2条消息)2. ZCU102 HDMI Demo【PCIE视频传输】_运维_vacajk的博客-CSDN博客 https://blog.csdn.net/vacajk/article/details/78970533?utm_source=distribute.pc_relevant.none-task

《pg201-zynq-ultrascale-plus-processing-system.pdf》 Page 11

AXI4 I/O Compliant Interfaces

Following are the AMBA® AXI4 compliant interfaces:

• Three PS General Purpose Master interfaces user configurable as 32, 64, and 128 bits in

width. The default width is 128.

• Seven PL General Purpose Master interfaces user configurable as 32, 64, and 128 bits in

width. The default width is 128.

• A 128-bit PL Master AXI coherency extension (ACE) interface for coherent I/O to A53 L1

and L2 cache systems

• A 128-bit PL Master ACP interface to support L2 cache allocation from PL masters.

Limited to 64-byte cache line transfers only

When the Zynq UltraScale+ MPSoC is used as an Endpoint, external DMA (like FPD or PL DMA units connected to S_AXI_HP[0:3]_FPD interfaces) can be used to exercise PCIe traffic.

Do not use PL DMA unit on S_AXI_HPC[0:1]_FPD, S_AXI_LPD, or any other masters (like LPD DMA) to exercise PCIe traffic because the shared path between the CCI and core switch can result in deadlock situations.

Exploring the PS-PL AXI interfaces on Zynq UltraScale+ MPSoC

https://j-marjanovic.io/exploring-the-ps-pl-axi-interfaces-on-zynq-ultrascale-mpsoc.html

dma-coherent

For use with ACP and HPC port, the u-dma-buffer needs to have the dma-coherent flag set. This is achieved with an entry in the device tree.

u-dma-buf

HP port requires no special configuration on the FPGA side, and the u-dma-buf needs to be opened with the O_SYNC flag.

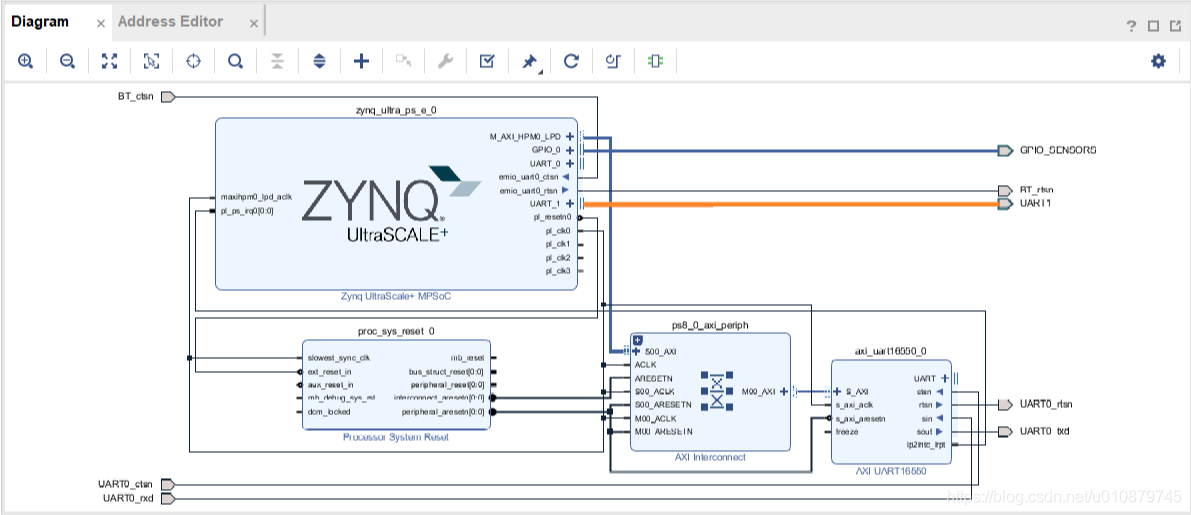

下图中有两个地方写错了,M_AXI_HPM

High-Performance interface

This interface connects directly to the DDR Memory Subsystem and completely bypasses the Cache Coherent Interconnect and the APU. According to UG1085, this interface is ideal for large datasets. The software needs to bypass the cache when accessing the data.

High-Performance Coherent interface

This interface is connected to a port on CCI-400 interconnect. When configured accordingly the memory transactions are communicated to the APU, providing tighter integration with software.

AR 69446 mentions that:

The HPC ports are preferable to the ACP port in most applications as they provide higher bandwidth and do not disturb the contents of the processor L2 cache.

Accelerator Coherency Port interface

Cortex-A53 TRM describes the ACP interface in the following way:

The ACP is provided to reduce software cache maintenance operations when sharing memory regions with other masters, and to allow other masters to allocate data into the L2 cache.

According to UG1085:

[…] ACP is optimal for medium-grain acceleration, such as a block-level crypto accelerator and video macro-block level processing.

登录

ALINX技术博客

官网:http://www.alinx.com 知乎:https://www.zhihu.com/org/alinx-26

【ZYNQ Ultrascale+ MPSOC FPGA教程】第一章 MPSoC芯片介绍

原创声明:

本原创教程由芯驿电子科技(上海)有限公司(ALINX)创作,版权归本公司所有,如需转载,需授权并注明出处。

适用于板卡型号:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

简介

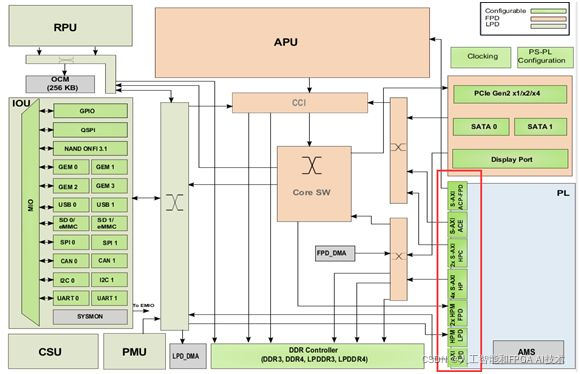

Zynq UltraScale+ MPSoC系列是Xilinx第二代Zynq平台。其亮点在于FPGA里包含了完整的ARM处理子系统(PS),包含了四核Cortex-A53处理器或双核Cortex-A53加双核Cortex-R5处理器,整个处理器的搭建都以处理器为中心,而且处理器子系统中集成了内存控制器和大量的外设,使处理器核在Zynq中完全独立于可编程逻辑单元,也就是说如果暂时没有用到可编程逻辑单元部分(PL), ARM处理器的子系统也可以独立工作,这与以前的FPGA有本质区别,其是以处理器为中心的。

Zynq就是两大功能块,PS 部分和 PL部分,说白了,就是ARM的SOC部分,和FPGA部分。其中,PS集成了APU ARM Cortex™-A53处理器,RPU Cortex-R5处理器,AMBA®互连,内部存储器(OCM),外部存储器接口(DDR Controller)和外设(IOU)。这些外设(IOU)主要包括USB总线接口,以太网接口,SD/eMMC接口,I2C总线接口,CAN总线接口,UART接口,GPIO等。高速接口如PCIe,SATA,Display Port。

ZYNQ MPSoC芯片的总体框图

PS: 处理系统(Processing System) , 就是与FPGA无关的ARM的SoC的部分。

PL: 可编程逻辑 (Progarmmable Logic), 就是FPGA部分。

1.1 PS和PL互联技术

ZYNQ作为将高性能ARM Cortex-A53系列处理器与高性能FPGA在单芯片内紧密结合的产品,为了实现ARM处理器和FPGA之间的高速通信和数据交互,发挥ARM处理器和FPGA的性能优势,需要设计高效的片内高性能处理器与FPGA之间的互联通路。因此,如何设计高效的PL和PS数据交互通路是ZYNQ芯片设计的重中之重,也是产品设计的成败关键之一。本节,我们就将主要介绍PS和PL的连接,让用户了解PS和PL之间连接的技术。

其实,在具体设计中我们往往不需要在连接这个地方做太多工作,我们加入IP核以后,系统会自动使用AXI接口将我们的IP核与处理器连接起来,我们只需要再做一点补充就可以了。

AXI全称Advanced eXtensible Interface,是Xilinx从6系列的FPGA开始引入的一个接口协议,主要描述了主设备和从设备之间的数据传输方式。在ZYNQ中继续使用,版本是AXI4,所以我们经常会看到AXI4.0,ZYNQ内部设备都有AXI接口。其实AXI就是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)的一个部分,是一种高性能、高带宽、低延迟的片内总线,也用来替代以前的AHB和APB总线。第一个版本的AXI(AXI3)包含在2003年发布的AMBA3.0中,AXI的第二个版本AXI(AXI4)包含在2010年发布的AMBA 4.0之中。

AXI协议主要描述了主设备和从设备之间的数据传输方式,主设备和从设备之间通过握手信号建立连接。当从设备准备好接收数据时,会发出READY信号。当主设备的数据准备好时,会发出和维持VALID信号,表示数据有效。数据只有在VALID和READY信号都有效的时候才开始传输。当这两个信号持续保持有效,主设备会继续传输下一个数据。主设备可以撤销VALID信号,或者从设备撤销READY信号终止传输。AXI的协议如图,T2时,从设备的READY信号有效,T3时主设备的VILID信号有效,数据传输开始。

AXI握手时序图

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,通过表5-1,我们可以看到这三种AXI接口的特性。

接口协议 特性 应用场合

AXI4-Lite 地址/单数据传输 低速外设或控制

AXI4 地址/突发数据传输 地址的批量传输

AXI4-Stream 仅传输数据,突发传输 数据流和媒体流传输

AXI4-Lite:

具有轻量级,结构简单的特点,适合小批量数据、简单控制场合。不支持批量传输,读写时一次只能读写一个字(32bit)。主要用于访问一些低速外设和外设的控制。

AXI4:

接口和AXI-Lite差不多,只是增加了一项功能就是批量传输,可以连续对一片地址进行一次性读写。也就是说具有数据读写的burst功能。

上面两种均采用内存映射控制方式,即ARM将用户自定义IP编入某一地址进行访问,读写时就像在读写自己的片内RAM,编程也很方便,开发难度较低。代价就是资源占用过多,需要额外的读地址线、写地址线、读数据线、写数据线、写应答线这些信号线。

AXI4-Stream:

这是一种连续流接口,不需要地址线(很像FIFO,一直读或一直写就行)。对于这类IP,ARM不能通过上面的内存映射方式控制(FIFO根本没有地址的概念),必须有一个转换装置,例如AXI-DMA模块来实现内存映射到流式接口的转换。AXI-Stream适用的场合有很多:视频流处理;通信协议转换;数字信号处理;无线通信等。其本质都是针对数值流构建的数据通路,从信源(例如ARM内存、DMA、无线接收前端等)到信宿(例如HDMI显示器、高速AD音频输出,等)构建起连续的数据流。这种接口适合做实时信号处理。

AXI4和AXI4-Lite接口包含5个不同的通道:

Read Address Channel

Write Address Channel

Read Data Channel

Write Data Channel

Write Response Channel

其中每个通道都是一个独立的AXI握手协议。下面两个图分别显示了读和写的模型:

AXI读数据通道AXI写数据通道

在ZYNQ芯片内部用硬件实现了AXI总线协议,包括12个物理接口,分别为S_AXI_HP{0:3}_FPD,S_AXI_LPD,S_AXI_ACE_FPD,S_AXI_ACP_FPD,S_AXI_HPC{0,1}_FPD,M_AXI_HPM{0,1}_FPD,M_AXI_HPM0_LPD接口。

S_AXI_HP{0:3}_FPD接口,是高性能/带宽的AXI4标准的接口,总共有四个,PL模块作为主设备连接。主要用于PL访问PS上的存储器(DDR和FPD Main Switch)

S_AXI_LPD接口,高性能端口,连接PL到LPD。低延迟访问OCM和TCM,访问PS端DDR。

S_AXI_HPC{0,1}_FPD接口,连接PL到FPD,可连接到CCI,访问L1和L2 Cache,由于通过CCI,访问DDR控制器会有较大延迟。

M_AXI_HPM{0,1}_FPD接口,高性能总线,PS为master,连接FPD到PL,可用于CPU, DMA, PCIe等从PS推送大量数据到PL。

M_AXI_HPM0_LPD接口,低延迟接口总线,PS为master,连接LPD到PL,可直接访问PL端的BRAM,DDR等,也经常用于配置PL端的寄存器。

浙公网安备 33010602011771号

浙公网安备 33010602011771号