zynq器件时钟

目录

前言

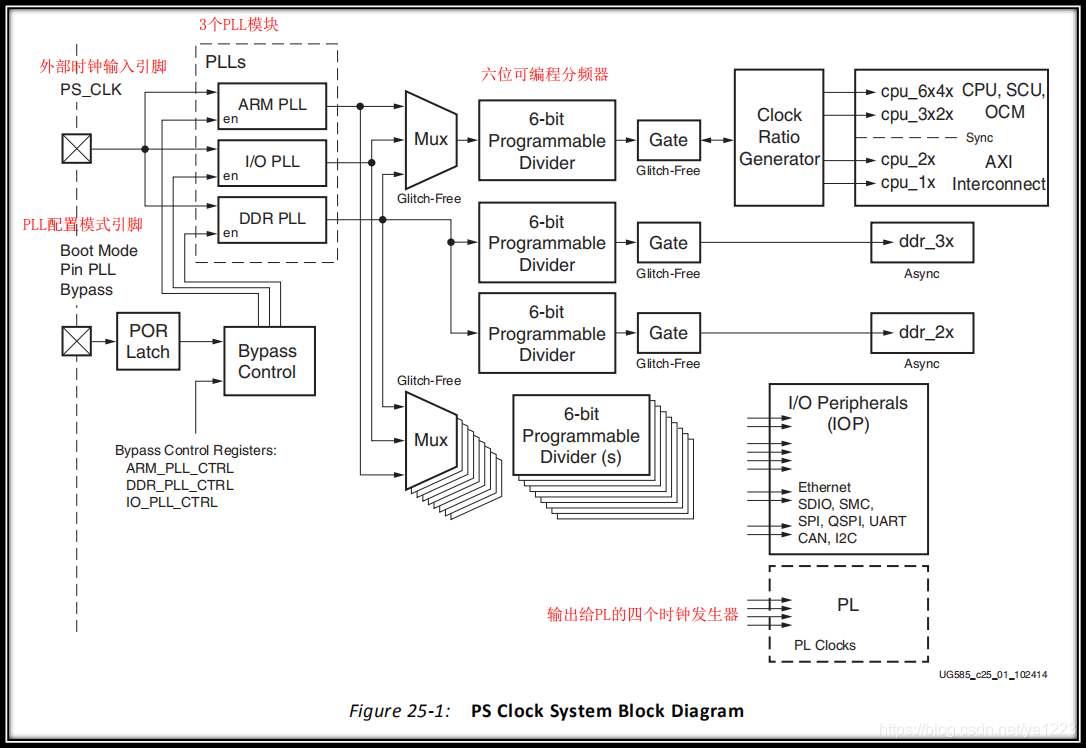

Zynq器件的时钟子系统是PS(ARMCortex-A9)系统的一个集成部分,本文就ZYNQ器件的时钟子系统作简单描述,官方详细描述请参考附件链接。

参考博客:

https://blog.csdn.net/Franceshaa/article/details/78663213

1.系统PLL介绍

PS时钟子系统产生的所有时钟都源自三个可编程的PLL锁相环之一,这三个PLL锁相环分别为:ARM PLL、DDRPLL、I/O

PLL,每个PLL分别和CPU、DDR、外设系统时钟有着松散地联系,时钟子系统的框图如下图示(源于《UG585 - Zynq-7000

SoC Technical Reference Manual (ver1.12.2)-技术参考手册.pdf》中第25节):

三个PLL锁相环特性如下:

三个PLL使用同一个外部基准时钟输入引脚

ARM PLL:CPU时钟和互连(interconnect)的通用时钟源。

DDR PLL:DDR DRAM控制器和AXI_HP接口的通用时钟源。

I/O PLL:I/O外设的通用时钟源。

三个PLL具有独立的旁路模式,并且可以进行独立的输出频率编程;同时,三个PLL公用VCO电压。

2.时钟使用模式

(1)正常操作情况:

PLL锁相环是使能的,时钟的产生过程如下:

外部PS_CLK时钟引脚——>PLLs先进行倍频处理——>时钟生成器在进行进一步的倍频或是分频处理——>输出给系统的各部分组件。

(2)bypass旁路模式:

PLL锁相环不使能,PS_CLK时钟脚的信号不经过PLL,各时钟产生如下:

外部PS_CLK时钟引脚——>时钟生成器在进行进一步的倍频或是分频处理——>输出给系统的各部分组件。

注意:当PS_POR reset上电复位信号释放时,锁相环旁路启动模式引脚被采样而决定是否使用旁路模式或是使能三个PLL锁环。旁路模式下,系统的运行速度明显低于正常模式,但对于低功耗应用程序和调试模式非常有用。

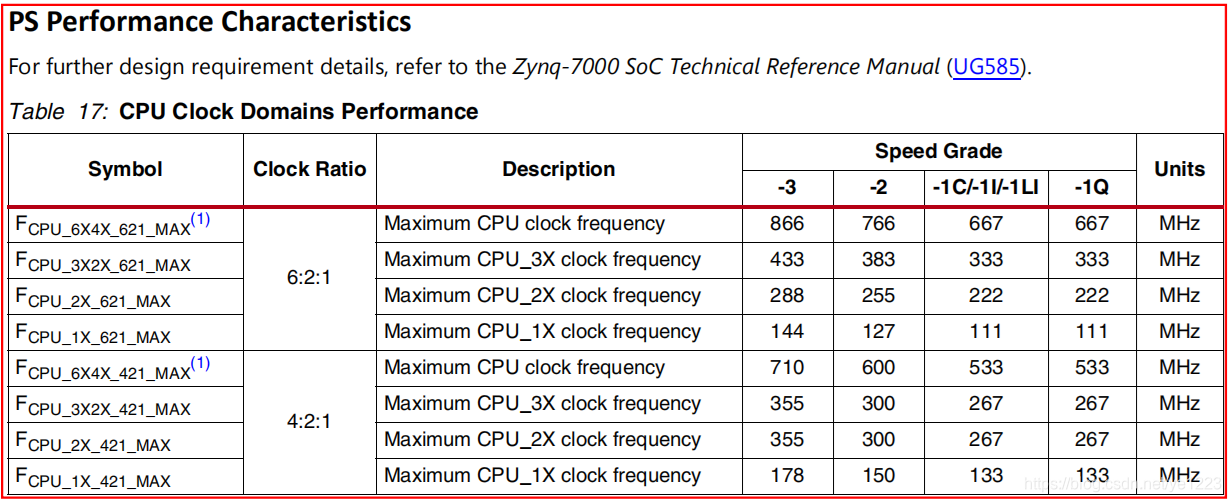

在系统启动后,用户代码执行后就可以用软件分别控制每个PLL锁相环的旁路模式和输出频率。要正确设置参数使PLL锁相环的输出频率的大小满足DATA SHEET要求,如下图示:

根据Zynq器件的DATA SHEET要求,PS_CLK时钟信号最低频率为30MHz, 最高频率60MHz, 占空比要求在40%~60%之间。、

锁相环输出的最小频率为780MHz,最大频率为1600MHz~2000MHz。

注意从减少功耗的角度考虑,使用锁相环时应在满足时钟要求的条件下尽可能降低锁相环的输出频率。比如,如果所有的时钟

可以由DDR PLL产生,那就不使能另外两个锁相环ARM PLL和I/O PLL可以获得比较低的功耗。

时钟产生路径还包括无毛刺的选择器和时钟门控电路以支持动态的时钟控制。

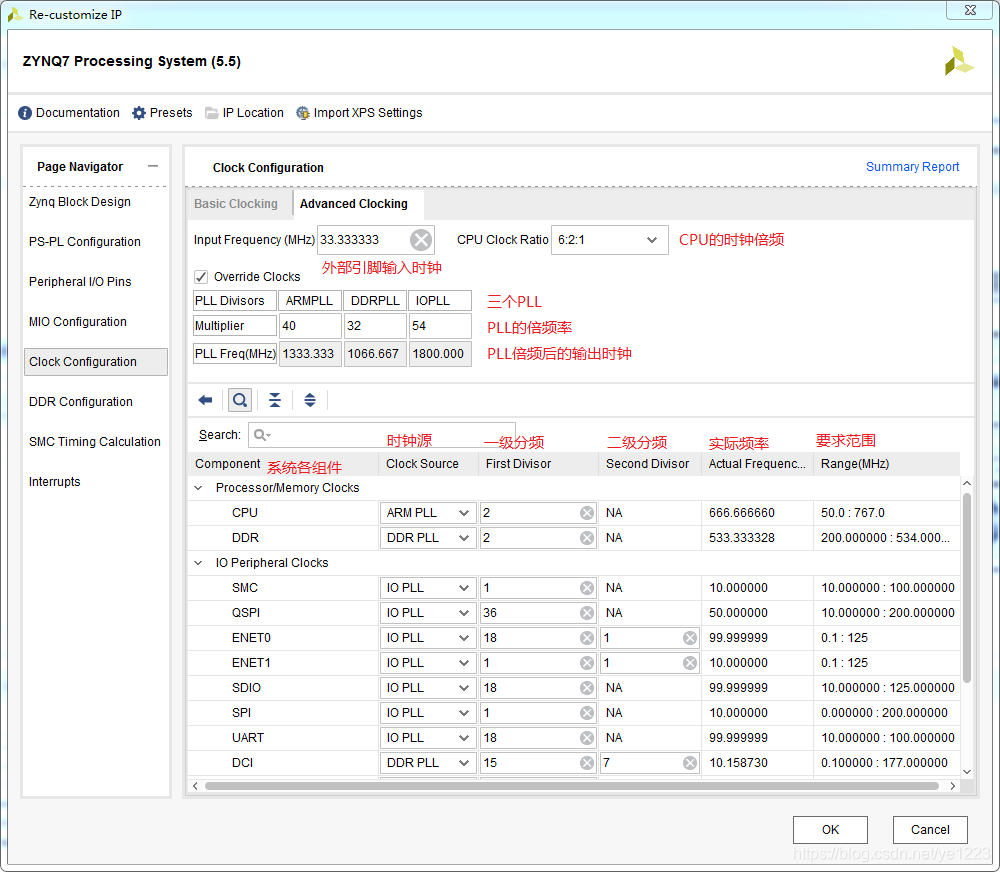

举例,ZYNQ7z202clg400-2器件的vivado中的配置如下(速度等级为-2,cpu时钟频率最高可配置为766M):

3.时钟分支(Clock Branches)

特性如下:

6比特的可编程序的频率除法器

大部分的时钟电路可以动态开关

有四个PL(FPGA)的时钟发生器

4.系统时钟域

由于时钟子系统是PS(ARM Cortex-A9)系统的一部分,但系统复位时,所有控制时钟模块的寄存器就重置为系统复位值。

系统的时钟域分布如下图示:

上图中,

CPU_6x时钟域主要用作CPU时钟,CPU互连和OCM仲裁。

CPU_2x时钟域主要用作L2Cache,I/O外设的AXI互连和OCM RAM。

CPU_1x时钟域主要用作I/O外设的AHB和APB总线互连。

DDR_3x时钟域主要用作DDR存储控制器。

DDR_2x时钟域主要用作访问PL(AXI_HP{0:3})的高性能的AXI总线互连。

最后提下PL的时钟,前面提到Zynq器 件的时钟子系统有四个时钟发生器产生时钟连到FPGA,但FPGA可以有自己的时钟管理和分发特性,仅仅是把这四个PS时钟子系统过来的信号作为一个可选 的时钟输入源而已,这点等同于普通地XILINX 7系统FPGA。

5.CPU CLOCK

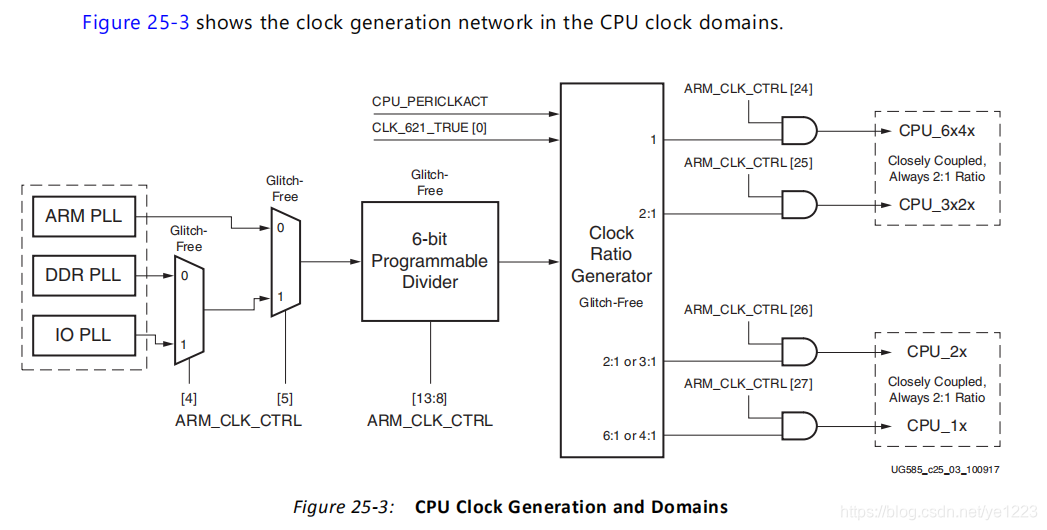

下图显示CPU时钟域中的时钟生成网络:

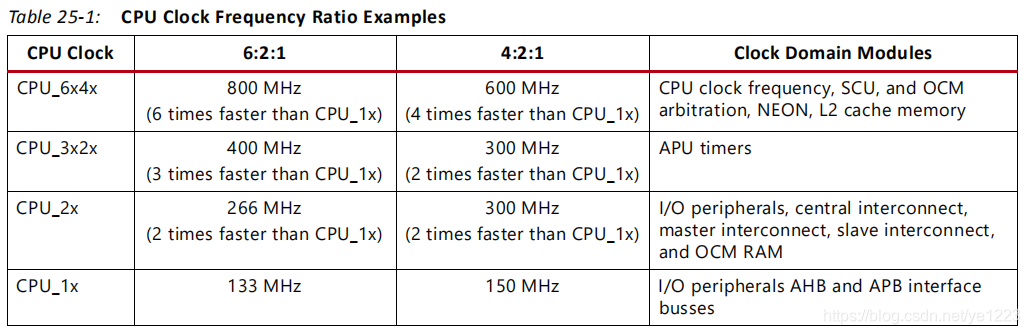

CPU时钟域由四个独立的时钟组成:CPU_6x4x、CPU_3x2x、CPU_2x和CPU_1x。

这四个时钟是根据它们的频率命名的,它们之间的关系是两个比率之一:6:3:2:1或4:2:2:1(缩写为6:2:1和4:2:

1)。这两种比率模式的选择由:CLK_621_TRUE [0]决定。。表25-1显示了在每个时钟域中工作的这些模式和模块的频率示例.(请参阅zynq-7000 soc数据手册。)

查看数据手册,有如下的要求:

根据zynq器件具有三种速度等级:-3、-2和-1,其中-3速度等级最高。

附录

《UG585 - Zynq-7000 SoC Technical Reference Manual (ver1.12.2)-技术参考手册.pdf》下载链接:

https://download.csdn.net/download/ye1223/10811782

浙公网安备 33010602011771号

浙公网安备 33010602011771号