GT基础知识

1、GT基础知识

SATA 接口只有几根线为什么那么快?连上网线显示的10Gbps(万兆网)是不是很令人兴奋!没错,他们都用了高速GTX技术、GTX全称Gigabit transceiver,是为了满足高速、实时传输而生的技术。传统的并行传输技术存在抗干扰能力低,同步能力差,传输速度低和信号质量差等问题。GTX目前的线速度范围是1Gbps - 12Gbps,有效负载范围0.8Gbps - 10Gbps。目前GTX已经应用于光纤通道(FC),PCIE,Rapid io,串行SATA ,千兆以太网,万兆以太网等。

GTX收发器采用的是差分信号对数据进行传输,其中LVDS(Low voltage different signal )和CML(current mode logic)是常用的两种差分信号标准。差分信号因为线路上收到的噪声干扰几乎完全相同,在计算差值相减从而达到抵消的效果,这就使得差分信号抗干扰能力特别强,高速传输时不易出错。

除了差分信号外,GTX采用自同步技术来解决时钟问题。目前常用的同步方式有:系统同步、源同步、自同步。系统同步利用片外的晶振进行同步,由于板间线路的长度不一致,以及片内延迟不一致,在时钟速到提高时可能存在较大误差。源同步是在发送数据同时发送一个时钟副本,这种设计需要更多的时钟端口。自同步讲时钟包含在数据流中,从数据流中恢复时钟,不仅端口使用较少,而且不论是高速还是低速,时钟延迟和数据延迟都是一样的,可以保证采样的正确性。

自同步接口主要包含三个模块分别是并串转换、串并转换和时钟恢复。时钟恢复是利用锁相环(PLL)合成出一个与输入串行信号的时钟频率一致的时钟,供采集数据用。

GTX包含两大部分,PMA PCS。

PMA(物理媒介附加子层)主要功能是 : 串并\并串转换和模拟部分。提供高性能的串行接口,如预加重、均衡。

PCS(物理编码子层)主要是并行数字电路处理。数字流的编码/解码,8B\10B等。

2 GTX速度到底可以跑到多少

关于器件速度的问题首先找到 ds182->Kintex-7 FPGAs Data Sheet:DC and AC Switching Characteristics,可以自己对应的器件去找,不过这个在设计电路板器件选型的时候就应该考虑到,除非是买的开发部学习用。这里面包括所有的FPGA各个器件能跑到的最高频率和器件延时,建立时间,保持时间等,对高速设计有很大的参考价值。找到GTX Transceiver Switching Characteristics

可以看到,虽然K7系列GTX最高可以跑到12.5Gbps,但这跟速度等级和封装都有关系,是在-3的速度等级,FF封装下才有的最高速度12.5Gbps。而现在手头的芯片型号是K7480TFFG901-1,所以最高支持8.0Gbps。其实这在配置IP核的时候就会发现了,线速范围是(0.5-8.0)。所以IP核都是严格和工程的器件相关联的,这点Vivado越做越好了。

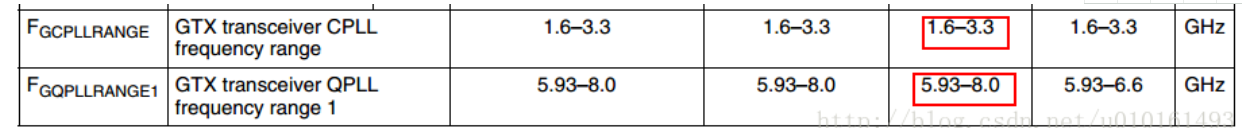

另外,速度还和CPLL QPLL 有关,以前一直以为CPLL 和QPLL 的区别就是在用时钟共享的时候会有区别。

3. GTX 硬件结构

下面图均以325T为例

当整个芯片多个GTX被使用时,需要合理的分布GTX与时钟输入。从一个Quad输入的时钟往上只能给相邻的一个Quad提供时钟,往下也只能给相邻的一个Quad提供时钟输入,最多只能驱动三个Quad,当整个芯片多个GTX使用到同样的参考时钟输入时,合理的分布时钟输入可以节省需要的时钟数量,并为时钟的提供冗余设计。因此,基本的原则是同一个物理接口的几个GTX放在一起,由同一个参考时钟作为时钟输入;不同物理接口的GTX如果在同一个参考时钟的驱动覆盖范围内,可以采用同一个参考时钟输入。有条件的情况下,可以做时钟备份;当一个时钟可以覆盖更多个GTX的时候,考虑到时钟驱动能力的不确定性,为留有更多余量,没必要使用到极限(一个时钟驱动12个GTX)(比如我在调试aurora的时候,一个参考时钟输入,驱动3个bank,理论上是没问题的,但是编译时报错。报错原因不是一个qpll不能驱动3个bank,而是上图中每个qpll都包含了一个common,这个common模块是不能共享的。aurora在使用为从核模式,共享逻辑在example下,自动的屏蔽掉了common逻辑,导致其他两个bank的qpll里面没有common。修改IP 源码,把common模块添加到QPLL里,问题得到解决。其实,最好的办法是,每个bank都预留一个参考时钟)。另外在V5的GTP中,关于多个GTP共用同一个参考时钟输入,要求在这个输入时钟的时钟链上,每一个GTP都被使用(即使不需要,也要例化),不允许共用同一个参考时钟的两个GTP中间有一个没有使用的GTP

GTX整体功能结构

4. 7 Series FPGAs TransceiversWizard IP 核介绍

1)选择shared logic选项,最好选include shared logic in example design

2)

-------------------------------------- 下面摘自其他文章,内部参数和上图不匹配,解析具有参考价值-----------------

先是协议,最简单的strat from cratch,就是没有协议。然后是线速,可以看到范围是(0.5-8.0)。参考时钟,这个可以根据需要选个合适的。软件都根据你的线速把参考时钟的可选项计算好了。接收端同样设置,当然可以不一样的。这是全双工,收发链路没有什么关系,也可以关掉其中一个Tx off 或Rx off。然后是PLL选择,到底选哪个呢?根据时钟频率选择

然后是比较重要的,选择用哪个收发器,这当然不是拍脑袋决定的,跟设计有关,可以查找原理图

比如说这样的,然后去查手册UG476-> 7 Series FPGAsGTX/GTH Transceivers 找到 Placement Information by Package如下

这样就知道用的是X0Y8,输入时钟在上面的原理图可以找到,是同一组的clk0。

3)

4)

5)

可选端口其实有的挺有用的,增加了可控性,比如说环回控制,LOOPBACK。顺便说一下内部环回有四种,

1.“000”:正常模式不环回

2.“001”:近端PCS环回

3.“010”:近端PMA环回

4.“100”:远端PMA环回

5.“110”:远端PCS环回)

6)

接下来是通道绑定和时钟校正。通道绑定的作用是把多个物理通道对齐,绑定成一个的逻辑通道。其实就是用FIFO消除通道间的延时不确定性。由于只有一个通道,没有绑定可言。

7)检查一下对不对

5. 调用例程

-

-

gtwizard_0 u_gtwizard_0

-

(

-

.soft_reset_tx_in(rst | reg_gtp_rst[0]),

-

.soft_reset_rx_in(rst | reg_gtp_rst[1]),

-

.dont_reset_on_data_error_in(1'b0),

-

.q0_clk1_gtrefclk_pad_n_in(gtp_refclk_n),

-

.q0_clk1_gtrefclk_pad_p_in(gtp_refclk_p),

-

.gt0_tx_mmcm_lock_out( ),

-

.gt0_rx_mmcm_lock_out( ),

-

.gt0_tx_fsm_reset_done_out( ),

-

.gt0_rx_fsm_reset_done_out( ),

-

.gt0_data_valid_in(1'b1),

-

.gt1_tx_mmcm_lock_out( ),

-

.gt1_rx_mmcm_lock_out( ),

-

.gt1_tx_fsm_reset_done_out( ),

-

.gt1_rx_fsm_reset_done_out( ),

-

.gt1_data_valid_in(1'b1),

-

.gt2_tx_mmcm_lock_out( ),

-

.gt2_rx_mmcm_lock_out( ),

-

.gt2_tx_fsm_reset_done_out( ),

-

.gt2_rx_fsm_reset_done_out( ),

-

.gt2_data_valid_in(1'b1),

-

.gt3_tx_mmcm_lock_out( ),

-

.gt3_rx_mmcm_lock_out( ),

-

.gt3_tx_fsm_reset_done_out( ),

-

.gt3_rx_fsm_reset_done_out(gt3_rx_fsm_reset_done_out),

-

.gt3_data_valid_in(1'b1),

-

-

.gt0_txusrclk_out( ),

-

.gt0_txusrclk2_out(gt0_txusrclk_out),

-

.gt0_rxusrclk_out( ),

-

.gt0_rxusrclk2_out(gt0_rxusrclk_out),

-

-

.gt1_txusrclk_out( ),

-

.gt1_txusrclk2_out(gt1_txusrclk_out),

-

.gt1_rxusrclk_out( ),

-

.gt1_rxusrclk2_out(gt1_rxusrclk_out),

-

-

.gt2_txusrclk_out( ),

-

.gt2_txusrclk2_out(gt2_txusrclk_out),

-

.gt2_rxusrclk_out( ),

-

.gt2_rxusrclk2_out(gt2_rxusrclk_out),

-

-

.gt3_txusrclk_out( ),

-

.gt3_txusrclk2_out(gt3_txusrclk_out),

-

.gt3_rxusrclk_out( ),

-

.gt3_rxusrclk2_out(gt3_rxusrclk_out),

-

//_________________________________________________________________________

-

//GT0 (X0Y0)

-

//____________________________CHANNEL PORTS________________________________

-

//------------------------------- CPLL Ports -------------------------------

-

.gt0_cpllfbclklost_out ( ), // output wire gt0_cpllfbclklost_out

-

.gt0_cplllock_out ( ), // output wire gt0_cplllock_out

-

.gt0_cpllreset_in (1'b0), // input wire gt0_cpllreset_in

-

//-------------------------- Channel - DRP Ports --------------------------

-

.gt0_drpaddr_in (9'd0), // input wire [8:0] gt0_drpaddr_in

-

.gt0_drpdi_in (16'd0), // input wire [15:0] gt0_drpdi_in

-

.gt0_drpdo_out ( ), // output wire [15:0] gt0_drpdo_out

-

.gt0_drpen_in (1'b0), // input wire gt0_drpen_in

-

.gt0_drprdy_out ( ), // output wire gt0_drprdy_out

-

.gt0_drpwe_in (1'b0), // input wire gt0_drpwe_in

-

//------------------------- Digital Monitor Ports --------------------------

-

.gt0_dmonitorout_out ( ), // output wire [7:0] gt0_dmonitorout_out

-

//----------------------------- Loopback Ports -----------------------------

-

.gt0_loopback_in (3'd0), // input wire [2:0] gt0_loopback_in

-

//------------------- RX Initialization and Reset Ports --------------------

-

.gt0_eyescanreset_in (1'b0), // input wire gt0_eyescanreset_in

-

.gt0_rxuserrdy_in (1'b1), // input wire gt0_rxuserrdy_in

-

//------------------------ RX Margin Analysis Ports ------------------------

-

.gt0_eyescandataerror_out ( ), // output wire gt0_eyescandataerror_out

-

.gt0_eyescantrigger_in (1'b0), // input wire gt0_eyescantrigger_in

-

//---------------- Receive Ports - FPGA RX interface Ports -----------------

-

.gt0_rxdata_out (gt0_rxdata_out), // output wire [31:0] gt0_rxdata_out

-

//----------------- Receive Ports - Pattern Checker Ports ------------------

-

.gt0_rxprbserr_out (gt0_rxprbserr_out), // output wire gt0_rxprbserr_out

-

.gt0_rxprbssel_in (3'b0), // input wire [2:0] gt0_rxprbssel_in

-

//----------------- Receive Ports - Pattern Checker ports ------------------

-

.gt0_rxprbscntreset_in (1'b0), // input wire gt0_rxprbscntreset_in

-

//---------------- Receive Ports - RX 8B/10B Decoder Ports -----------------

-

.gt0_rxdisperr_out (gt0_rxdisperr_out), // output wire [3:0] gt0_rxdisperr_out

-

.gt0_rxnotintable_out (gt0_rxnotintable_out), // output wire [3:0] gt0_rxnotintable_out

-

//------------------------- Receive Ports - RX AFE -------------------------

-

.gt0_gtxrxp_in (rx_serdout0_p), // input wire gt0_gtxrxp_in

-

//---------------------- Receive Ports - RX AFE Ports ----------------------

-

.gt0_gtxrxn_in (rx_serdout0_n), // input wire gt0_gtxrxn_in

-

//----------------- Receive Ports - RX Buffer Bypass Ports -----------------

-

.gt0_rxbufstatus_out ( ), // output wire [2:0] gt0_rxbufstatus_out

-

//------------ Receive Ports - RX Byte and Word Alignment Ports ------------

-

.gt0_rxbyterealign_out ( ), // output wire gt0_rxbyterealign_out

-

.gt0_rxmcommaalignen_in (gt0_rxmcommaalignen_in), // input wire gt0_rxmcommaalignen_in

-

.gt0_rxpcommaalignen_in (gt0_rxmcommaalignen_in), // input wire gt0_rxpcommaalignen_in

-

//------------------- Receive Ports - RX Equalizer Ports -------------------

-

.gt0_rxdfelpmreset_in (1'b0), // input wire gt0_rxdfelpmreset_in

-

.gt0_rxmonitorout_out ( ), // output wire [6:0] gt0_rxmonitorout_out

-

.gt0_rxmonitorsel_in (2'b0), // input wire [1:0] gt0_rxmonitorsel_in

-

//------------- Receive Ports - RX Fabric Output Control Ports -------------

-

.gt0_rxoutclkfabric_out ( ), // output wire gt0_rxoutclkfabric_out

-

//----------- Receive Ports - RX Initialization and Reset Ports ------------

-

.gt0_gtrxreset_in (1'b0), // input wire gt0_gtrxreset_in

-

.gt0_rxpmareset_in (1'b0), // input wire gt0_rxpmareset_in

-

//----------------- Receive Ports - RX8B/10B Decoder Ports -----------------

-

.gt0_rxchariscomma_out ( ), // output wire [3:0] gt0_rxchariscomma_out

-

.gt0_rxcharisk_out (gt0_rxcharisk_out), // output wire [3:0] gt0_rxcharisk_out

-

//------------ Receive Ports -RX Initialization and Reset Ports ------------

-

.gt0_rxresetdone_out (gt0_rxresetdone_out), // output wire gt0_rxresetdone_out

-

//------------------- TX Initialization and Reset Ports --------------------

-

.gt0_gttxreset_in (1'b0), // input wire gt0_gttxreset_in

-

.gt0_txuserrdy_in (1'b0), // input wire gt0_txuserrdy_in

-

//-------------------- Transmit Ports - TX Buffer Ports --------------------

-

.gt0_txbufstatus_out ( ), // output wire [1:0] gt0_txbufstatus_out

-

//---------------- Transmit Ports - TX Data Path interface -----------------

-

.gt0_txdata_in (gt0_txdata_in), // input wire [31:0] gt0_txdata_in

-

//-------------- Transmit Ports - TX Driver and OOB signaling --------------

-

.gt0_gtxtxn_out (tx_serdin0_n), // output wire gt0_gtxtxn_out

-

.gt0_gtxtxp_out (tx_serdin0_p), // output wire gt0_gtxtxp_out

-

//--------- Transmit Ports - TX Fabric Clock Output Control Ports ----------

-

.gt0_txoutclkfabric_out ( ), // output wire gt0_txoutclkfabric_out

-

.gt0_txoutclkpcs_out ( ), // output wire gt0_txoutclkpcs_out

-

//------------------- Transmit Ports - TX Gearbox Ports --------------------

-

.gt0_txcharisk_in (gt0_txcharisk_in), // input wire [3:0] gt0_txcharisk_in

-

//----------- Transmit Ports - TX Initialization and Reset Ports -----------

-

.gt0_txresetdone_out (gt0_txresetdone_out), // output wire gt0_txresetdone_out

-

//---------------- Transmit Ports - pattern Generator Ports ----------------

-

.gt0_txprbssel_in (3'b0), // input wire [2:0] gt0_txprbssel_in

-

-

//GT1 (X0Y1)

-

//____________________________CHANNEL PORTS________________________________

-

//------------------------------- CPLL Ports -------------------------------

-

.gt1_cpllfbclklost_out ( ), // output wire gt1_cpllfbclklost_out

-

.gt1_cplllock_out ( ), // output wire gt1_cplllock_out

-

.gt1_cpllreset_in (1'b0), // input wire gt1_cpllreset_in

-

//-------------------------- Channel - DRP Ports --------------------------

-

.gt1_drpaddr_in (9'd0), // input wire [8:0] gt1_drpaddr_in

-

.gt1_drpdi_in (16'd0), // input wire [15:0] gt1_drpdi_in

-

.gt1_drpdo_out ( ), // output wire [15:0] gt1_drpdo_out

-

.gt1_drpen_in (1'b0), // input wire gt1_drpen_in

-

.gt1_drprdy_out ( ), // output wire gt1_drprdy_out

-

.gt1_drpwe_in (1'b0), // input wire gt1_drpwe_in

-

//------------------------- Digital Monitor Ports --------------------------

-

.gt1_dmonitorout_out ( ), // output wire [7:0] gt1_dmonitorout_out

-

//----------------------------- Loopback Ports -----------------------------

-

.gt1_loopback_in (3'd0), // input wire [2:0] gt1_loopback_in

-

//------------------- RX Initialization and Reset Ports --------------------

-

.gt1_eyescanreset_in (1'b0), // input wire gt1_eyescanreset_in

-

.gt1_rxuserrdy_in (1'b1), // input wire gt1_rxuserrdy_in

-

//------------------------ RX Margin Analysis Ports ------------------------

-

.gt1_eyescandataerror_out ( ), // output wire gt1_eyescandataerror_out

-

.gt1_eyescantrigger_in (1'b0), // input wire gt1_eyescantrigger_in

-

//---------------- Receive Ports - FPGA RX interface Ports -----------------

-

.gt1_rxdata_out (gt1_rxdata_out), // output wire [31:0] gt1_rxdata_out

-

//----------------- Receive Ports - Pattern Checker Ports ------------------

-

.gt1_rxprbserr_out (gt1_rxprbserr_out), // output wire gt1_rxprbserr_out

-

.gt1_rxprbssel_in (3'b0), // input wire [2:0] gt1_rxprbssel_in

-

//----------------- Receive Ports - Pattern Checker ports ------------------

-

.gt1_rxprbscntreset_in (1'b0), // input wire gt1_rxprbscntreset_in

-

//---------------- Receive Ports - RX 8B/10B Decoder Ports -----------------

-

.gt1_rxdisperr_out (gt1_rxdisperr_out), // output wire [3:0] gt1_rxdisperr_out

-

.gt1_rxnotintable_out (gt1_rxnotintable_out), // output wire [3:0] gt1_rxnotintable_out

-

//------------------------- Receive Ports - RX AFE -------------------------

-

.gt1_gtxrxp_in (rx_serdout1_p), // input wire gt1_gtxrxp_in

-

//---------------------- Receive Ports - RX AFE Ports ----------------------

-

.gt1_gtxrxn_in (rx_serdout1_n), // input wire gt1_gtxrxn_in

-

//----------------- Receive Ports - RX Buffer Bypass Ports -----------------

-

.gt1_rxbufstatus_out ( ), // output wire [2:0] gt1_rxbufstatus_out

-

//------------ Receive Ports - RX Byte and Word Alignment Ports ------------

-

.gt1_rxbyterealign_out ( ), // output wire gt1_rxbyterealign_out

-

.gt1_rxmcommaalignen_in (gt0_rxmcommaalignen_in), // input wire gt1_rxmcommaalignen_in

-

.gt1_rxpcommaalignen_in (gt0_rxmcommaalignen_in), // input wire gt1_rxpcommaalignen_in

-

//------------------- Receive Ports - RX Equalizer Ports -------------------

-

.gt1_rxdfelpmreset_in (1'b0), // input wire gt1_rxdfelpmreset_in

-

.gt1_rxmonitorout_out ( ), // output wire [6:0] gt1_rxmonitorout_out

-

.gt1_rxmonitorsel_in (2'b0), // input wire [1:0] gt1_rxmonitorsel_in

-

//------------- Receive Ports - RX Fabric Output Control Ports -------------

-

.gt1_rxoutclkfabric_out ( ), // output wire gt1_rxoutclkfabric_out

-

//----------- Receive Ports - RX Initialization and Reset Ports ------------

-

.gt1_gtrxreset_in (1'b0), // input wire gt1_gtrxreset_in

-

.gt1_rxpmareset_in (1'b0), // input wire gt1_rxpmareset_in

-

//----------------- Receive Ports - RX8B/10B Decoder Ports -----------------

-

.gt1_rxchariscomma_out ( ), // output wire [3:0] gt1_rxchariscomma_out

-

.gt1_rxcharisk_out (gt1_rxcharisk_out), // output wire [3:0] gt1_rxcharisk_out

-

//------------ Receive Ports -RX Initialization and Reset Ports ------------

-

.gt1_rxresetdone_out (gt1_rxresetdone_out), // output wire gt1_rxresetdone_out

-

//------------------- TX Initialization and Reset Ports --------------------

-

.gt1_gttxreset_in (1'b0), // input wire gt1_gttxreset_in

-

.gt1_txuserrdy_in (1'b0), // input wire gt1_txuserrdy_in

-

//-------------------- Transmit Ports - TX Buffer Ports --------------------

-

.gt1_txbufstatus_out ( ), // output wire [1:0] gt1_txbufstatus_out

-

//---------------- Transmit Ports - TX Data Path interface -----------------

-

.gt1_txdata_in (gt1_txdata_in), // input wire [31:0] gt1_txdata_in

-

//-------------- Transmit Ports - TX Driver and OOB signaling --------------

-

.gt1_gtxtxn_out (tx_serdin1_n), // output wire gt1_gtxtxn_out

-

.gt1_gtxtxp_out (tx_serdin1_p), // output wire gt1_gtxtxp_out

-

//--------- Transmit Ports - TX Fabric Clock Output Control Ports ----------

-

.gt1_txoutclkfabric_out ( ), // output wire gt1_txoutclkfabric_out

-

.gt1_txoutclkpcs_out ( ), // output wire gt1_txoutclkpcs_out

-

//------------------- Transmit Ports - TX Gearbox Ports --------------------

-

.gt1_txcharisk_in (gt1_txcharisk_in), // input wire [3:0] gt1_txcharisk_in

-

//----------- Transmit Ports - TX Initialization and Reset Ports -----------

-

.gt1_txresetdone_out (gt1_txresetdone_out), // output wire gt1_txresetdone_out

-

//---------------- Transmit Ports - pattern Generator Ports ----------------

-

.gt1_txprbssel_in (3'b0), // input wire [2:0] gt1_txprbssel_in

-

-

//GT2 (X0Y2)

-

//____________________________CHANNEL PORTS________________________________

-

//------------------------------- CPLL Ports -------------------------------

-

.gt2_cpllfbclklost_out ( ), // output wire gt2_cpllfbclklost_out

-

.gt2_cplllock_out ( ), // output wire gt2_cplllock_out

-

.gt2_cpllreset_in (1'b0), // input wire gt2_cpllreset_in

-

//-------------------------- Channel - DRP Ports --------------------------

-

.gt2_drpaddr_in (9'd0), // input wire [8:0] gt2_drpaddr_in

-

.gt2_drpdi_in (16'd0), // input wire [15:0] gt2_drpdi_in

-

.gt2_drpdo_out ( ), // output wire [15:0] gt2_drpdo_out

-

.gt2_drpen_in (1'b0), // input wire gt2_drpen_in

-

.gt2_drprdy_out ( ), // output wire gt2_drprdy_out

-

.gt2_drpwe_in (1'b0), // input wire gt2_drpwe_in

-

//------------------------- Digital Monitor Ports --------------------------

-

.gt2_dmonitorout_out ( ), // output wire [7:0] gt2_dmonitorout_out

-

//----------------------------- Loopback Ports -----------------------------

-

.gt2_loopback_in (3'd0), // input wire [2:0] gt2_loopback_in

-

//------------------- RX Initialization and Reset Ports --------------------

-

.gt2_eyescanreset_in (1'b0), // input wire gt2_eyescanreset_in

-

.gt2_rxuserrdy_in (1'b1), // input wire gt2_rxuserrdy_in

-

//------------------------ RX Margin Analysis Ports ------------------------

-

.gt2_eyescandataerror_out ( ), // output wire gt2_eyescandataerror_out

-

.gt2_eyescantrigger_in (1'b0), // input wire gt2_eyescantrigger_in

-

//---------------- Receive Ports - FPGA RX interface Ports -----------------

-

.gt2_rxdata_out (gt2_rxdata_out), // output wire [31:0] gt2_rxdata_out

-

//----------------- Receive Ports - Pattern Checker Ports ------------------

-

.gt2_rxprbserr_out (gt2_rxprbserr_out), // output wire gt2_rxprbserr_out

-

.gt2_rxprbssel_in (3'b0), // input wire [2:0] gt2_rxprbssel_in

-

//----------------- Receive Ports - Pattern Checker ports ------------------

-

.gt2_rxprbscntreset_in (1'b0), // input wire gt2_rxprbscntreset_in

-

//---------------- Receive Ports - RX 8B/10B Decoder Ports -----------------

-

.gt2_rxdisperr_out (gt2_rxdisperr_out), // output wire [3:0] gt2_rxdisperr_out

-

.gt2_rxnotintable_out (gt2_rxnotintable_out), // output wire [3:0] gt2_rxnotintable_out

-

//------------------------- Receive Ports - RX AFE -------------------------

-

.gt2_gtxrxp_in (fb_serdout0_p), // input wire gt2_gtxrxp_in

-

//---------------------- Receive Ports - RX AFE Ports ----------------------

-

.gt2_gtxrxn_in (fb_serdout0_n), // input wire gt2_gtxrxn_in

-

//----------------- Receive Ports - RX Buffer Bypass Ports -----------------

-

.gt2_rxbufstatus_out ( ), // output wire [2:0] gt2_rxbufstatus_out

-

//------------ Receive Ports - RX Byte and Word Alignment Ports ------------

-

.gt2_rxbyterealign_out ( ), // output wire gt2_rxbyterealign_out

-

.gt2_rxmcommaalignen_in (gt2_rxmcommaalignen_in), // input wire gt2_rxmcommaalignen_in

-

.gt2_rxpcommaalignen_in (gt2_rxmcommaalignen_in), // input wire gt2_rxpcommaalignen_in

-

//------------------- Receive Ports - RX Equalizer Ports -------------------

-

.gt2_rxdfelpmreset_in (1'b0), // input wire gt2_rxdfelpmreset_in

-

.gt2_rxmonitorout_out ( ), // output wire [6:0] gt2_rxmonitorout_out

-

.gt2_rxmonitorsel_in (2'b0), // input wire [1:0] gt2_rxmonitorsel_in

-

//------------- Receive Ports - RX Fabric Output Control Ports -------------

-

.gt2_rxoutclkfabric_out ( ), // output wire gt2_rxoutclkfabric_out

-

//----------- Receive Ports - RX Initialization and Reset Ports ------------

-

.gt2_gtrxreset_in (1'b0), // input wire gt2_gtrxreset_in

-

.gt2_rxpmareset_in (1'b0), // input wire gt2_rxpmareset_in

-

//----------------- Receive Ports - RX8B/10B Decoder Ports -----------------

-

.gt2_rxchariscomma_out ( ), // output wire [3:0] gt2_rxchariscomma_out

-

.gt2_rxcharisk_out (gt2_rxcharisk_out), // output wire [3:0] gt2_rxcharisk_out

-

//------------ Receive Ports -RX Initialization and Reset Ports ------------

-

.gt2_rxresetdone_out (gt2_rxresetdone_out), // output wire gt2_rxresetdone_out

-

//------------------- TX Initialization and Reset Ports --------------------

-

.gt2_gttxreset_in (1'b0), // input wire gt2_gttxreset_in

-

.gt2_txuserrdy_in (1'b0), // input wire gt2_txuserrdy_in

-

//-------------------- Transmit Ports - TX Buffer Ports --------------------

-

.gt2_txbufstatus_out ( ), // output wire [1:0] gt2_txbufstatus_out

-

//---------------- Transmit Ports - TX Data Path interface -----------------

-

.gt2_txdata_in (gt2_txdata_in), // input wire [31:0] gt2_txdata_in

-

//-------------- Transmit Ports - TX Driver and OOB signaling --------------

-

.gt2_gtxtxn_out (tx_serdin2_n), // output wire gt2_gtxtxn_out

-

.gt2_gtxtxp_out (tx_serdin2_p), // output wire gt2_gtxtxp_out

-

//--------- Transmit Ports - TX Fabric Clock Output Control Ports ----------

-

.gt2_txoutclkfabric_out ( ), // output wire gt2_txoutclkfabric_out

-

.gt2_txoutclkpcs_out ( ), // output wire gt2_txoutclkpcs_out

-

//------------------- Transmit Ports - TX Gearbox Ports --------------------

-

.gt2_txcharisk_in (gt2_txcharisk_in), // input wire [3:0] gt2_txcharisk_in

-

//----------- Transmit Ports - TX Initialization and Reset Ports -----------

-

.gt2_txresetdone_out (gt2_txresetdone_out), // output wire gt2_txresetdone_out

-

//---------------- Transmit Ports - pattern Generator Ports ----------------

-

.gt2_txprbssel_in (3'b0), // input wire [2:0] gt2_txprbssel_in

-

-

//GT3 (X0Y3)

-

//____________________________CHANNEL PORTS________________________________

-

//------------------------------- CPLL Ports -------------------------------

-

.gt3_cpllfbclklost_out ( ), // output wire gt3_cpllfbclklost_out

-

.gt3_cplllock_out ( ), // output wire gt3_cplllock_out

-

.gt3_cpllreset_in (1'b0), // input wire gt3_cpllreset_in

-

//-------------------------- Channel - DRP Ports --------------------------

-

.gt3_drpaddr_in (9'd0), // input wire [8:0] gt3_drpaddr_in

-

.gt3_drpdi_in (16'd0), // input wire [15:0] gt3_drpdi_in

-

.gt3_drpdo_out ( ), // output wire [15:0] gt3_drpdo_out

-

.gt3_drpen_in (1'b0), // input wire gt3_drpen_in

-

.gt3_drprdy_out ( ), // output wire gt3_drprdy_out

-

.gt3_drpwe_in (1'b0), // input wire gt3_drpwe_in

-

//------------------------- Digital Monitor Ports --------------------------

-

.gt3_dmonitorout_out ( ), // output wire [7:0] gt3_dmonitorout_out

-

//----------------------------- Loopback Ports -----------------------------

-

.gt3_loopback_in (3'd0), // input wire [2:0] gt3_loopback_in

-

//------------------- RX Initialization and Reset Ports --------------------

-

.gt3_eyescanreset_in (1'b0), // input wire gt3_eyescanreset_in

-

.gt3_rxuserrdy_in (1'b1), // input wire gt3_rxuserrdy_in

-

//------------------------ RX Margin Analysis Ports ------------------------

-

.gt3_eyescandataerror_out ( ), // output wire gt3_eyescandataerror_out

-

.gt3_eyescantrigger_in (1'b0), // input wire gt3_eyescantrigger_in

-

//---------------- Receive Ports - FPGA RX interface Ports -----------------

-

.gt3_rxdata_out (gt3_rxdata_out), // output wire [31:0] gt3_rxdata_out

-

//----------------- Receive Ports - Pattern Checker Ports ------------------

-

.gt3_rxprbserr_out (gt3_rxprbserr_out), // output wire gt3_rxprbserr_out

-

.gt3_rxprbssel_in (3'b0), // input wire [2:0] gt3_rxprbssel_in

-

//----------------- Receive Ports - Pattern Checker ports ------------------

-

.gt3_rxprbscntreset_in (1'b0), // input wire gt3_rxprbscntreset_in

-

//---------------- Receive Ports - RX 8B/10B Decoder Ports -----------------

-

.gt3_rxdisperr_out (gt3_rxdisperr_out), // output wire [3:0] gt3_rxdisperr_out

-

.gt3_rxnotintable_out (gt3_rxnotintable_out), // output wire [3:0] gt3_rxnotintable_out

-

//------------------------- Receive Ports - RX AFE -------------------------

-

.gt3_gtxrxp_in (fb_serdout1_p), // input wire gt3_gtxrxp_in

-

//---------------------- Receive Ports - RX AFE Ports ----------------------

-

.gt3_gtxrxn_in (fb_serdout1_n), // input wire gt3_gtxrxn_in

-

//----------------- Receive Ports - RX Buffer Bypass Ports -----------------

-

.gt3_rxbufstatus_out ( ), // output wire [2:0] gt3_rxbufstatus_out

-

//------------ Receive Ports - RX Byte and Word Alignment Ports ------------

-

.gt3_rxbyterealign_out ( ), // output wire gt3_rxbyterealign_out

-

.gt3_rxmcommaalignen_in (gt3_rxmcommaalignen_in), // input wire gt3_rxmcommaalignen_in

-

.gt3_rxpcommaalignen_in (gt3_rxmcommaalignen_in), // input wire gt3_rxpcommaalignen_in

-

//------------------- Receive Ports - RX Equalizer Ports -------------------

-

.gt3_rxdfelpmreset_in (1'b0), // input wire gt3_rxdfelpmreset_in

-

.gt3_rxmonitorout_out ( ), // output wire [6:0] gt3_rxmonitorout_out

-

.gt3_rxmonitorsel_in (2'b0), // input wire [1:0] gt3_rxmonitorsel_in

-

//------------- Receive Ports - RX Fabric Output Control Ports -------------

-

.gt3_rxoutclkfabric_out ( ), // output wire gt3_rxoutclkfabric_out

-

//----------- Receive Ports - RX Initialization and Reset Ports ------------

-

.gt3_gtrxreset_in (1'b0), // input wire gt3_gtrxreset_in

-

.gt3_rxpmareset_in (1'b0), // input wire gt3_rxpmareset_in

-

//----------------- Receive Ports - RX8B/10B Decoder Ports -----------------

-

.gt3_rxchariscomma_out ( ), // output wire [3:0] gt3_rxchariscomma_out

-

.gt3_rxcharisk_out (gt3_rxcharisk_out), // output wire [3:0] gt3_rxcharisk_out

-

//------------ Receive Ports -RX Initialization and Reset Ports ------------

-

.gt3_rxresetdone_out (gt3_rxresetdone_out), // output wire gt3_rxresetdone_out

-

//------------------- TX Initialization and Reset Ports --------------------

-

.gt3_gttxreset_in (1'b0), // input wire gt3_gttxreset_in

-

.gt3_txuserrdy_in (1'b0), // input wire gt3_txuserrdy_in

-

//-------------------- Transmit Ports - TX Buffer Ports --------------------

-

.gt3_txbufstatus_out ( ), // output wire [1:0] gt3_txbufstatus_out

-

//---------------- Transmit Ports - TX Data Path interface -----------------

-

.gt3_txdata_in (gt3_txdata_in), // input wire [31:0] gt3_txdata_in

-

//-------------- Transmit Ports - TX Driver and OOB signaling --------------

-

.gt3_gtxtxn_out (tx_serdin3_n), // output wire gt3_gtxtxn_out

-

.gt3_gtxtxp_out (tx_serdin3_p), // output wire gt3_gtxtxp_out

-

//--------- Transmit Ports - TX Fabric Clock Output Control Ports ----------

-

.gt3_txoutclkfabric_out ( ), // output wire gt3_txoutclkfabric_out

-

.gt3_txoutclkpcs_out ( ), // output wire gt3_txoutclkpcs_out

-

//------------------- Transmit Ports - TX Gearbox Ports --------------------

-

.gt3_txcharisk_in (gt3_txcharisk_in), // input wire [3:0] gt3_txcharisk_in

-

//----------- Transmit Ports - TX Initialization and Reset Ports -----------

-

.gt3_txresetdone_out (gt3_txresetdone_out), // output wire gt3_txresetdone_out

-

//---------------- Transmit Ports - pattern Generator Ports ----------------

-

.gt3_txprbssel_in (3'b0), // input wire [2:0] gt3_txprbssel_in

-

-

//____________________________COMMON PORTS________________________________

-

.gt0_qplloutclk_out(gt0_pll0outclk_out),

-

.gt0_qplloutrefclk_out(gt0_pll0outrefclk_out),

-

.sysclk_in(core_clk)

-

-

);

除了下图蓝色的,其他的不是全0 就是全1 。

浙公网安备 33010602011771号

浙公网安备 33010602011771号