SV语法 / 数据类型 / byte bit logic

例子:

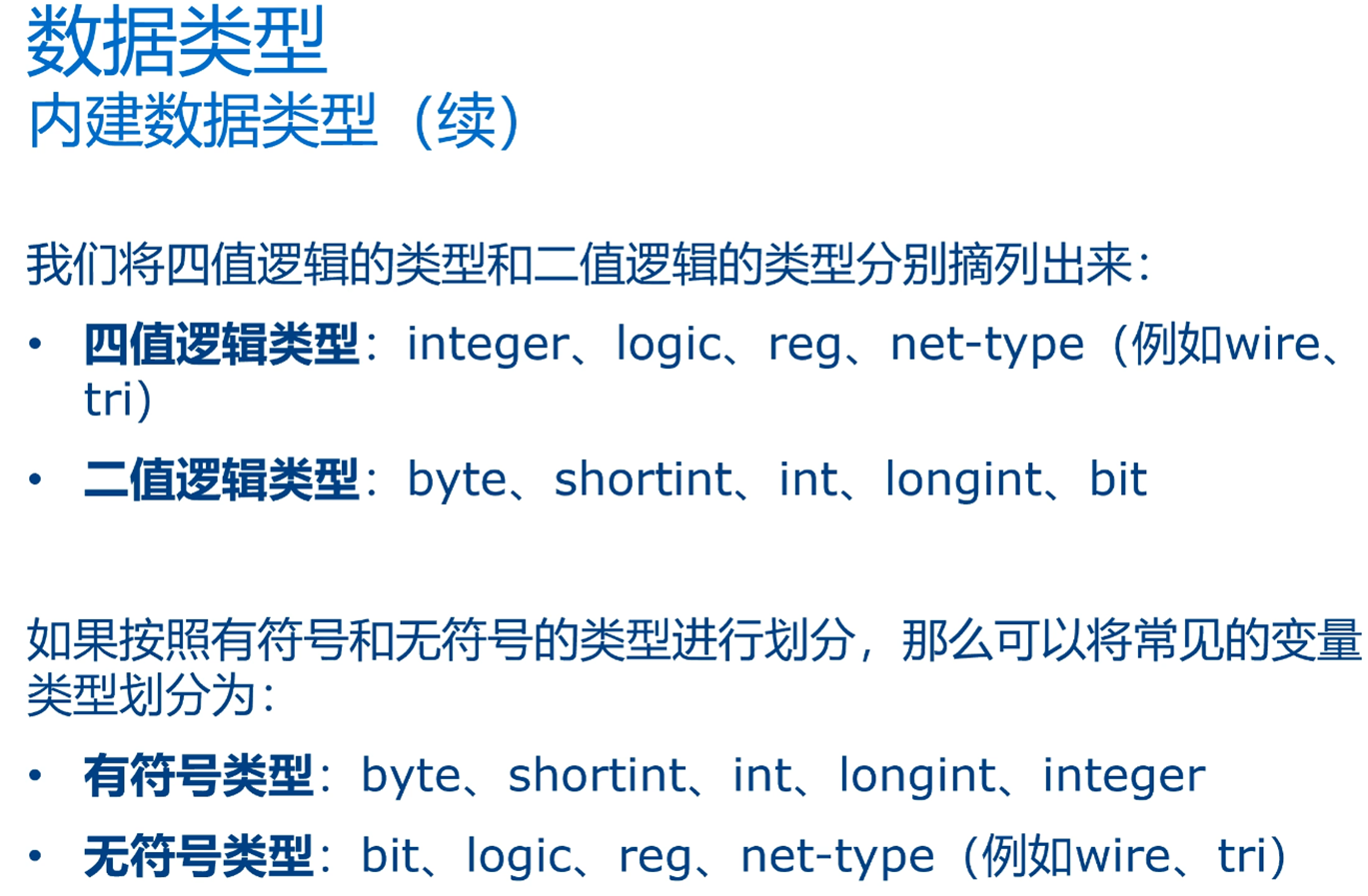

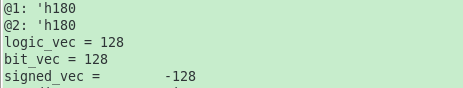

unsigned' 和 $unsigned :

//都是最高位补零,等式左值

byte signed_vec = 8'b1000_0000;

bit [8:0] result_vec;

logic [7:0] logic_vec = 8'b1000_0000;

bit [7:0] bit_vec = 8'b1000_0000;

initial begin

result_vec = signed_vec;

$display("@1: 'h%x",result_vec);

result_vec = unsigned'(signed_vec);

$display("@2: 'h%x",result_vec);

$display("logic_vec = %d",logic_vec);

$display("bit_vec = %d",bit_vec);

$display("signed_vec = %d",signed_vec);

end

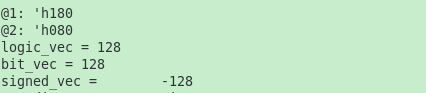

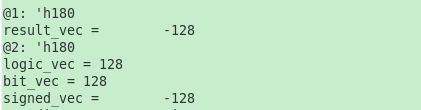

byte signed_vec = 8'b1000_0000;

bit [8:0] result_vec;

logic [7:0] logic_vec = 8'b1000_0000;

bit [7:0] bit_vec = 8'b1000_0000;

initial begin

result_vec = signed_vec;

$display("@1: 'h%x",result_vec);

result_vec = $unsigned(signed_vec);

$display("@2: 'h%x",result_vec);

$display("logic_vec = %d",logic_vec);

$display("bit_vec = %d",bit_vec);

$display("signed_vec = %d",signed_vec);

end

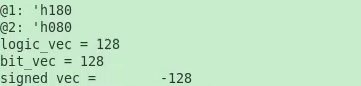

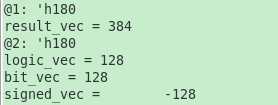

signed' 和 $signed :

//都是最高位补符号位

byte signed_vec = 8'b1000_0000;//byte默认为有符号数

bit [8:0] result_vec;

logic [7:0] logic_vec = 8'b1000_0000;

bit [7:0] bit_vec = 8'b1000_0000;

initial begin

result_vec = signed_vec;

$display("@1: 'h%x",result_vec);

result_vec = signed’(signed_vec);

$display("@2: 'h%x",result_vec);

$display("logic_vec = %d",logic_vec);

$display("bit_vec = %d",bit_vec);

$display("signed_vec = %d",signed_vec);

end

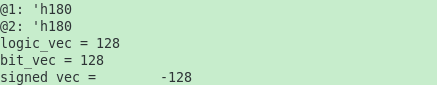

byte signed_vec = 8'b1000_0000;

bit [8:0] result_vec;

logic [7:0] logic_vec = 8'b1000_0000;

bit [7:0] bit_vec = 8'b1000_0000;

initial begin

result_vec = signed_vec;

$display("@1: 'h%x",result_vec);

result_vec = $signed(signed_vec);

$display("@2: 'h%x",result_vec);

$display("logic_vec = %d",logic_vec);

$display("bit_vec = %d",bit_vec);

$display("signed_vec = %d",signed_vec);

end

等式运算,如果右边为有符号数,左边为无符号数,右边位宽<左边位宽 最高位补符号位

如果右边为无符号数,左边为无符号数,右边位宽<左边位宽 最高位补零

有符号数给有符号数赋值(位宽不等时):

byte signed_vec = 8'b1000_0000;

bit signed [8:0] result_vec;

logic [7:0] logic_vec = 8'b1000_0000;

bit [7:0] bit_vec = 8'b1000_0000;

initial begin

result_vec = signed_vec;

$display("@1: 'h%x",result_vec);

$display("result_vec = %d",result_vec);

result_vec = $signed (signed_vec);

$display("@2: 'h%x",result_vec);

$display("logic_vec = %d",logic_vec);

$display("bit_vec = %d",bit_vec);

$display("signed_vec = %d",signed_vec);

end

如果变量声明了signed,最高位补符号位,打印时将原数值视为补码,然后求其原码

有符号数给无符号数赋值(位宽不等时):

byte signed_vec = 8'b1000_0000;

bit [8:0] result_vec; //默认为unsigned类型

logic [7:0] logic_vec = 8'b1000_0000;

bit [7:0] bit_vec = 8'b1000_0000;

initial begin

result_vec = signed_vec;

$display("@1: 'h%x",result_vec);

$display("result_vec = %d",result_vec);

result_vec = $signed (signed_vec);

$display("@2: 'h%x",result_vec);

$display("logic_vec = %d",logic_vec);

$display("bit_vec = %d",bit_vec);

$display("signed_vec = %d",signed_vec);

end

result_vec为无符号数,右边为有符号数,且右边位宽<左边位宽,最高位补符号位对齐,

result_vec 值为 9b'1_1000_0000 ,其按无符号数打印显示为:1x2^8+1x2^7=256+128=384

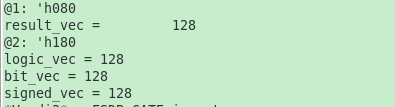

无符号数给有符号数赋值(位宽不等时):

一条运算究竟是按unsigned还是signed运算,取决于其右值的操作数是否含有unsigned变量,只要右值存在unsigned变量,整个操作就会按unsigned处理

bit [7:0] unsigned_vec = 8'b1000_0000;

bit signed [8:0] result_vec;

logic [7:0] logic_vec = 8'b1000_0000;

bit [7:0] bit_vec = 8'b1000_0000;

initial begin

result_vec = unsigned_vec;

$display("@1: 'h%x",result_vec);

$display("result_vec = %d",result_vec);

result_vec = $signed (unsigned_vec); //$signed 会把无符号数的最高位扩展 此时的 result_vec 打印应该显示 -128

$display("@2: 'h%x",result_vec);

$display("logic_vec = %d",logic_vec);

$display("bit_vec = %d",bit_vec);

$display("signed_vec = %d",unsigned_vec);

end

无符号数给有符号数赋值时,最高位 补零 对齐 result_vec 为 9 bit 位宽,最高位为零 :9‘b 0_1000_0000; 有符号数:正数的补码 反码 原码相同,

所以result_vec = 1 x 2^7 = 128

浙公网安备 33010602011771号

浙公网安备 33010602011771号