Verilog 基本语句

Verilog HDL语句包括过程语句、块语句、赋值语句、条件语句、循环语句、编译导向语句等。

| 类别 | 语句 |

| 赋值语句 | 持续赋值语句:assign |

| 过程赋值:=,<= | |

| 块语句 | 串行块:begun-end |

| 并行块:fork-join | |

| 过程语句 | initial |

| always | |

| 条件语句 | if-else |

| case,casez,casex | |

| 循环语句 | for |

| repeat | |

| while | |

| forever |

1.连续语句赋值:

用于对线网进行赋值,等价于门级描述。具有以下特点:

- 左值必须为一个线网类型的变量或向量,不能是寄存器类型。

- 输出值随输入值变化而随时变化。

- 操作数可以是线网或寄存器或函数调用。

- 必须用“=”阻塞赋值进行赋值。

格式:

- 普通连续赋值:wire OUT;assign OUT=INT1 & INT2;

- 缺省连续赋值(在线网声明的同时对其赋值): wire OUT=INT1 & INT2;

- 缺省线网声明:信号名被用在连续赋值左侧,则该信号默认为一个缺省声明的线网类型变量:wire INT1;assign OUT=INT1 ;//则OUT默认为线网类型;

- 线网被连接在模块端口,则缺省线网宽度为模块端口的宽度。

2.单元块语句

①顺序块begin-end:

格式:

begin:块名 //块名可缺省

语句1;

语句2;

....

语句N;

end

②并行块fork-join:

格式:

fork:块名 //块名可缺省

语句1;

语句2;

....

语句N;

join

注意:如果两条语句在同一时刻对同一变量产生影响,则可能出现隐含的竞争。

3.条件语句

①if-else语句

1)系统对逻辑表达式的值进行判断,若为0,x,z,按“假”处理;若为1,按“真”处理;

2)if和else语句中可嵌套多个操作语句;

3)if-else语句具有优先级,前面的优先级最高。

②case语句

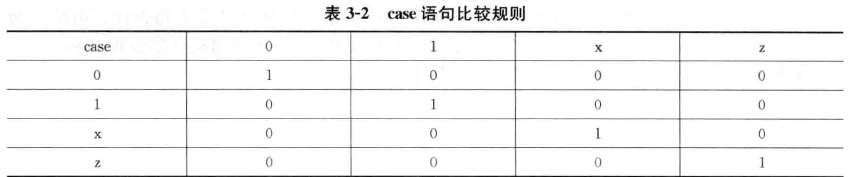

1)case语句

case(表达式)

数值1:

语句1;

....

数值n:

语句n;

default:

语句n+1;

endcase

case语句没有优先级,即case语句的每个分支都是并行的,与位置无关。

case语句的所有表达式的值的位宽必须相等。

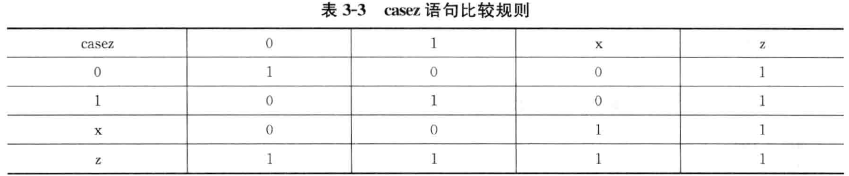

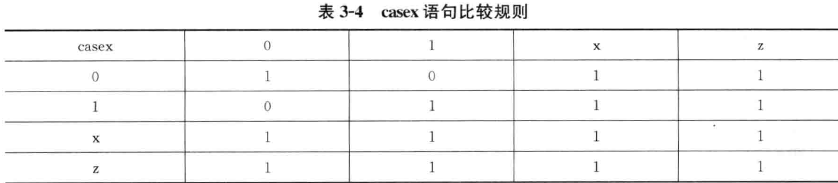

2)casez与casex语句

使用条件语句时,为了使程序具有更好的可读性和可维护性,应遵循以下几点要求:

①if-else语句的级联不要超过3层。

②case的级联不要超过2层。

③if语句必须要有else,case语句必须要有default,否则将产生不必要的锁存器;设计中禁用casez/casex。不能使用casez/casex语句,不是说他们没用,当在仿真实验中,这些是可用的。

4.循环语句

四种循环语句:forever、repeat、while、for

1)forever语句

forever语句 是连续的执行语句,格式如下:

forever

语句;

或

forever

begin

多条语句;

end

forever语句常用于产生周期性的波形,作为仿真控制信号。forever语句不能独立写在程序中,必须写在initial中。

forever用来表示永久循环,在永久循环中不包含任何条件表达式,等价于永远为真的while循环,如while(1)。如果要从forever循环中退出,可以使用disable语句。

2)repeat语句

repeat语句可以连续执行一条语句n次,主要特点是可以执行固定次数的循环,其使用格式如下所示:

repeat(循环次数表达式)

语句;

或

repeat(循环次数表达式)

begin

多条语句;

end

3)while语句

使用格式:

while(循环执行条件表达式)

语句;

或

while(循环条件表达式)

begin

多条语句;

end

4)for语句

使用格式:

for(表示式1;表达式2;表达式3)

5.过程语句

过程语句有两种:initial和always

initial语句常用于仿真中的初始化,initial过程块中的语句仅执行一次;always语句则是不断重复执行的。

每一条initial语句和always语句都是独立的执行过程,彼此并行执行,执行顺序于在模块内的书写顺序无关,并且,每条initial和always语句过程语句都是在仿真时间0时刻同时开始的。

initial语句和always语句不可嵌套使用。

1)always语句

格式如下:

always @(敏感信号表达式)

begin

语句1;

.....

语句n;

end

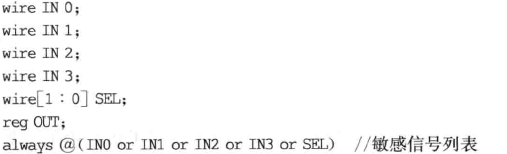

敏感信号表达式中应列出影响块内取值的所有信号,多个敏感信号用关键字“or”连接。

敏感信号可以分为两种类型:电平敏感型、边沿敏感型。边沿敏感主要用来描述组合逻辑电路,而边沿敏感主要用来描述时序逻辑电路。

每一个always过程最好只有一个类型的敏感信号触发。

always@(A or B)或always@(posedge CLK or negedge RST_B)//表示时钟的上升沿或者复位的下降沿。

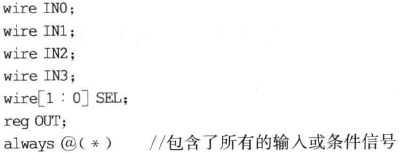

对于电平敏感型,可用“*”代替所有的输入或条件信号,如:

2)initial语句

只执行一次,不带触发条件,常用于仿真中的初始化,是面向模拟仿真中的语句,不被逻辑综合工具支持。

initial

语句1;

.......

语句n;

end

浙公网安备 33010602011771号

浙公网安备 33010602011771号