程序块(Program Block)和时序区域(Timing Region)

设计和测试平台都用module封装后,它们之间可能会出现竞争状态。这个问题的根源在于设计和测试平台的事件混合在同一个时间片内,我们希望存在一种方法可以在时间轴上分开这些事件,就像分开代码那样。那System Verilog如何将测试平台的事件和设计的事件分开调度的呢?在SV中,将测试平台的代码封装在程序块(Program Block)之中,值得注意的是,程序块不能有任何的层次级别,例如模块的实例,接口等等。

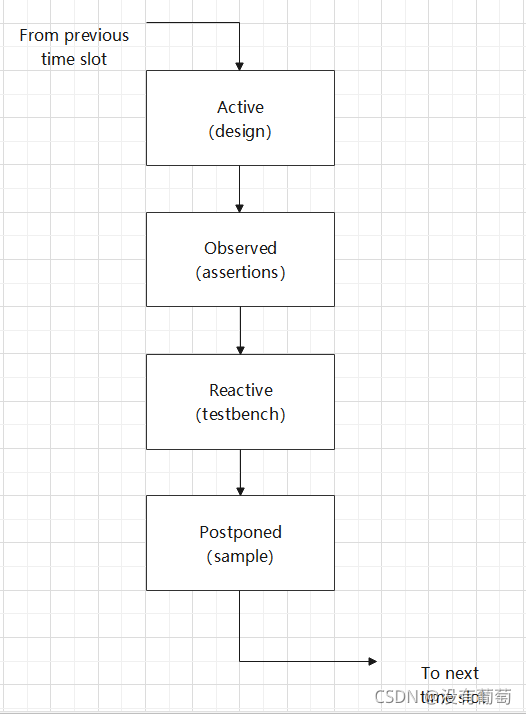

| 区域名 | 行为 |

| Active | 仿真模块中的设计代码 |

| Observed | 执行System Verilog的断言 |

| Reactive | 执行程序中的测试平台的部分 |

| Postponed | 为测试平台的输入采样信号 |

注意时间不是单向地向前流动——Observed和Reactive区域的事件可以触发本时钟周期内Active区域中进一步的设计事件。这也是为什么时钟发生器不能放在程序块之中,因为这会引起竞争,clk信号和测试平台的输出信号都从Reactive区域开始传递,在Active区域进入设计,所以时钟发生器应该放在一个模块之中。

System Verilog把任何一个程序块都视为含有一个测试,如果只有一个程序块,当完成所有initial块的最后一个语句时,仿真就结束了,即使还有其他线程在运行。所以,当测试结束之后无需关闭所有的监视器和驱动器。如果存在多个程序块,仿真在最后一个程序块结束时结束。可以用$exit来中断任何一个程序块,或者用$finish来结束仿真。

同时,你也可以指定设计和测试平台之间的延时。时钟块默认时许是在#1step延时后采样输入信号,在#0后驱动输出信号。1step延时规定了前一个时钟片的postponed区域,在设计有任何新动作之前被采样。

Program中不允许使用always块,可以使用initial块。因为在一个设计之中,一个always块可能从仿真开始就会在每一个时钟的上升沿触发执行。但是一个测试平台的执行过程是经过初始化,驱动和相应设计等步骤后结束仿真。一个连续的always模块不能正常工作。但是,如果确实需要一个always块,那可以使用“initial forever”来代替。

浙公网安备 33010602011771号

浙公网安备 33010602011771号