systemverilog中的静态变量static和动态变量automatic

本文参考:

SystemVerilog静态变量和动态变量_行走的BUG永动机的博客-CSDN博客_systemverilog静态变量和动态变量

systemverilog之Automatic - 腾讯云开发者社区-腾讯云 (tencent.com)

https://blog.csdn.net/zhajio/article/details/101429431

Verilog 早期版本仅有静态生命周期的概念,同一个function或者task无论你调用多少次内部的变量都是分配的同一个地址。没有调用堆栈的操作。

在Verilog-2001 标准中引入了动态生命周期的概念,任务或者函数中的变量可以定义为动态变量。

动态变量主要用来描述在测试程序、抽象系统级、transaction级或总线功能模型中的验证程序

动态变量也可以用来编写可重入的任务(当一个任务的前一次调用仍在进行时,可以再次调用)

在systemverilog中 用static和automatic 关键字来表示声明的变量是静态还是动态。默认是静态变量。在module中声明的变量必须是静态变量。在function,task,begin...end, fork...join 中的变量可以使用automatic声明为动态变量。默认也是静态变量。在这里如果是从C++转过来写SV的尤其要注意。

静态变量和动态变量的区别:

初始化:

静态变量初始化不可综合,动态变量的初始化可以综合。

静态变量的初始化实在仿真前,动态变量的初始化是在被调用时发生的。

静态变量在下次调用时保持上次调用后的值。动态变量在下次调用时会开辟新的存储空间并重新初始化。

使用原则:

在always和initial块中,需要内嵌初始化就声明为动态变量,不需要内嵌初始化用静态变量

如果任务或函数是可重入的,应设置被动态的,其内的变量也应是动态的

如果任务或函数用来描述独立的硬件部分,且不可重入,应该设置为静态的,其内的变量也应为静态的

例子:

//sv file

import "DPI-C" function void recurr(input int a);

initial begin

recur(1);

recurr(1);

end

function void recur(int a); int st_v=0; automatic int at_v=0; st_v++; at_v++; $display("a: %0d, st_v: %0d, at_v:%0d",a,st_v,at_v); if(a==4) return; recur(a+1); endfunction

// C++ file:

extern "C" void recurr(int a){

int st_v=0;

int at_v=0;

st_v++;

at_v++;

printf("a: %0d, st_v: %0d, at_v: %0d\n",a,st_v,at_v);

if(a==4) return;

recurr(a+1);

}

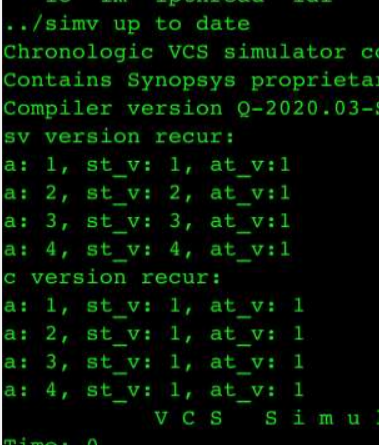

运行结果:

从上面结果可以看出在sv的function中声明的变量默认就是静态的,重复调用时,变量的值维持上次的结果,除非声明为automatic。或者直接将function声明为automatic,此时function内部所有变量默认都会时automatic的

浙公网安备 33010602011771号

浙公网安备 33010602011771号