关于仿真软件在跑systemverilog的时候,是如果通过将HDL代码分成5个区域来编译

关于仿真软件在跑systemverilog的时候,是如果通过将HDL代码分成5个区域来编译,从而实现用软件模拟硬件的运行结果的。

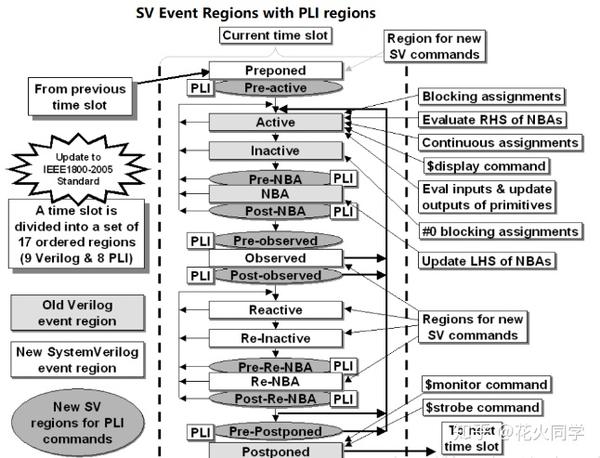

首先是基础概念,systemverilog标准划分了仿真软件的5个跑仿真所要执行的5个区域,说白了就是规定了软件在跑代码的时候要把代码分成5类,放到5个堆栈里面分别跑,这样才能明明在软件上是以顺序方式来执行代码的,却能“看似”像在硬件中那样的实现并行的电路结果。

今天的内容就先这样,等以后弄到断言方面的内容时,再回来把断言等部分的软件处理方式更新一下。

浙公网安备 33010602011771号

浙公网安备 33010602011771号