什么是形式验证??

形式验证入门之基本概念和流程

一、什么是形式验证?

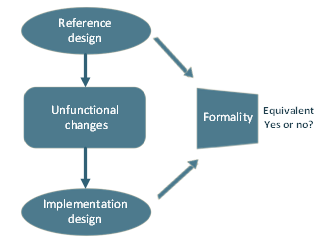

VLSI设计的功能验证有两种方法,动态仿真验证和形式验证。形式验证采用数学方法来比较原设计和修改设计之间的逻辑功能的异同,而动态仿真验证是对两设计施加相同的激励后,观测电路对激励的反应异同。设计越大,为了达到100%的覆盖率,动态仿真验证所需要的矢量越多,这时形式验证在这方面就有优势了。但形式验证是一种功能等价验证,这种验证脱离工艺和版图约束,无法保证时序的准确性,故而,形式验证往往需要和静态时序分析工具一起来完成对电路完备的验证。本文就以Synopsys公司的formality工具为例,来介绍形式验证的流程和基本概念,后续会详细介绍使用formality做RTL2Gate流程中每一步骤的操作。

二、使用formality做形式验证需知的基本概念。

图1. 形式验证概念图

1. reference design 和 implementation design

reference design是golden design,即认为是正确的标准的设计。implementation design是经过非功能性修改的、待验证的设计。比如,使用综合工具DC将RTL代码映射成和工艺库相关的门级网表,那么原RTL设计就是reference design,而DC输出的门级网表就是implementation design。

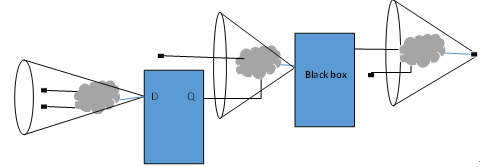

2. logic cone和compare point

逻辑锥(logic cone)是由设计中的组合逻辑电路组成的,每个逻辑锥可以有多个输入,只有一个输出。逻辑锥的输入为:设计输入端口、寄存器输出端口、黑盒子输出端口;逻辑锥的输出为:设计的基本输出端口、寄存器输入端口和黑盒子输入端口。逻辑锥的输出点就是比较点,reference design中的比较点和implementation design中的比较点是要一一对应的,这称为比较点匹配(match)。Formality将设计划分成一个个逻辑锥,以逻辑锥为单位,将其抽象为数学模型,然后针对每个比较点将implementation design和reference design进行比较,注意逻辑锥之间是可以交叠的。

图2. 设计的逻辑锥划分

3. Consistency and Equality

对于某个输入pattern,reference design中某个比较点的响应为x,即0或1都可以的一个状态,那么在implementation design 中相应比较点处的响应为0或者1,验证都会通过,这叫做Design Consistency;而此时Design Equality要求在implementation design 中相应比较点处的响应也应该为x。可见,Design Equality的验证标准要高于Design Consistency,对这两种验证,Formality工具都是支持的。

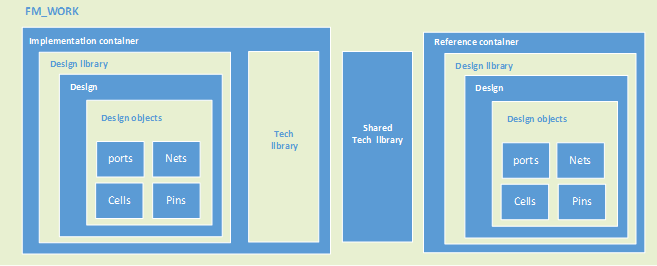

4. container和library

在Synopsys工具中,container是个常见概念,它就是一个存储空间,formality中的container内存储的是工艺库和设计库信息。通常,为了对两个设计进行比较,我们需要将reference design放到一个container中,将implementation design放到另一container中。一旦启动formality,工具会自动创建一个名为FM_WORK的工作空间,在这个工作空间里,默认创建了名为i和r两个container,这两个默认的container用起来很方便,当然,用户也可以创建新的container。在向container中读入设计的时候,如果不指定设计库的名称,formality会默认创建一个名为WORK的设计库,并将设计读入其中。在读工艺库的时候,如果不指定container,那么这些工艺库会放到FM_WORK工作目录下,并对所有container可见,称为共享库;如果指定了container,那么这些工艺库会放到相应的container中,库信息只能该container内部访问。这样,如图所示,每一个design和design object可以通过container、design library、design、design object找到,这条路径就是designID或objectID。

图3. Container 和 library关系图

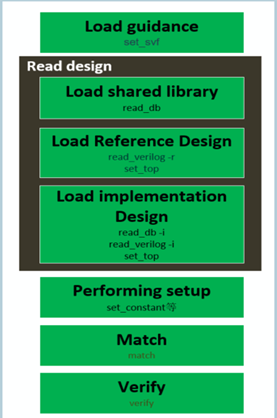

三、形式验证的基本流程

使用formality做形式验证的基本流程如图4所示,1)Load guidance阶段是formality提取SVF文件信息的阶段;2)接下来读入设计,如果set_top声明的设计顶层和待验证的设计不是同一层次,需要使用命令set_reference_design和set_implemetation_design来声明target design;3)在setup阶段提供帮助比较点匹配的信息,声明约束信息。4)match阶段进行比较点匹配,这一步骤formality进行逻辑锥划分、比较点映射和对读入的SVF文件的信息处理(即guide命令处理);5)进行等价性验证,若不一致需要debug。在整个过程中,涉及到四种shell mode:setup mode、match mode、verify mode和guide mode,每种mode下可使用的formality command是不相同的,使用者在查看相应命令的man page时需要注意。打开工具默认进入setup mode,执行了math命令后进入match mode,执行了verify命令后进入verifymode,而guide mode不易察觉,因为SVF信息的提取虽然在这一mode下进行,但是提取后工具又进入setup mode了,所以使用者不以察觉。

图4. formality 应用基本流程图

小结:本文介绍了形式验证的基本概念和基本流程,有兴趣的同学欢迎关注接下来对各个步骤的详细介绍:如何恰当使用guidance、load design注意事项、setup阶段需要补充哪些信息、比较点匹配规则和verify失败时基本的debug方法等。

浙公网安备 33010602011771号

浙公网安备 33010602011771号