NMOS与PMOS区别

在CMOS设计里,PMOS管和NMOS管同等重要,不过因为一般的电路设计书籍都注重NMOS管的讲解,PMOS都是直接类比NMOS,所以让人不太清楚PMOS的工作原理。

1. 端口不同

PMOS和NMOS的源漏方位相反,NMOS的漏端drain在上面,PMOS的源端source在上面,之所以这么做是借助方位来表明电位的高低。NMOS的漏端drain和PMOS的源端source的电压都比栅端gate电压高,所以这么标注获得一个“visual aid”。电流方向是一致的,如果采用箭头表示电流方向,都是从上到下的。底下是razavi书上的图和说明,一并奉上作为参考。

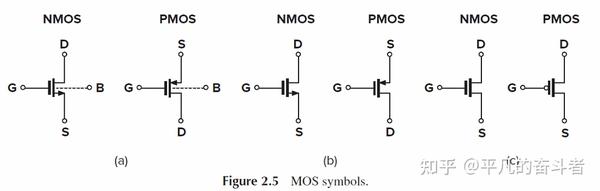

2.1.3 MOS Symbols

The circuit symbols used to represent NMOS and PMOS transistors are shown in Fig.2.5. The symbols in Fig.2.5(a) contain all four terminals, with the substrate denoted by"B"(bulk) rather than"S"to avoid confusion with the source. The source of the PMOS device is positioned on top as a visual aid because it has a higher potential than its gate. Since in most circuits the bulk terminals of NMOS and PMOS devices are tied to ground and VDD, respectively, we usually omit these connections in drawing [Fig.2.5(b)]. In digital circuits, it is customary to use the "switch" symbols depicted in Fig.2.5(c) for the two types, but we prefer those in Fig.2.5(b) because the visual distinction between S and D proves helpful in understanding the operation of circuits.

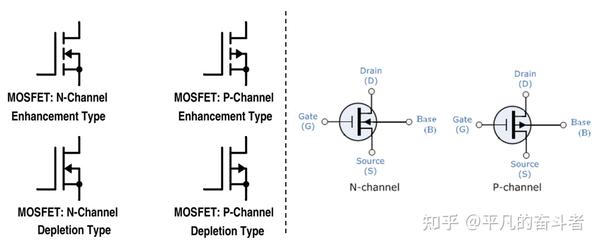

如果是四端口画法,箭头的方向就不是电流方向,而是衬底和沟道之间的PN结方向,和二极管一样,都是从P端指到N端。如下图所示。

NMOS是N型沟道,P型衬底,衬底接最低电位,PMOS是P型沟道,N型衬底接最高电位。这样是为了源漏端和衬底形成P-N结反偏,不然电流从源漏端直接正向导通到地。击穿说的也是这个P-N结反向击穿。因为沟道和衬底的材料不同,所以栅压变化才会有耗尽层-反型层形成的说法。

NMOS的沟道材料是N型,而衬底材料是P型,所以栅极需要加正电压,才能排斥P型衬底里的空穴,吸引电子聚集在沟道的下方,和栅极的金属板构成栅电容。电容的介质材料是SiO2。PMOS的沟道材料是P型,而衬底材料是N型,要想在N型材料里吸引空穴的话,自然栅极应该加负电压。和NMOS栅极正电压越大,沟道的导电能力越强一样,PMOS是栅极电压负向越大,沟道导电能力越强。

问题:MOS管是多数载流子导电,为什么,有什么好处?

空穴:带正电,实际中不存在,为方便处理设置的,是电子行为的反向等效。

说完栅极,我们说衬底极substrate。NMOS的衬底极接地,PMOS的衬底极接正电压,这都是根据P-N结反偏要求设定的。也就是P极接负,N极接正。衬底的电压简单的是直接就近连接,NMOS一般和源端一起接地,PMOS衬底和源端一起连 VDDV_{DD} 。

2. 工作条件不同

2.1. 沟道形成条件

现在来看一下工作条件。NMOS里大家都烂熟于心了, VGS>VthV_{GS}>V_{th} 和 VDS>VGS−VthV_{DS}>V_{GS}-V_{th} ,前者是用来保证导电沟道的形成,叠加后者的条件就是饱和状态。导通条件到PMOS这,是以栅端电压对比衬底电压 VDDV_{DD} 较小为好,这样空穴就会被吸附到表面形成沟道,所以可以看出阈值电压 VthV_{th} 为负值。这和NMOS的 VthV_{th} 的正值恰相反,注意这里不涉及增强型还是耗尽型管子的区分。考虑衬底和源端相连,导通条件是 VGS<VthV_{GS}<V_{th} ,如果用绝对值表示 |VGS|>|Vth||V_{GS}|>|V_{th}| 。电流的流动从方位上和NMOS没有区别,都是从上方流到下方。

2.2 饱和条件

饱和区的条件类比较为麻烦,因为饱和区形成的微观机理稍微复杂一点。首先我们要弄清,为什么对于NMOS,当 VDS>VGS−VthV_{DS}>V_{GS}-V_{th} 就有 IDI_D 饱和呢?当满足了 VGS>VthV_{GS}>V_{th} ,沟道里从漏端到源端的电压都是一样的,可以等效为简单的平行板电容器。但是MOS管是个立体结构,除了平行板的垂直电场,要形成电流还需要水平方向的电场,也就是从漏极到源级的电场。水平方向的电场NMOS是漏端最高,源端最低,沿着沟道方向电势逐渐降低。

沟道处的电势由固定的衬底电势叠加水平方向的电势,就造成了栅平行板电容虽然栅极电压不变,但衬底边的电压不均匀。对于NMOS来说,需要保证VGS>VthV_{GS}>V_{th},这里S换成sub(衬底)会更好理解, VG−Sub>VthV_{G-Sub}>V_{th} ,但现在衬底电压因为施加了 VDSV_{DS} 不再保持均匀相等。靠近漏端这一端的电压 VGDV_{GD} 要比 VGSV_{GS} 小,因为漏端电压高。随着漏端电压的提升, VGDV_{GD} 会率先小于 VthV_{th} ,这样漏端这个地方就形成了夹断(pinch-off),但这个夹断和 VG−Sub<VthV_{G-Sub}<V_{th} 时的截止不一样,称为预夹断,是通过VDSV_{DS}破坏了VG−Sub>VthV_{G-Sub}>V_{th}的条件形成的夹断,且只有漏端一点夹断了,不是整个沟道都夹断了。但是,沟道的预夹断正是我们需要的,因为夹断后漏端和栅端就连接起来的了。

这里其实是有点问题的,因为按照前面的器件模型,夹断后VGDV_{GD}是等于 VthV_{th} 的,继续增大 VDV_D 可以继续减小VGDV_{GD},造成小于VthV_{th}的情况。但这里的假设是, VGDV_{GD} 减小到VthV_{th}的时候,栅端和漏端连接起来,这样无论VDV_D如何变化,夹断点都等于 VthV_{th} ,整个沟道的水平电压也就保持不变了。这里不考虑channel-length modulation的情况。夹断以后,器件模型就类似是diode-connected的电路拓扑了,栅端和漏端连接,器件始终工作在饱和区。不过不同的是,器件里降低VDV_D可以回到线性区,而在电路里,降低VDV_D回不到线性区,只能直接进入截止区。

根据前面的分析,可以知道NMOS进入饱和区的要求是 VGD<VthV_{GD}<V_{th} ,换成常用的是 VDS>VGS−VthV_{DS}>V_{GS}-V_{th} 。PMOS因为栅端电压负与衬底端,所以施加 VSDV_{SD} 后,漏端的电压最低,且低的栅端电压高于漏端电压不超过阈值电压了,破坏了栅电压构筑的导通条件,所以有 VGD>VthV_{GD}>V_{th} ,换算一下, VDS<VGS−VthV_{DS}<V_{GS}-V_{th} 。

总结

对于NMOS,栅端gate比衬底端substrate高一个VthV_{th} ,才能形成沟道,要破坏这个沟道,栅端gate比漏端drain高,但不能高于 VthV_{th} ,才能形成预夹断,工作在饱和区。

VGS>Vth,VGD<VthV_{GS}>V_{th},V_{GD}<V_{th} ,后一个条件即 VDS>VGS−VthV_{DS}>V_{GS}-V_{th}

对于PMOS,栅端gate比衬底端substrate低过负阈值电压 VthV_{th} ,才可以吸附空穴,形成反型层,栅端gate比漏端drain低,但不能低过 VthV_{th} , 形成沟道破坏条件,才能工作在饱和区。

VGS<Vth,VGD>VthV_{GS}<V_{th}, V_{GD}>V_{th} ,后一个条件即 VDS<VGS−VthV_{DS}<V_{GS}-V_{th} ,考虑VthV_{th}是负值,也可以改为 |VGS|>|Vth|,|VDS|>|VGS|−|Vth||V_{GS}|>|V_{th}|,|V_{DS}|>|V_{GS}|-|V_{th}| ,这样和NMOS的条件就有了一定的统一性。

我是平凡的奋斗者,如果本文对你有帮助,欢迎点赞,关注和评论。

浙公网安备 33010602011771号

浙公网安备 33010602011771号