什么是三态门?

什么是三态门?

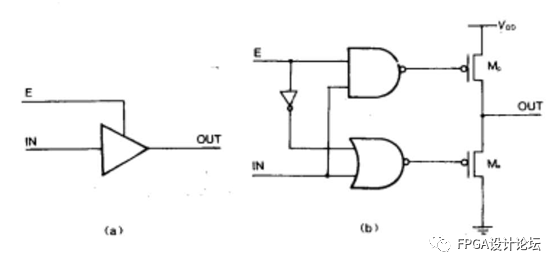

三态门即三态电路。三态电路可提供三种不同的输出值:逻辑“0”,逻辑“1”和高阻态。高阻态主要用来将逻辑门同系统的其他部分加以隔离。例如双向I/O电路和共用总线结构中广泛应用三态特性。

赋值冲突问题:

错误代码:(存在赋值冲突)

1. assign c =(sel[0] == 1'b1) ? a:1'b0;

2. assign c =(sel[1] == 1'b1) ? b:1'b1;

这个例子代码,两条赋值语句肯定都是一直有效的,因此必然产生赋值冲突,从而导致出错。

正确代码:

1. assign c =(sel[0] == 1'b1) ? a:1'bz;

2. assign c =(sel[1] == 1'b1) ? b:1'bz;

这个代码的写法和上面的唯一区别就是高组态的使用。

为什么使用了高阻态,代码就是正确的了呢?

这是因为高阻态实际上就是电路中的断路,通过合理切换到高阻态,可以让上述有高阻态的例子中的两条赋值语句不会在同一时刻生效,因此不会产生赋值冲突。

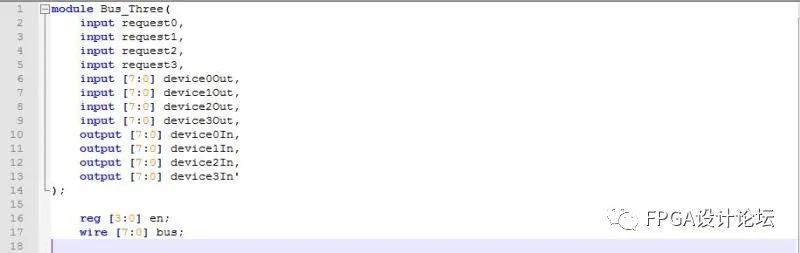

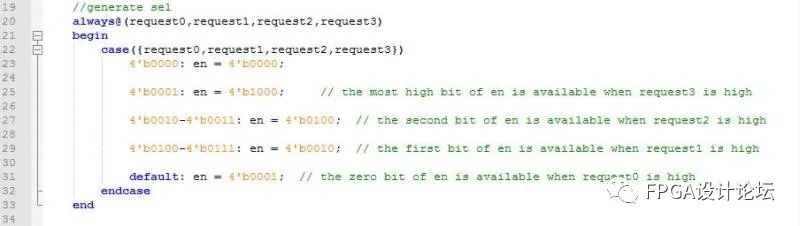

一个简单的三态门式总线的FPGA实现方式,功能代码分为三个部分:

1. 选择器控制信号产生部分,采用抢占式优先级译码器的思路,根据四个外围器件的请求信号产生多路选择器的选择控制信号。

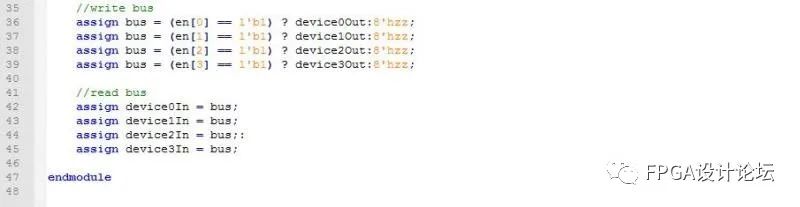

2. 写总线部分,即将四个三态门的输出连接到总线上。

3. 读总线部分,各个外围器件根据自己的情况将总线数据读入器件内部进行运算和处理。

源代码:

浙公网安备 33010602011771号

浙公网安备 33010602011771号