Verilog语法【repeat和task】

1.task

语法格式:

task my_task;

input a, b;

inout c;

output d, e;

begin

. . . // statements that perform the work of the task

. . .

c = foo1; // the assignments that initialize result regs

d = foo2;

e = foo3;

end

endtask

语法格式二:

task my_task (input a, b, inout c, output d, e);

begin

. . . // statements that perform the work of the task

. . .

c = foo1; // the assignments that initialize result regs

d = foo2;

e = foo3;

end

endtask

使用:

my_task (v, w, x, y, z);

2.repeat

用法一:

repeat(10)begin

...//执行10次

end

用法二:

repeat(10)@(posedge clk);//延迟10个时钟周期

a=b;

或者直接写成:

a=repeat(10)@(posedge clk) b ;

3.testbench使用举例

实现流水灯效果的一个testbench,迅速掌握task和repeat的用法。

`timescale 1ns/1ns

`define clock_period 20

module traffic_lights;

reg

clock,

red,

amber,

green;

parameter

on = 1,

off = 0;

//产生时钟

always #(`clock_period/2)clock = ~clock;

//设置初始值

initial begin

red = off;

amber = off;

green = off;

clock = 1;

end

//主程序

always begin

repeat(10)begin

red = on;

light(red,(`clock_period*10));

green = on;

light(green,(`clock_period*10));

amber = on;

light(amber,(`clock_period*10));

end

#100;

$stop;

end

//task

task light;

output color;

input [31:0] delay;

color = repeat (delay) @ (posedge clock) off;

endtask

endmodule

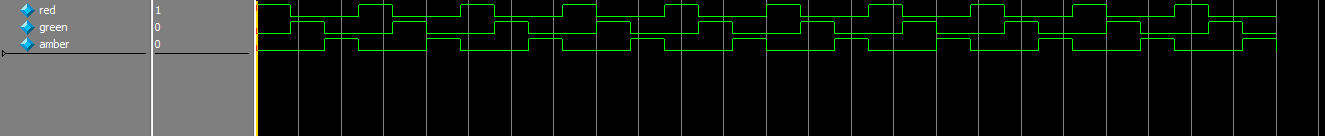

仿真结果

浙公网安备 33010602011771号

浙公网安备 33010602011771号