DDR3学习笔记三

- 从SDRAM到DDR3

- DDR3硬件设计

- DDR3操作时序及IP核设计

- DDR3读写程序设计

- 从SDRAM到DDR3

- SDRAM的操作时序

SDRAM操作指令

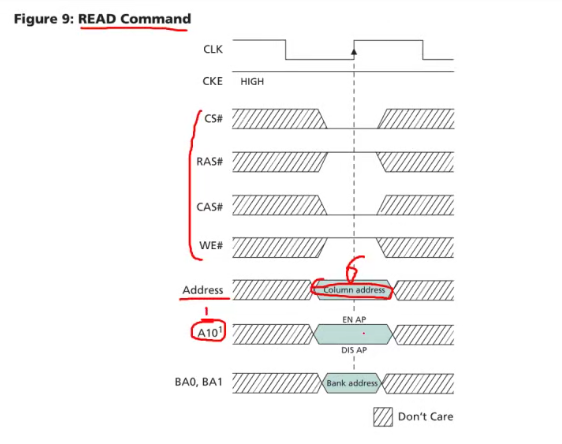

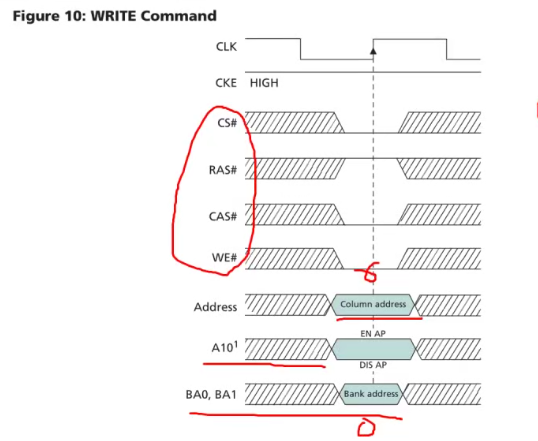

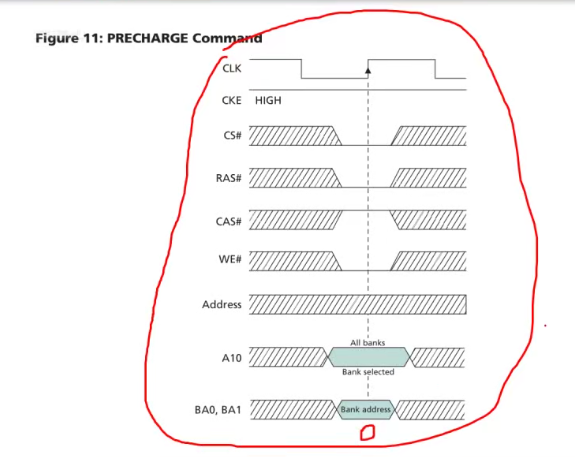

A10 EN_AP:auto_precharge,每一次读写完对所有BANK进行预充电,下一次读写前不需要先发送precharge 指令(DIS_AP)。

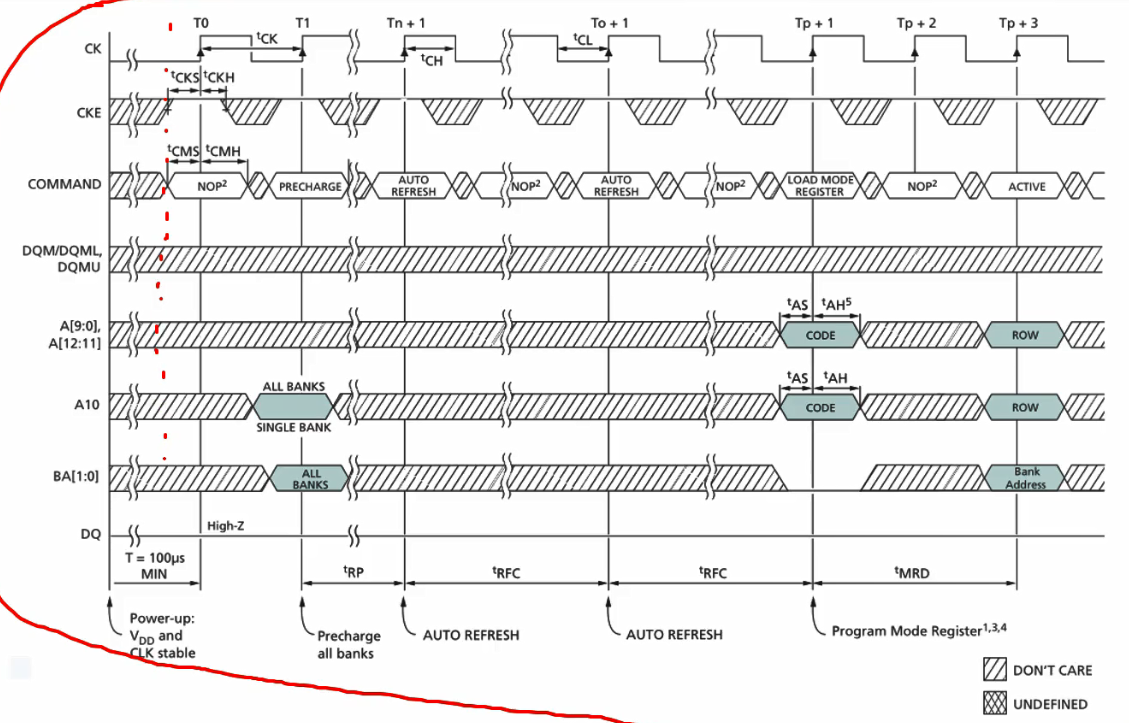

初始化命令:

电源上电后需要发送此初始化命令,上电后延迟等待100us发送NOP指令--->Precharge---->Auto Refresh---->NOP指令

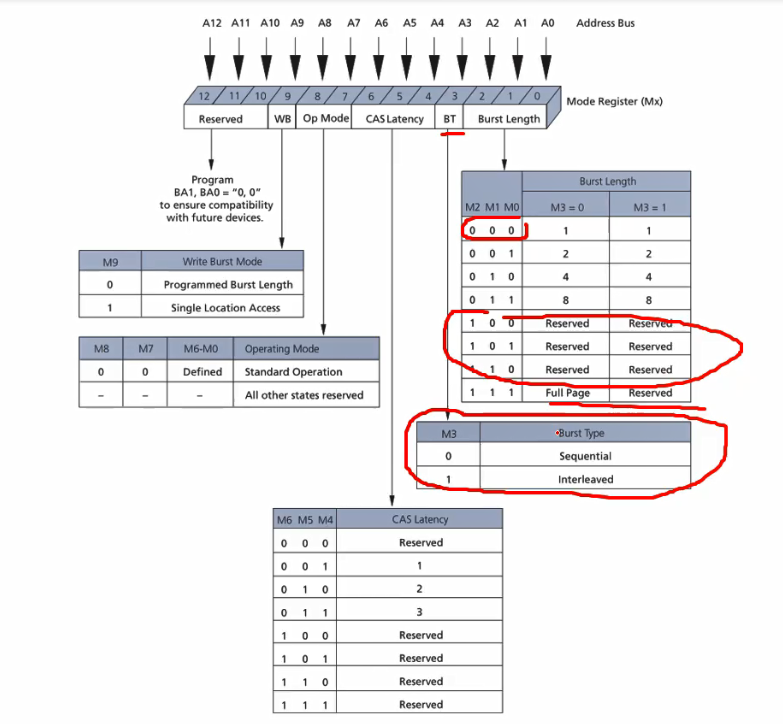

Load MODE REG:

COMMAND :RAS CAS WE CS= L L L L

CAS Latency :(Column Address Select) ,在列激活(地址赋值)的时候,指令同时发送 。

CAS Latency (CL)只在读数据延迟,写数据无延迟。

The CAS Latency is defined by MR0 (bit A2, A4~A6) as shown in the MR0 Definition figure. CAS Latency is the delay, in

clock cycles, between the internal Read command and the availability of the first bit of output data. DDR3(L) SDRAM does

not support any half clock latencies. The overall Read Latency (RL) is defined as Additive Latency (AL) + CAS Latency

(CL); RL = AL + CL

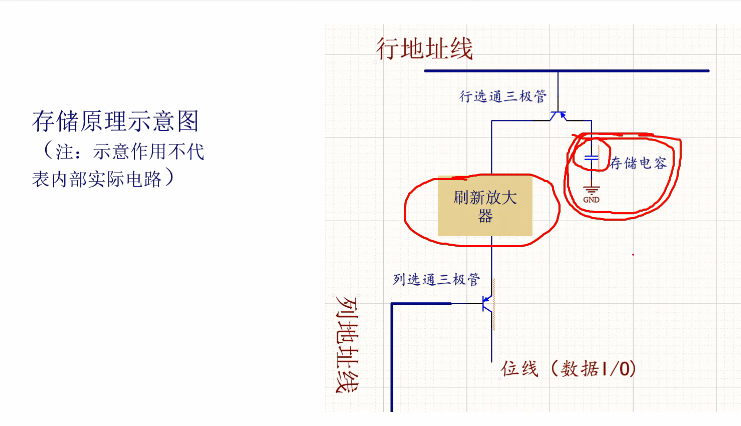

CL延迟时间内刷新放大器对数据进行刷新确保数据正确,CL=2,延迟两个时钟数据出现。

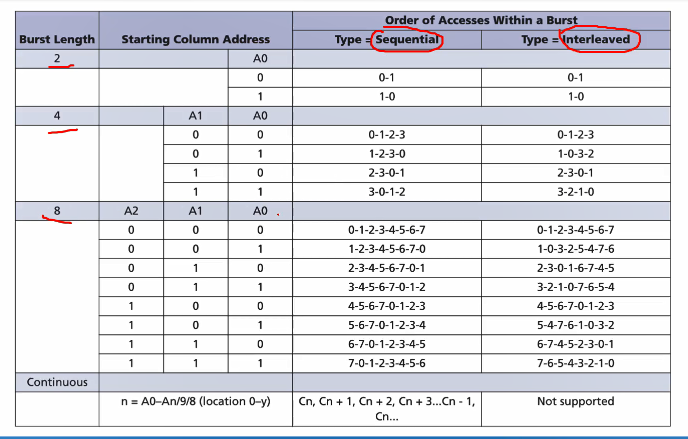

顺序和交替突发:

模式寄存器配置过地址线且回到数据存储地址,配置模式寄存器复用的是地址总线。

OP MODE:默认配置成 00,厂商用来升级做兼容用。

WB:写突发长度,0:读写一样的突发长度,1:单词写一个突发长度数据。

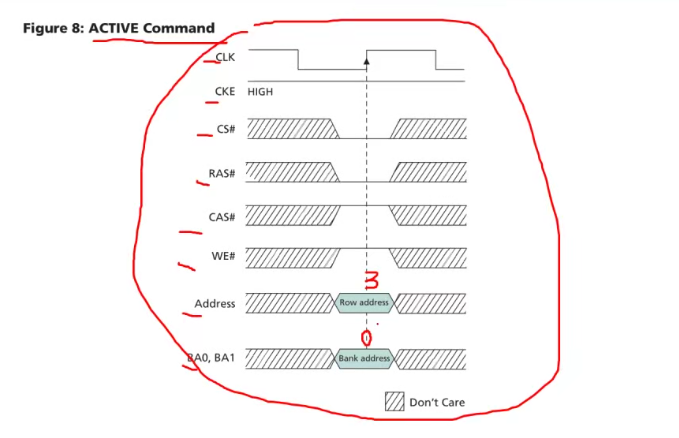

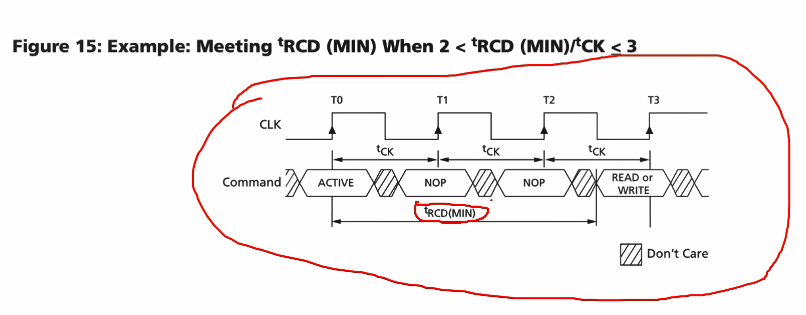

tRCD(ACT to internal read or write delay time) :初始化命令之后需要等待 tRCD 时间可以执行--->ACTIVE命令

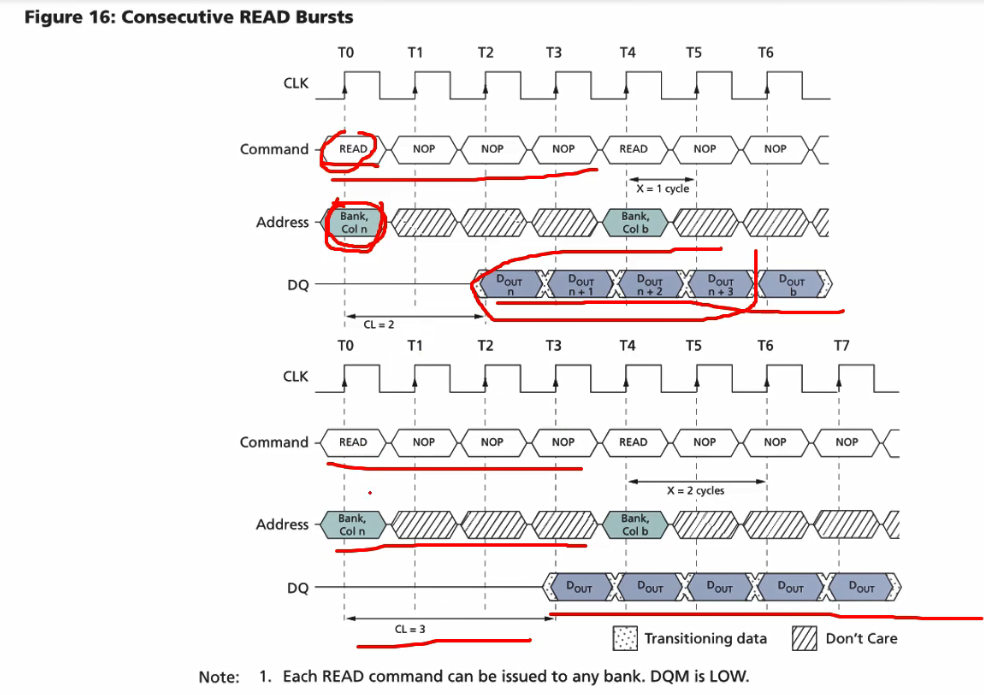

Consecutive READ Bursts

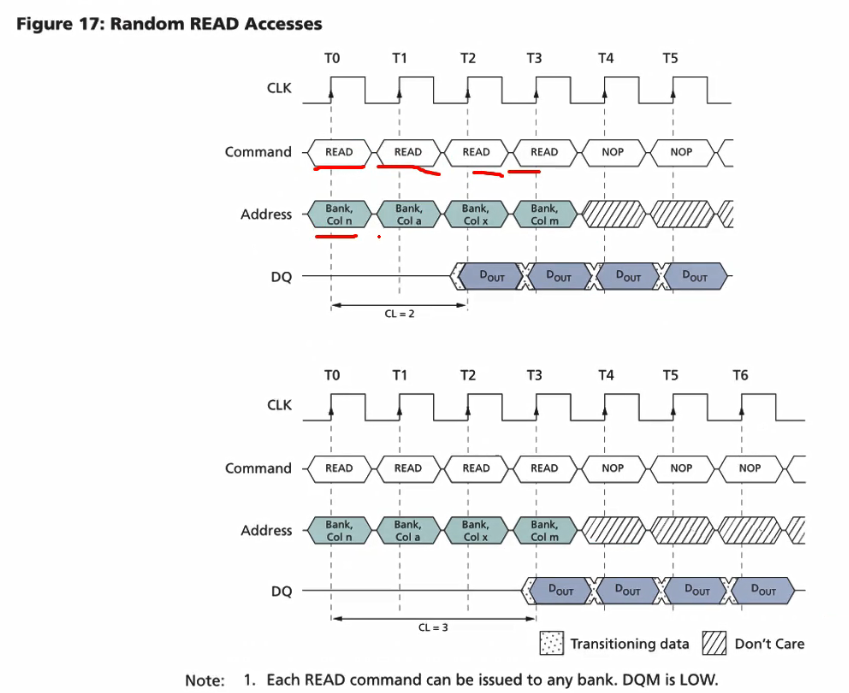

Random READ Accesses(非突发模式):

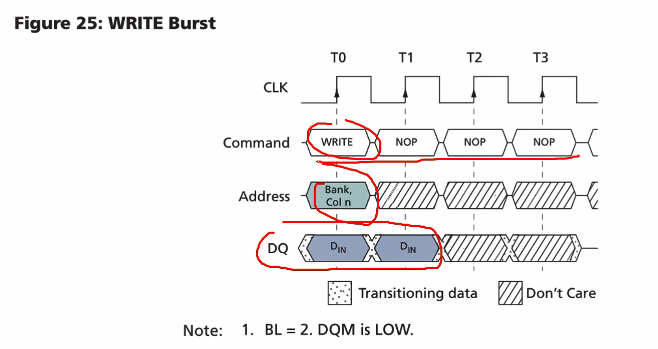

write burst:

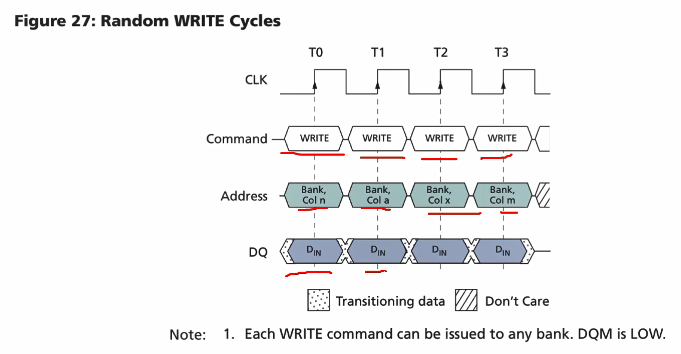

random write cycles:

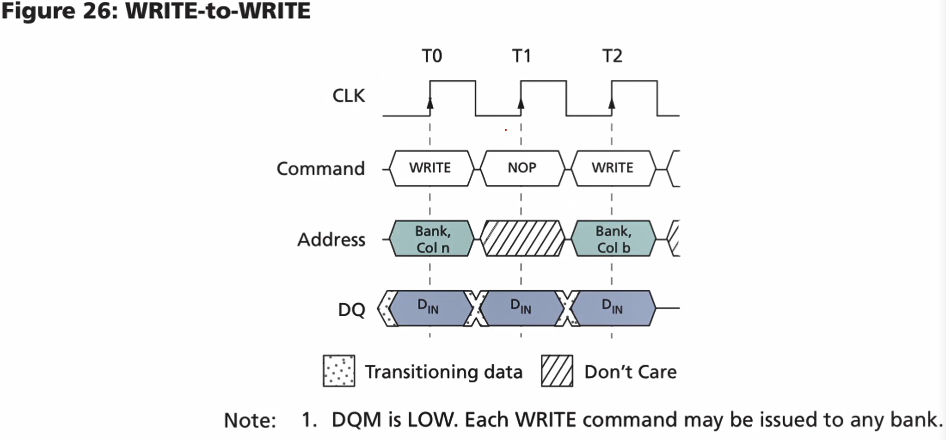

write to write:

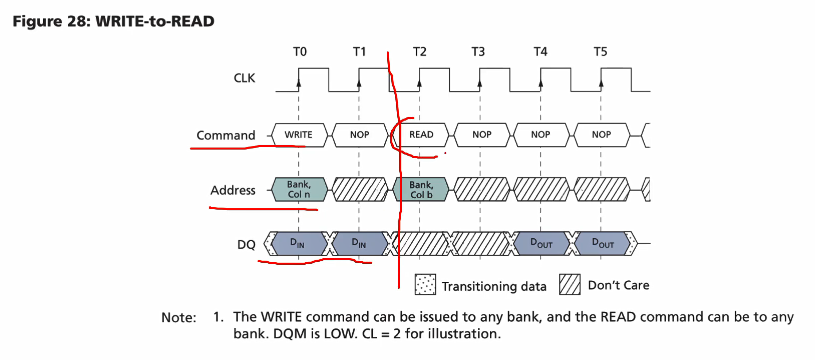

write to read:

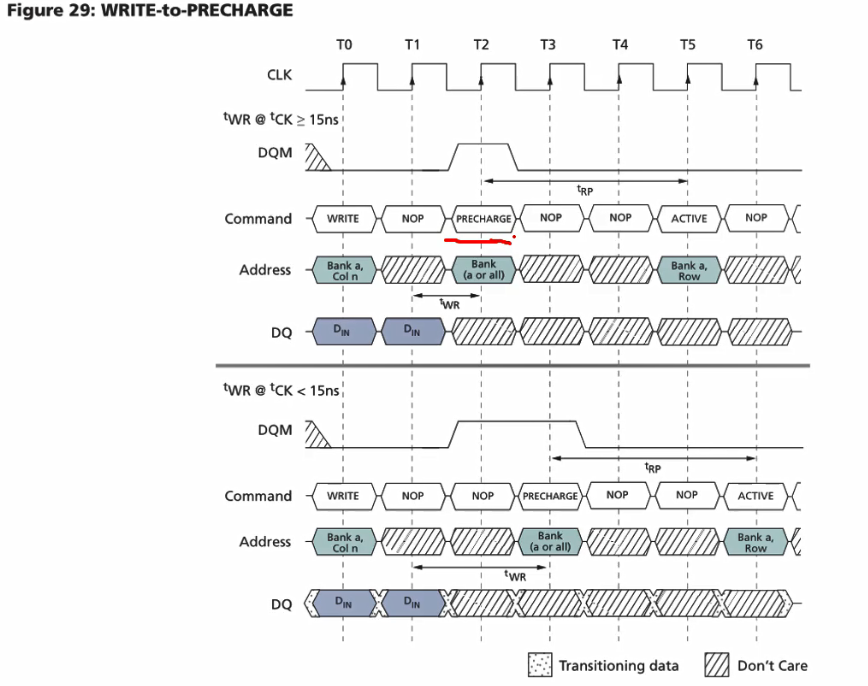

write to precharge:

tWR和tRP

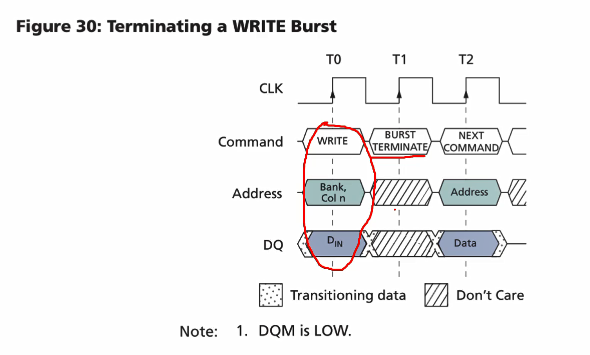

terminating a write burst:

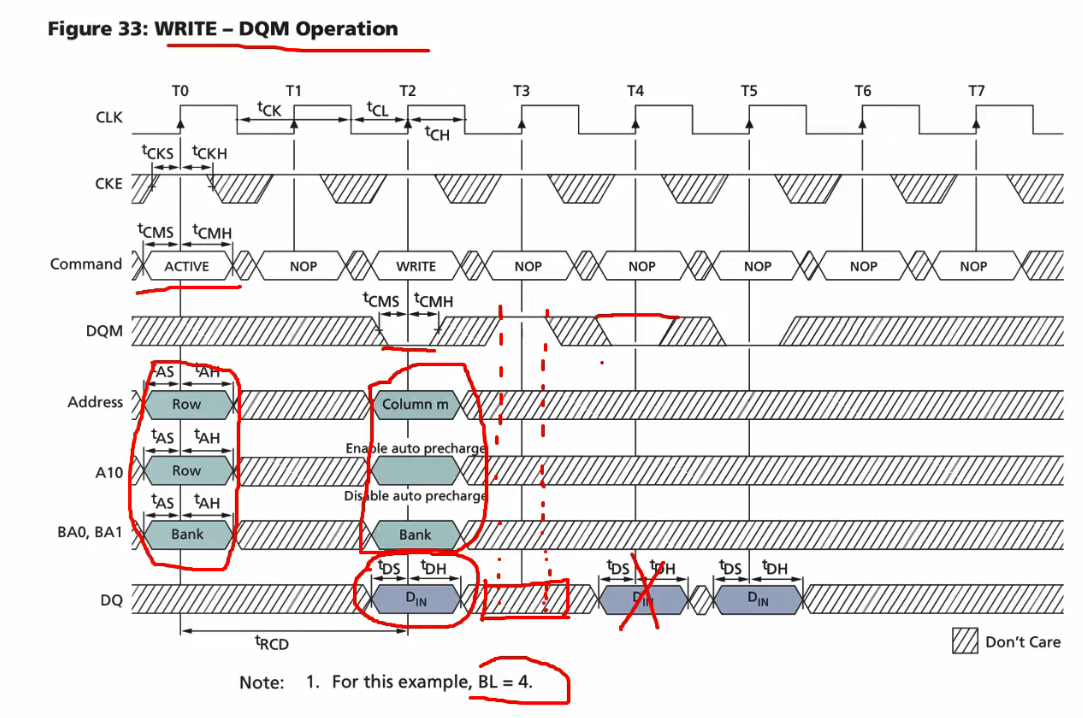

write-DQM(数据屏蔽) operation:

写数据屏蔽时会直接将写数据屏蔽掉,读数据屏蔽时会通过读数据寄存器方式屏蔽数据。

DQM在对应位置拉高屏蔽对应位。

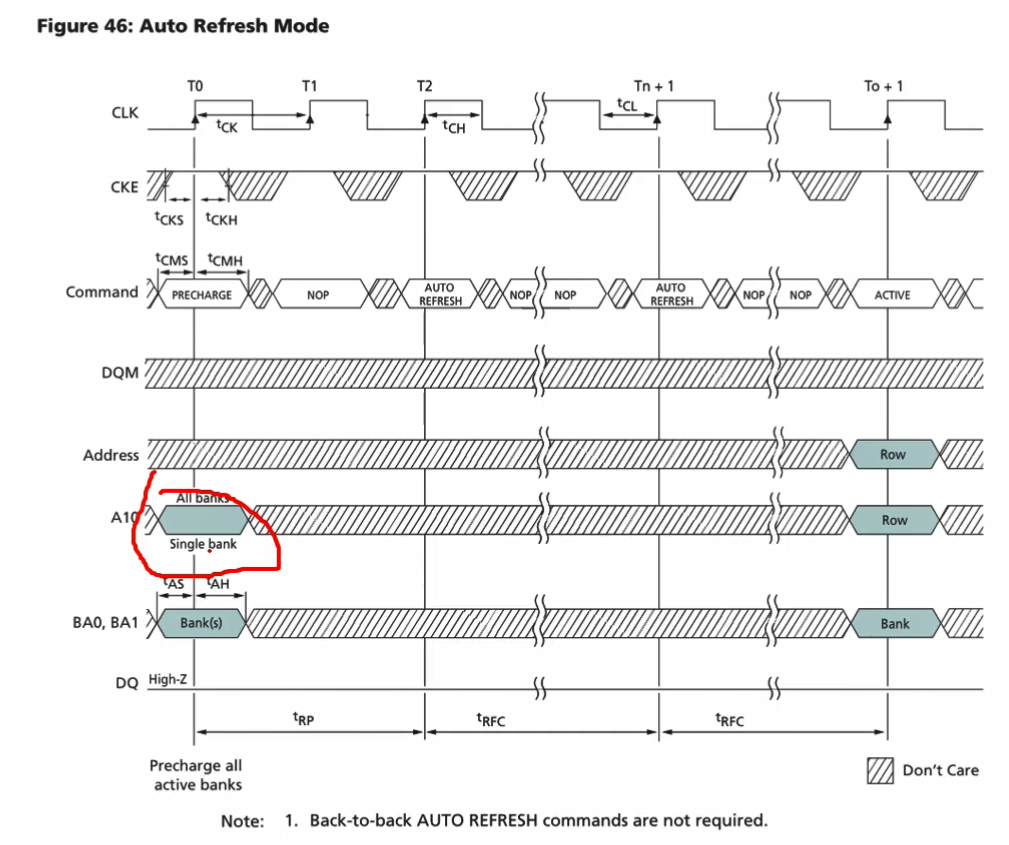

AUTO Refresh Mode:

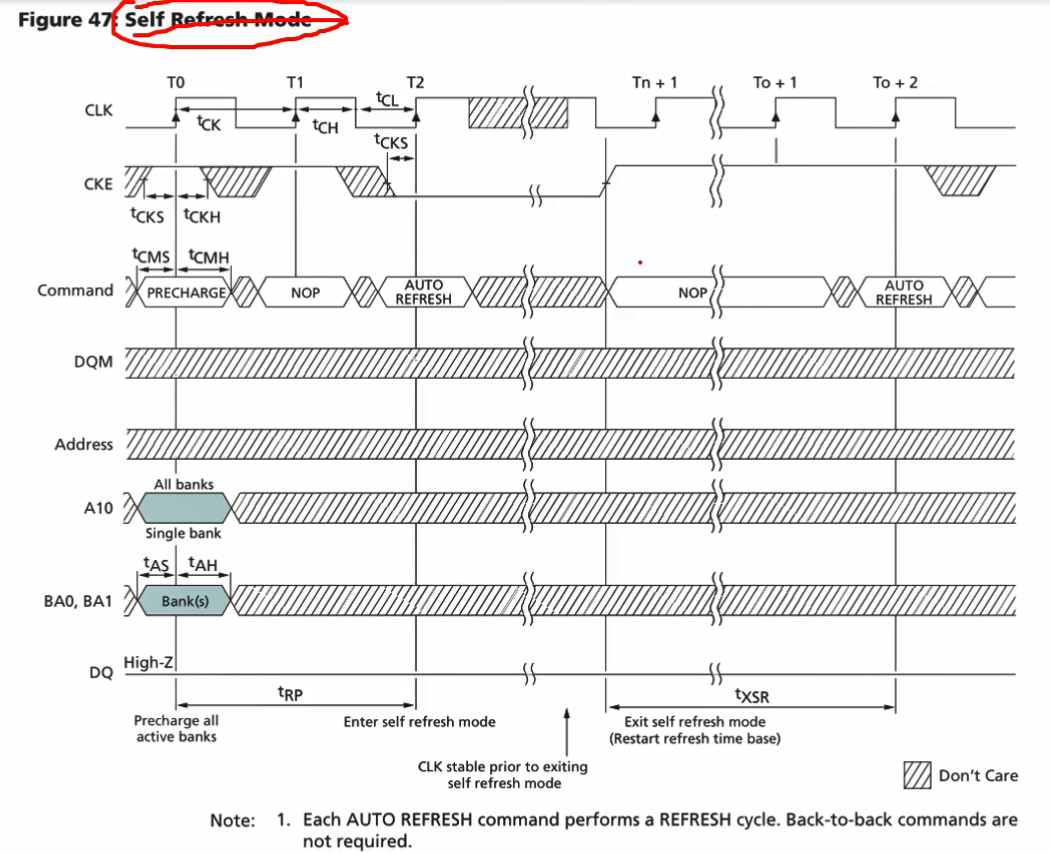

Self refresh Mode:

- SDRAM基本结构

- SDRAM的操作时序

- 从SDRAM到DDR SDRAM

- DDR的进一步发展