RAM相关概念

最近在学习DRAM相关知识,对channel, dimm, rank, chip, bank等结构概念傻傻分不清,偶然看到这篇阐述DRAM结构的好文,结构清晰,言简意赅,在此分享。

RAM

RAM(Random Access Memory)随机存取内存,之所以叫做“随机存取”,是因为相对于早期现行存储媒介(磁带?很久以前的)而言,因为磁带的存取是线性的(还记得快进/倒带 那个滋溜爽),存取时间由目前磁带位置和目的位置的距离而定(类似数据结构中的线性表)。需要转动刺头到应有的位置,因此距离越长,转的就越久了,读写时间也越久。而伟大的RAM没有这种限制,存取时间为固定值(类似数组这种下表式访问,下标就是地址),不会因为存储资料在memory中的位置而影响读取时间。

RAM大致可以分为两种:SRAM与DRAM,这两者基本原理上有相同的地方,都是将电荷存储到记忆体内部,由此针对不同的电荷存储0 or 1。SRAM(Static Random Access Memory)静态随机存储memory和DRAM(Dynamic Random Access Memory)有几点不同:SRAM的结构比较复杂,单位面积的容量少,存取速度很快;DRAM则结构简单,单位面积存储的容量比较多,存取时间相对SRAM慢,同时DRAM因为构造比较简单,存储的电荷会随着时间逐渐消失,因此需要定时再充电(Refresh),以保持电容存储的资料。

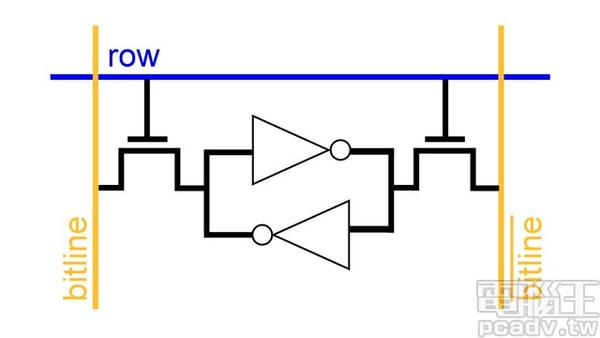

SRAM一个单位存储区的构造

SRAM一个单位存储区的构造 DRAM一个单位存储区的构造

DRAM一个单位存储区的构造

由图中的SRAM和DRAM构造可以知道,SRAM采用正反三极管+电容(flip-flop)构造存储器,DRAM则是采用电容式存储。因为SRAM和DRAM的种种特性上的不同,SRAM比较适合作为Cache,配合CPU快速存取使用,DRAM则适合作为主存而使用。

易失性存储器与非易失性存储器

易失性存储器(Volatile Memory)和非易失性存储器(Non-Volatile Memory)之间的差异在于,断电之后是否还可以保存内部存储的资料。易失性存储器的资料将会随着失去供电而消失,而非易失性存储器依然可以保存有内部的资料。

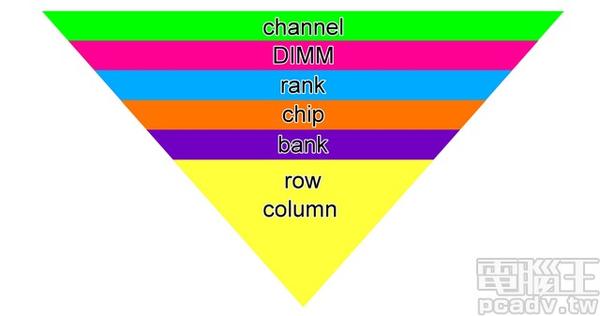

内存子系统

DRAM由于构造简单,高密度,作为电脑的主存非常适合。但由于主存通常放在CPU之外,从工厂出来的颗粒需要封装和组合之后才可以和CPU相连,因此从CPU到DRAM颗粒之间依次按层级由大到小分为channel > DIMM > rank > chip > bank > row/column。(和lz之前想的差不多,就跟先到哪条街道,哪个小区单元,哪个栋楼,几层几单元的地址格局一样)。下面,让我们来一一说明这些部分:

内存的结构(从上往下,由大到小)

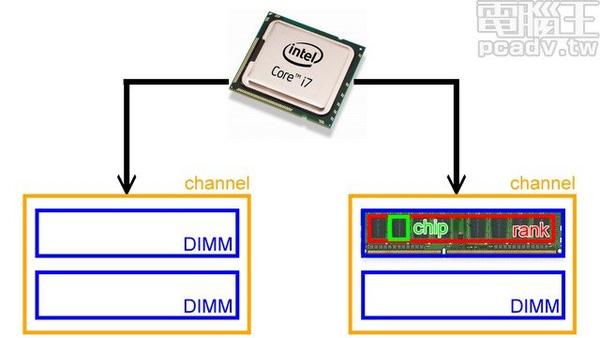

内存的结构(从上往下,由大到小) 内存从channel到chip的对应关系

内存从channel到chip的对应关系

这里特别要注意,rank和内存条的面没有必然关系,虽然图中这么画了,但是不要误导大家,就是示意一下,下面会有详细介绍。

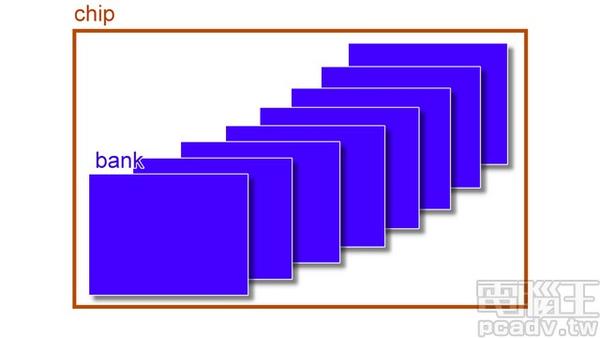

chip 再往下拆分为 bank

chip 再往下拆分为 bank

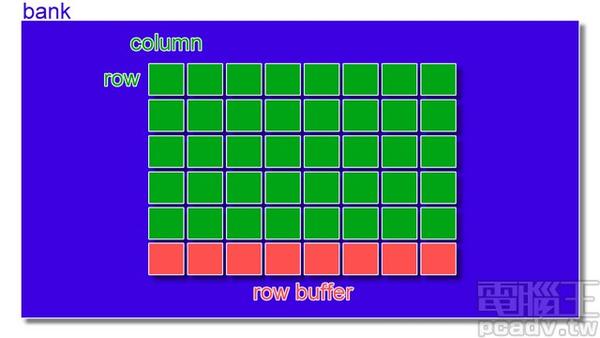

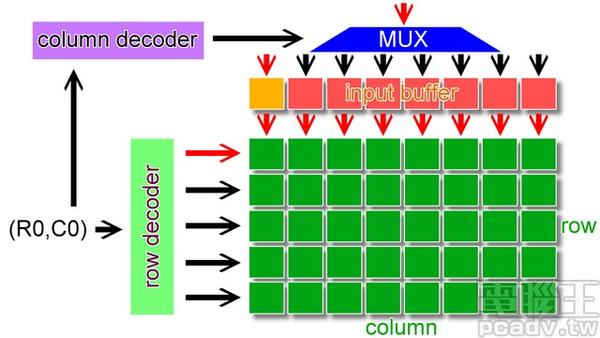

bank 再往下拆分就是一个个的存储单位,横排为row,纵列为column,每排column的下方都有一个row buffer,用来暂存刚刚读取出来的某个row排的资料。(是不是很简单,是不是很像你家小区的格局?Yeah!so easy ~)

bank 往下拆就是1个个的存储单元

bank 往下拆就是1个个的存储单元

横向1排称之为row, 纵向一列称之为column,每排column下方都有一个row buffer,用来暂存row的资料

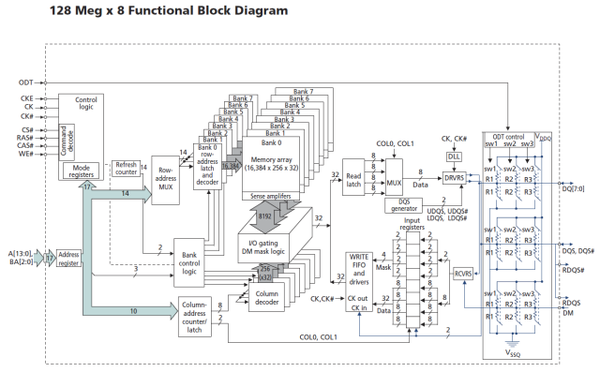

单一DRAM芯片的内部结构图

单一DRAM芯片的内部结构图

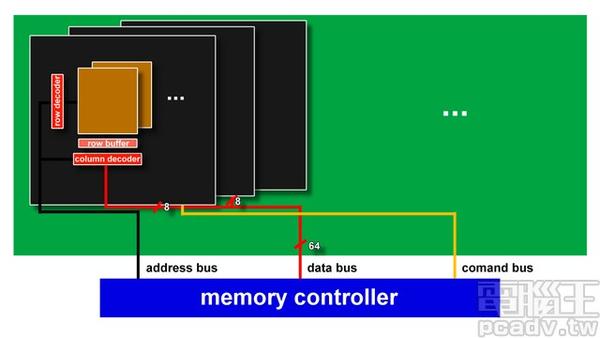

channel和 DIMM

从内存控制器出来之后,最先到达的是channel,每个channel都需要配有一组内存控制器,2个channel两个内存控制器,以此类推。而每个channel中能够有很多组DIMM(Dual In-line Memory Module),DIMM就是目前能够在消费市场上买到的大家平时能看到的内存模组。因为n多年前的主板必须购买内存颗粒(chip)自己插在主板上(想想知道为啥那时候大师都厉害了吧,这组成原理在实践中就得到了锻炼),然后发展出SIMM (Single In-line Memory Module),将多组内存颗粒(chip)焊在一块电路板上,成为内存模组,再将次电路板插在主板上。接着为了增加吞吐量,将一条内存模组的位宽从SIMM的32bit升级到DIMM的64bit,这个设计沿用至今。从内存颗粒过度到SIMM的时代,坊间曾出现替使用者将内存颗粒焊接到SIMM电路板上的私活,因为当时的内存条非常贵,所以稍微花点小钱就可以把内存颗粒换到新的电脑上。

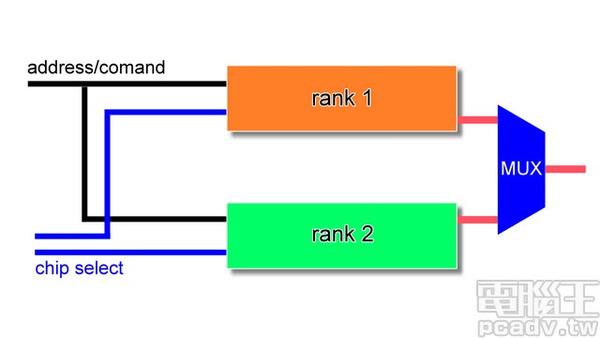

rank和chip

rank指的是连接到同一个cs(Chip Select,片选)的所有内存颗粒chips,内存控制器能够对同一个rank的所有chips同时进行读写操作,而在同一个rank的chip也分享同样的控制信号。以目前的电脑来说,因为一组channel的位宽是64bit,所以能够同时读写8byte的资料,如果是具有ECC功能的内存控制器和ECC内存模组,那么一组channel的位宽就是72bit。

rank1和rank2共享同一组addr/command信号线,利用cs片选线选择读/写的那一组,之后将存储内容经由MUX多路器送出。

很多人有错误的理解,常以chip的数量或是以内存模组的单/双面对rank进行判断,但实际上应该以内存控制器和内存颗粒的规格进行判断。目前家用PC的内存控制器通道绝大部分是64bit宽,内存颗粒的位宽是8bit。因此8颗颗粒就可以满足内存控制器的需求,也就是一组rank。但偶尔也有以16bit位宽的内存颗粒制成的内存模组,此时4个颗粒chip就是一组rank。

这在采用Intel H61/H81 芯片组 和 传统单channel的主板时需要特别注意,因为Intel限制H64/H81每个channel仅能支持2组rank,而不是4组rank,部分主板每个channel又做了2组内存模组插槽,造成部分使用者同组channel放入2条内存模组(内存条)时能够识别全部的内存容量(对于双面单rank的内存模组是这样),然而部分使用者则仅能识别一半的容量(双面双rank的内存模组)。

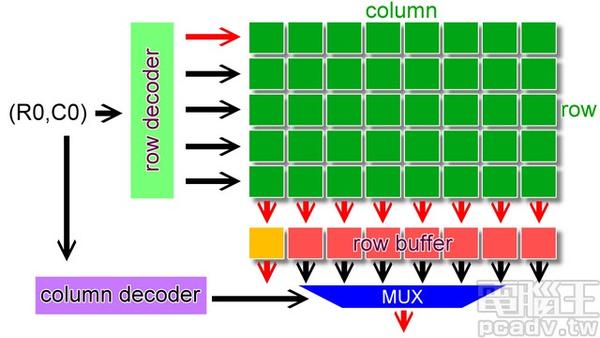

bank,row,column

bank再往下分就是实际存储单元的电路,一般来说横向选择排数的线路称为row(row enable, row select, word line),纵向负责传送信号的线路称为column(bit line),每组bank的下方还会有个row buffer(sense amplifier),负责将读出的row内容暂存,等待column位址送到后输出正确的位元,以及判断存储的内容是0还是1。

一个bank的读取操作

一个bank的读取操作 一个bank的写入操作

一个bank的写入操作

内存的读写方式

上图标明了内存的读写方式,读取时首先内存控制器将1组位址现传到内存上,控制器跟着传送控制信号;如果是多rank的情况,CS也会送到对应信号选择的目标rank上。接着由于每个rank是由多个chip组成,每个chip仅负责部分的资料读取,chip接收到位址信号后,将位址放入内部的row/column解码器找出对应的bank位址(每家厂商每款产品内部的bank组合可能不同,因此相应地也会略有不同),接着开启row线,同一排row的内部内容就会流到row buffer内部,row buffer判断信号为0或是1之后就输出存储内容。

写入时除了位址资料以外,还会传送欲写入的内容至芯片内部的input buffer,同样的也是按照row/column解码器找出对应位址之后写入。

内存控制器和DIMM之间的线路关系

内存控制器和DIMM之间的线路关系

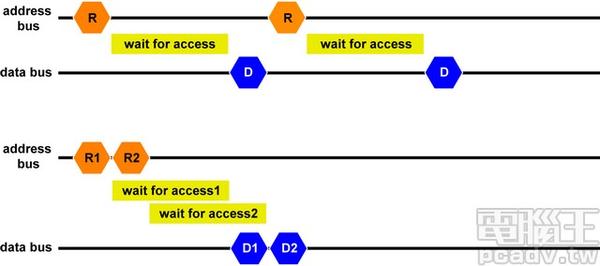

越多越好,加速读写能力

家用电脑的内存控制器已经进入双通道内存控制器多年,加速原理为增加位宽,达到同时读写更多资料的能力。

另一种增加频宽的方法就是减少延迟,利用多个chip或是bank达成。一般的内存读取延迟为 命令下达 + 内存读取延迟 + 输出内容,如果命令下达延迟为2ns,内存读取延迟为10ns,输出内容延迟为2ns,那么读取两笔资料的延迟就是 (2+10+2)* 2 = 28ns。

如果能够将资料拆分到2颗内存颗粒上,那么这两笔读取延迟将降低至2+2+10+2=16ns,因为不需要等到前面一笔资料的读取完成才发出下一笔的读取命令,在第一笔资料进入内存读取时就可发出。这种概念也可应用到目前的SSD上,较多的ce分装的快速记忆芯片,通常都比较少ce封装的芯片来得快。

由时序图可以知道,下面那种尽量拆分内存空间的作法,可以大幅减少延迟。

参考文献:

浙公网安备 33010602011771号

浙公网安备 33010602011771号