建立保持时间计算公式

笔者这段时间在找工作中发现,关于时序分析的基础概念,时序关系表达式及时序违例计算几乎是每个IC/FPGA岗位笔试面试的必考内容。就此,从建立保持时间裕量出发,夯实基础。本文主要是对之前转载博客【时序约束学习笔记1】Vivado入门与提高--第12讲 时序分析中的基本概念和术语 做一些总结和个人理解。

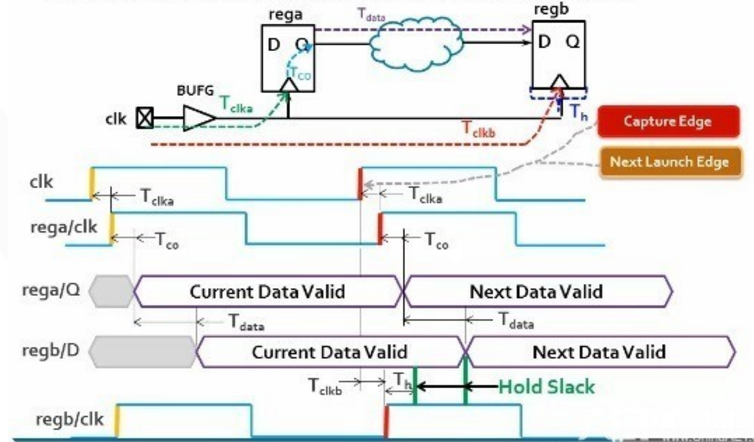

还是直接用之前转载博客中图片:

图中的两个寄存器中间加一段组合逻辑电路是时序分析的经典模型,主时钟clk前后两个上升沿分别叫启动沿和锁存沿,是时序分析的起点和终点。下边一步步推导出建立时间和保持时间裕量及常用通式。要注意,下边的“时间”均表示一个时刻。且为了方便,将启动沿时刻定义为0时刻,故锁存沿为T时刻。

1 时钟到达时间:时钟有效沿到达带二个寄存器的时刻。

Tcd = capature Edge + Tclkb = T + Tclkb

2 数据到达时间:数据到达第二个寄存器的时刻。

Tdd = launch Edge + Tclka + Tco + Tdata = Tclka + Tco + Tdata

3 数据需求时间(建立时间需求):为满足建立时间要求,数据最晚到达的时刻。

Tsu,req = Tcd - Tsu = T+ Tclkb - Tsu

4 数据需求时间(保持时间需求):为了满足保持时间要求,数据最早更新的时刻。

Th,req = Tcd + Th = T + Tclkb + Th

5 建立时间裕量:为满足建立时间要求,富余出来的时间段长度。

setup slack = 建立时间需求 - 数据到达时间

= Tdd - Tsu,req = T+ Tclkb - Tsu - Tclka - Tco - Tdata

= T + T△ - Tco - Tdata - Tsu

6 保持时间裕量:为了满足保持时间要求,富余出来的时间长度。

hold slack = 数据到达时间(下一次)- 保持时间需求

= Tdd' - Th,req = Tclka + Tco + Tdata + T - T - Tclkb - Th

= -T△ + Tco + Tdata - Th

同步数字电路就系统中,每条时序路径必须满足建立时间裕量和保持时间裕量 ≥ 0,否则无法满足建立与保持时间要求,引起系统不稳定甚至无法正常工作。常用通式(不考虑时钟偏抖):

1 通过建立时间裕量引出系统最高时钟频率

setup slack≥0:T - Tco - Tdata - Tsu ≥ 0 -->T ≥ Tco + Tdata + Tsu

2 通过保持时间裕量得到保持时间与时序参数关系

hold slack≥0:-T△ + Tco + Tdata - Th ≥ 0 --> Th ≤ Tco + Tdata

还不赶紧背下来!

浙公网安备 33010602011771号

浙公网安备 33010602011771号