时序分析基本概念介绍——SDC概述

今天我们要介绍的时序概念是设计约束文件SDC. 全称Synopsys design constraints. SDC是一个设计中至关重要的一个文件。它对电路的时序,面积,功耗进行约束,它是设计的命脉,决定了芯片是否满足设计要求的规范。Timing工程师在release sdc时必须非常小心,一个错误的false path或者case constant就有可能导致整块芯片不工作。

Timing Constraint 为使用者所给定,用来检验设计电路时序的准则。我们在做STA前首先要了解各种约束是做什么的。

Timing Constraint按照它们的用途,大致分为以下几类:

(1)描述芯片的工作速度,即时钟的频率,包括create_clock,create_generated_clock等

(2)描述芯片的边界约束,包括set_input_delay, set_output_delay等

(3)描述芯片的一些设计违反rule(DRV),包括set_max_fanout,set_max_capacitance, set_max_transition等

(4)描述设计中一些特殊的路径,包括set_false_path,set_multicycle_path等

(5)描述设计中一些需要禁止的timing arc,例如set_disable_timing

需要注意的是,设计的不同阶段我们使用的sdc都有所不同(当然,有的公司比较强大,会有一套golden sdc)。比如说,综合时由于模型的粗糙,我们会选择过约sdc,将时钟频率设得更高一些;CTS之前,由于skew的不确定性,通常我们也会加大uncertainty;还有signoff tool与PR工具correlation问题,margin的设置也会不一样。

那我们如何去合理定义一个设计的sdc呢?

这是一项非常有难度的工作,其实常用的sdc命令就以下几条,但要准确运用他们可不容易。

clock相关:

create_clock

create_generated_clock

set_clock_uncertainty

set_clock_groups

set_input_delay

set_output_delay

系统接口相关:

set_input_transition

set_load

set_driving_cell

时序特例相关:

set_false_path

set_multicycle_path

逻辑赋值相关:

set_case_analysis

接下来几篇文章会分别介绍这些命令

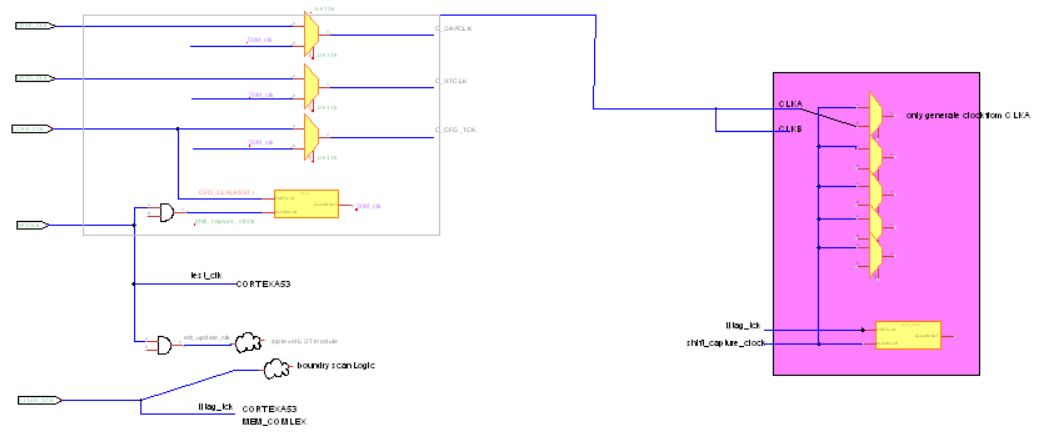

还有一个最重要的前提条件是:我们必须要尽早有一张结构清晰的clock结构图。而且是越早做越好。clock结构最好是让前端设计人员给你,当然也可以通过cad软件自己去画一张。这边介绍一个比较好用的绿色小软件TinyCad. 简单易学~~

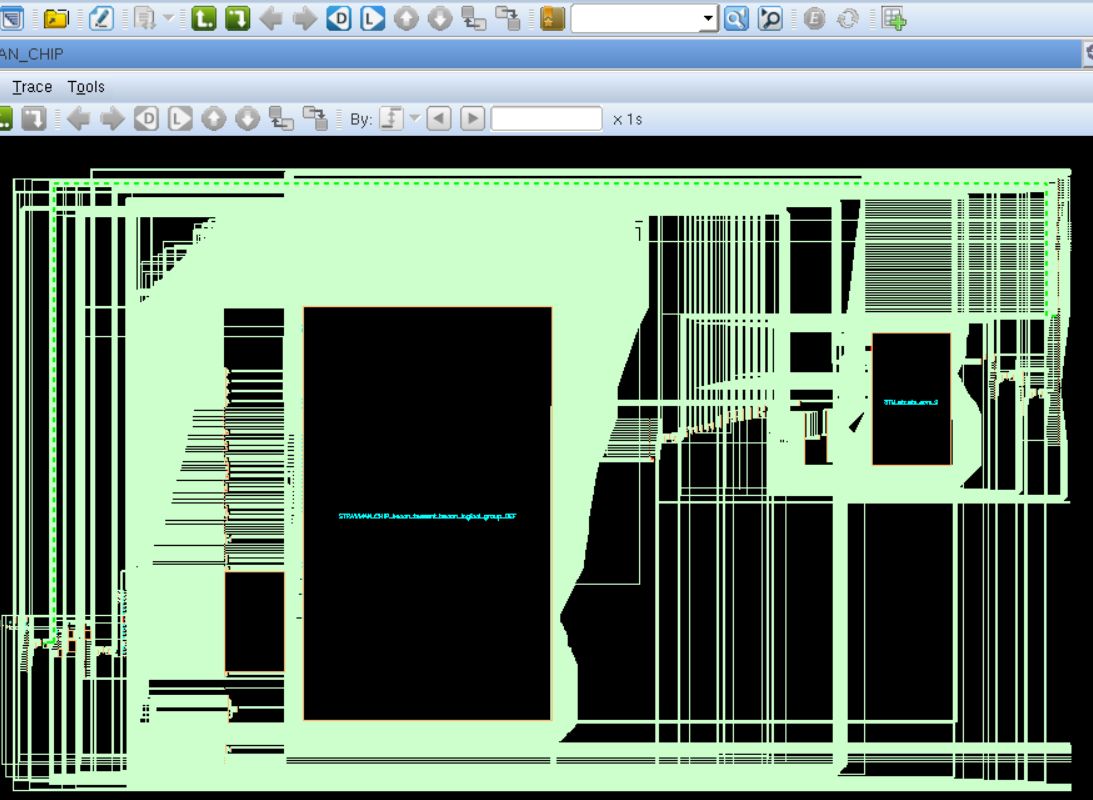

也可以通过Verdi来trace电路结构,这也是很方便的,只需要读入设计的网表就行

好了,今天就大致介绍一下sdc的基本概念,以后会分别介绍几个重要的sdc命令。

浙公网安备 33010602011771号

浙公网安备 33010602011771号