dsp48的演变历史

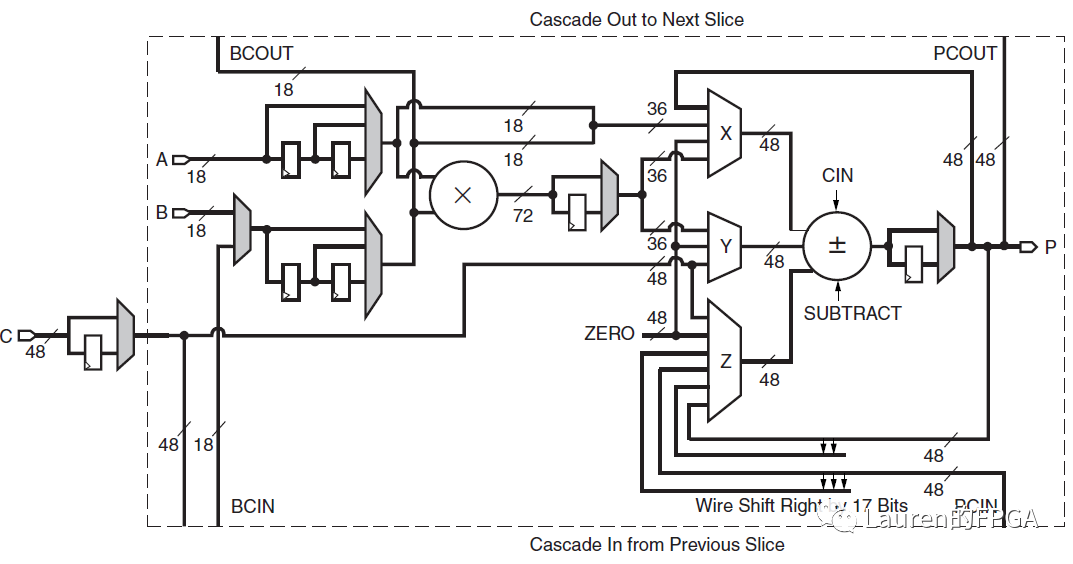

DSP48最早出现在XilinxVirtex-4 FPGA中,但就乘法器而言,Virtex-II和Virtex-II Pro中就已经有了专用的18x18的乘法器,不过DSP48可不只是乘法器,其功能更加多样化。DSP48基本结构如下图所示(图片来源:ug073, Figure 2-1)。DSP48中的核心单元是18x18的乘法器。从图中不难看出,DSP48可实现基本数学函数P=Z±(X+Y+CIN)。这里X、Y和Z是图中3个MUX的输出。根据图中MUX的输入,上述数学函数可以变为P=A*B+C或P=A*B+PCIN,后者需用级联DSP48。因为PCIN和PCOUT是专用走线相连。同时,与Virtex-II不同,Virtex-II中,相邻的DSP48和Block RAM共享互连资源,而在Virtex-4中,DSP48和Block RAM有独立的布线资源。

此外,从资源角度看,Virtex-4SX55包含的DSP48最多,一共8列512个DSP48,在全流水模式下,可运行到的最高频率为500MHz。

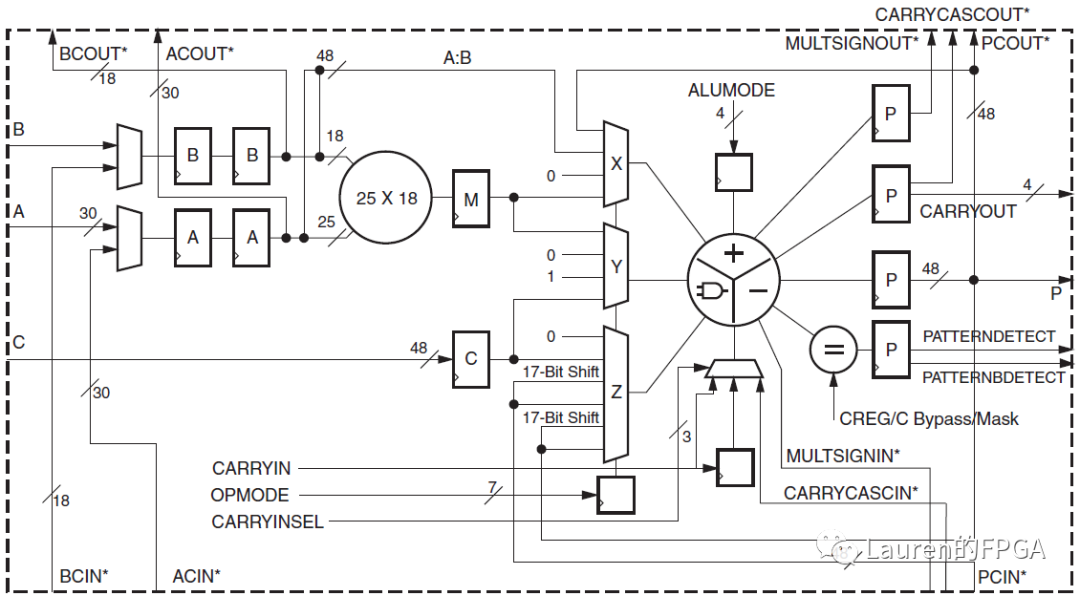

在Virtex-5中,引入了增强型DSP48,称之为DSP48E,其基本结构如下图所示(图片来源ug193, Figure 1-1)。这种增强体现在以下几点:乘法器变为25x18;A端口变为30位,其中低25位可用于乘法器的输入,A和B可拼接为48位,从而可实现{A,B}+C(两个48位数据相加);乘法器之后不再是简单的累加器,而是功能更为多样的ALU(算术逻辑单元),可实现算术运算和逻辑运算。这里特别介绍一下ALU,ALU支持SIMD功能(Single InstructionMultiple Data),使得ALU可配置为2个24位的加法器或者4个12位的加法器。从资源角度看,Virtex-5 SX240T包含的DSP48E最多,共1056个,在全流水模式下,可运行到的最高频率为550MHz。

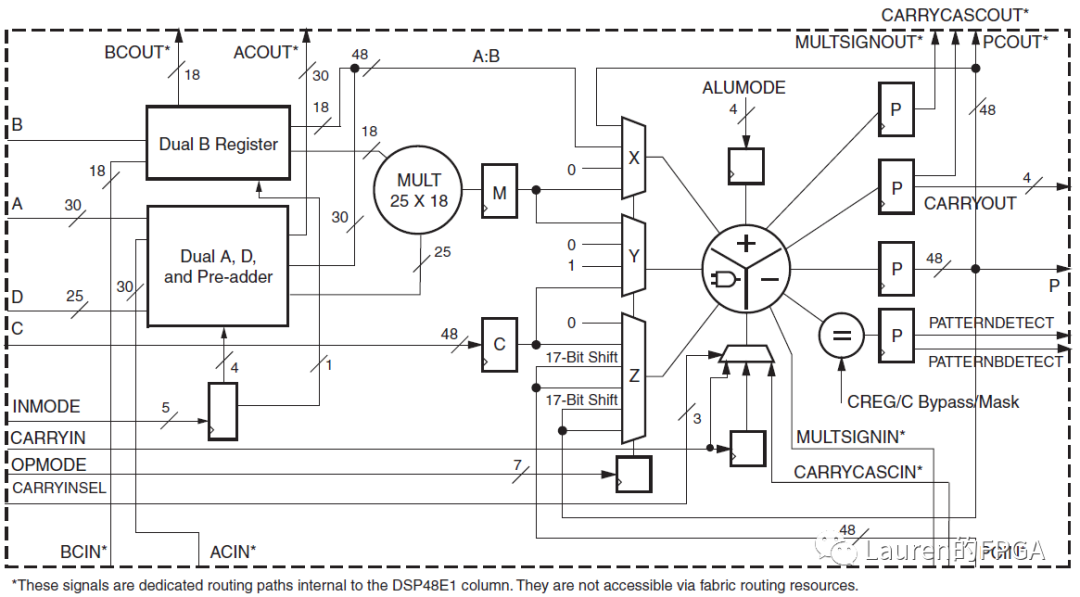

在Virtex-6和7系列FPGA中,DSP48E功能进一步增强,称之为DSP48E1,其基本结构如下图所示(图片来源ug369, Figure 1-1)。最显著的变化是在DSP48E中添加了预加器(可实现25位的加法运算),这对于系数对称的滤波器而言非常有利,可将乘法器资源减半。

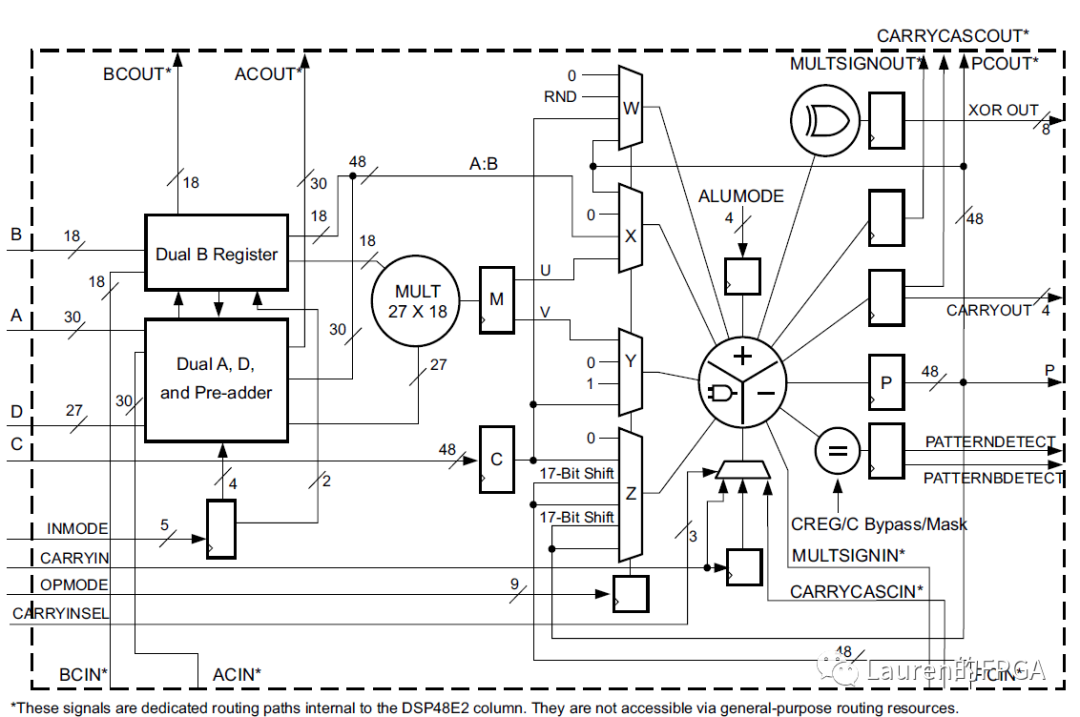

在UltraScale和UltraScale Plus系列FPGA中,引入了DSP48E2,其基本结构如下图所示(图片来源ug579,Figure 2-1)。相比于DSP48E1,其中的乘法器变为27x18,端口D的位宽也由25位变为27位,这样预加器可支持27位的加法运算。预加器的输出可同时送给乘法器的两个输入端口,从而很容易实现平方运算。同时,增加了一个MUX,对应图中的W。ALU可实现Z+W+X+Y。

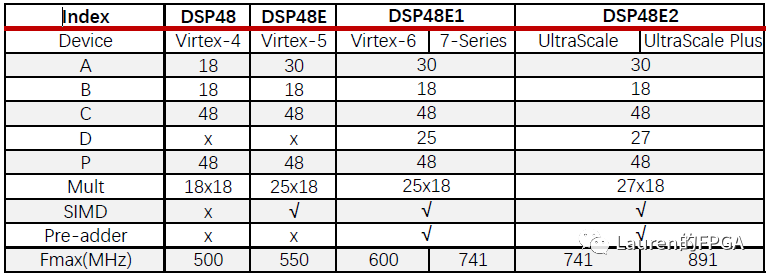

对比DSP48、DSP48E、DSP48E1和DSP48E2,如下表所示。

浙公网安备 33010602011771号

浙公网安备 33010602011771号