FPGA基本结构之slice

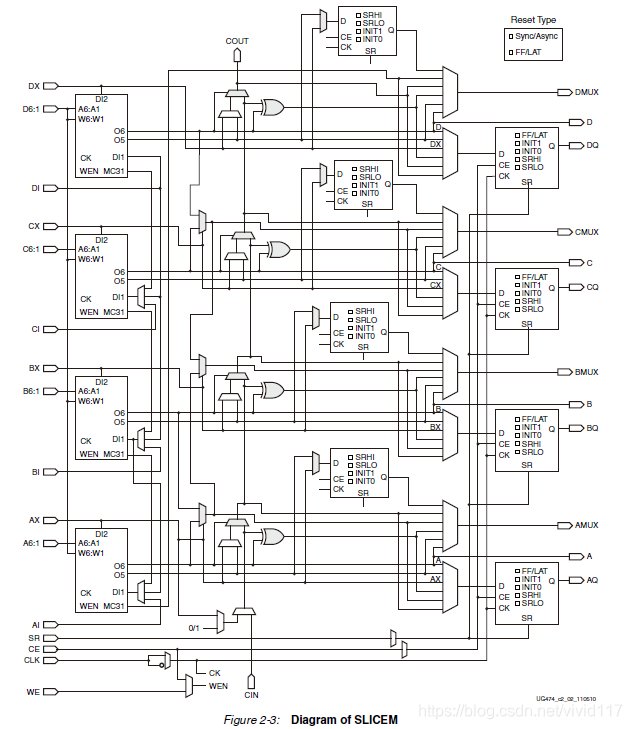

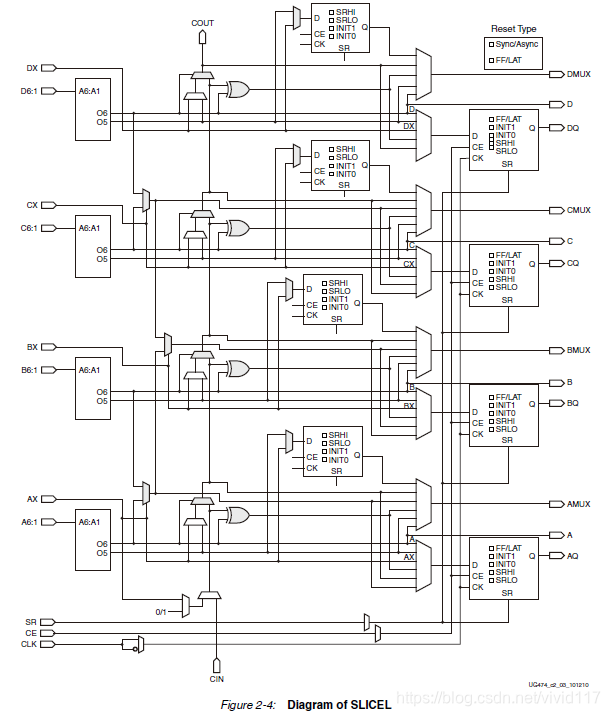

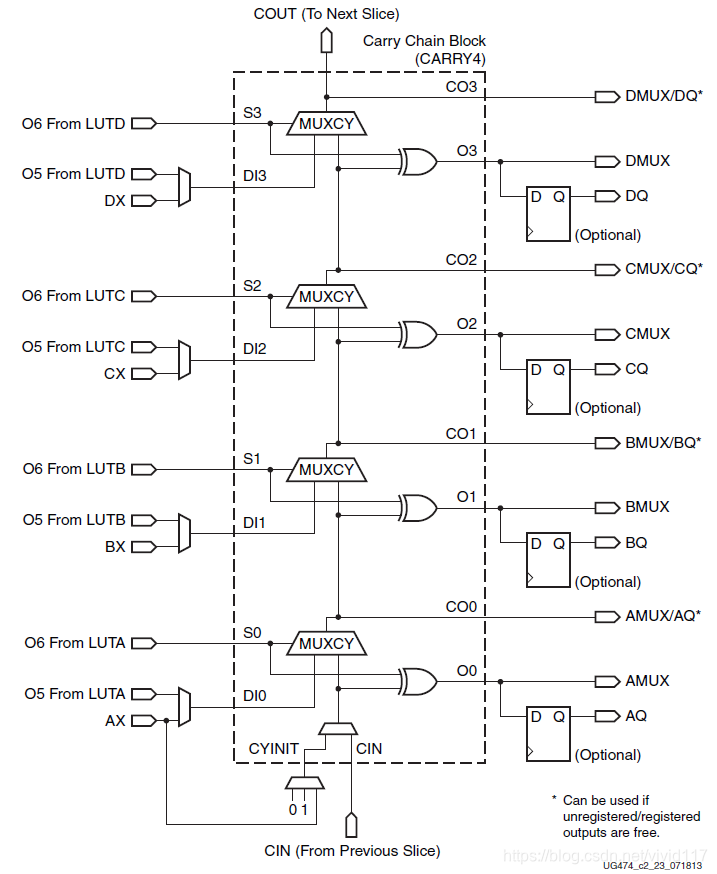

可以看到 一个 slice 有4个部分:4个6输入查找表,3个选择器,一个CARRY4进位链,还有8个寄存器。

其中CARRY4可以用来实现加法器,具体如何实现很容易搜到。IO引脚 是可以直接接入CARRY4的DI端的。(IO的输入端可能是下图的AX,BX,CX,DX ?猜测)

浅谈XILINX FPGA CLB单元 之 进位逻辑链(CARRY4原理分析,超前快速进位逻辑结构)

数据选择器:

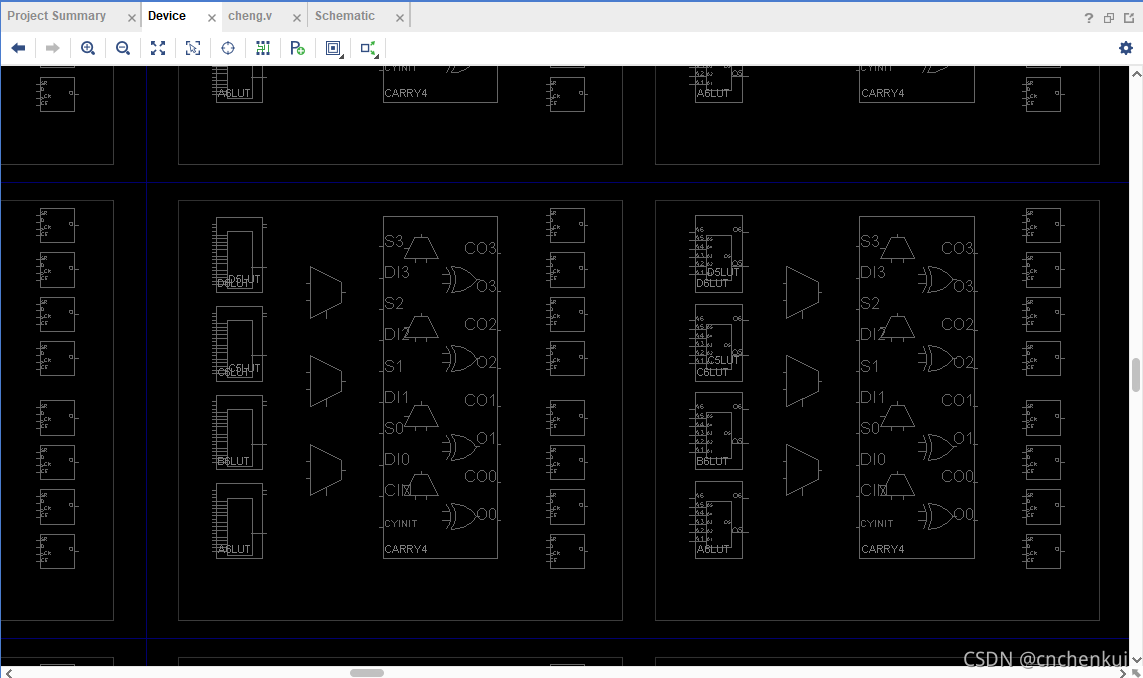

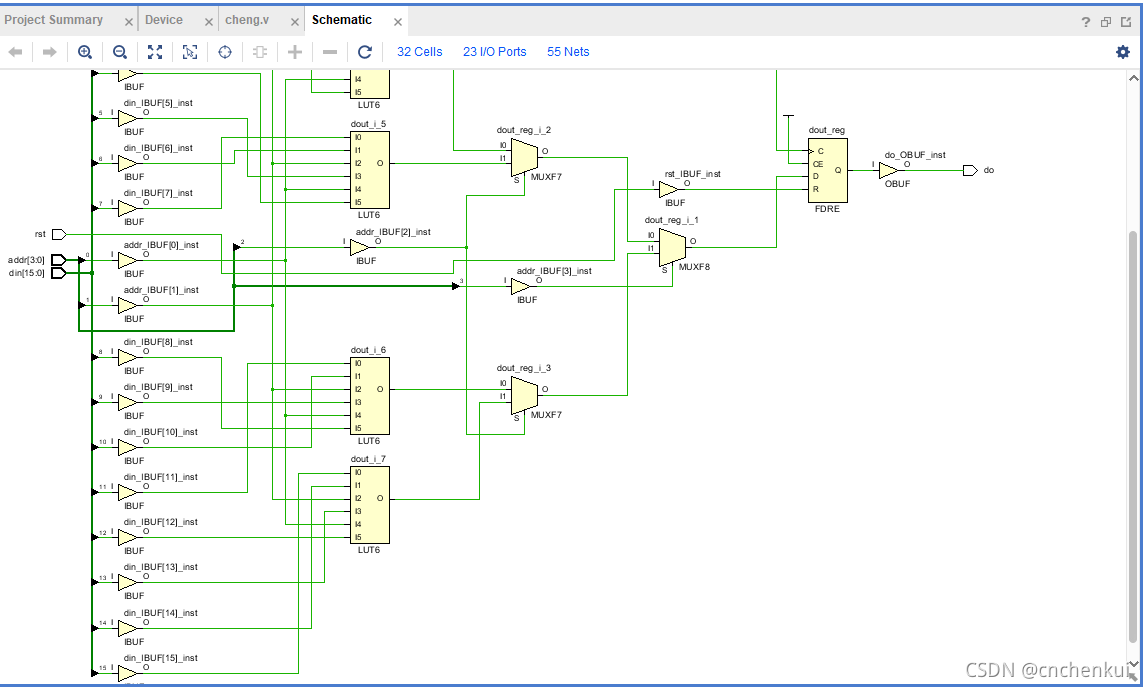

下图是一个16选1的数据选择器的综合实现图,可以看出,sel信号是能够直接通过IO接入数据选择器的。而且可以看出,选择器MUXF的输入是只能从查找表输出的,并不能从IO送过来。因此综合工具在实现数据选择器的时候,会首先使用LUT,这样就可以避免使用MUXF的资源。因为如果直接使用MUXF资源的话,但输入只能从LUT获得,LUT资源同样也被消耗了。 但如果实现的功能查找表无法实现时,就会使用 MUXF,避免使用其他的SLICE资源。

关于SLICEM:

sliceM的LUT可以配置为 分布式RAM、ROM、移位寄存器,LUT6可以配置为32bit的移位寄存器,也就是说32位的移位寄存器只需要消耗一个LUT

浙公网安备 33010602011771号

浙公网安备 33010602011771号