clock gate

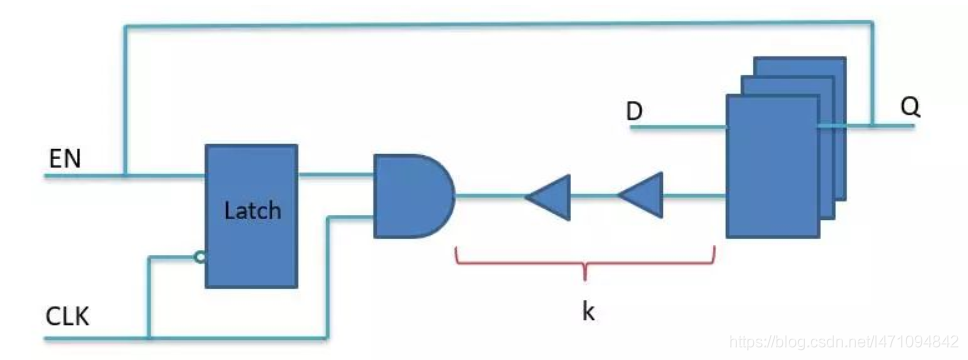

今天我们要介绍的时序分析概念是clock gate。 clock gate cell是用data signal控制clock信号的cell,它被频繁地用在多周期的时钟path,可以节省功耗。如下图所示:

我们经常说的reg2clockgate path的setup和hold检查,就是指:clock gate上enable信号要比clock信号提前到达一段时间和保持一段时间。

通常,clock gate上的setup会比较难收敛,因为如下图对于clock gate的timing path,天然会穿在skew k;clock tree必然不balance。在实际设计中,我们一般会尽量将clock gate 单元放在寄存器附近以减小skew。也可以采用set_clock_gating_check,加大对clock gate timing的约束。

常见的clock gating cell有ICG cell(integrated clock gating cell)和clock gating logical cell(and+low latch)。现在一般library库里都带有ICG cell了,clock gating logical cell已经不常用了

对于clock gating cell,synthesis前就会插入,本身和CTS没太大关系,

一般只要确保clock timing check打开的就行,就是如下global变量设成true

timing_enable_clock2clock_clockgating_check

另外,CTS工具会对其做clone,declone操作.

ICG cell Clone: 受相同ICG cell控制的时序单元较多或者分布不均匀时,就会导致ICG cell连线过长,这时可以通过clone ICG cell进行优化

ICG cell De-Clone: 受相同ICG cell控制的时序单元较少,就会导致ICG cell数量过多,设计density增大。这时可以通过De-clone ICG cell进行优化

1、结构图(锁存器,与门,D触发器)

latch或reg:用于同步使能信号,防止出现亚稳态和毛刺。

与门:使能信号无效时,关断模块输入时钟。

D触发器:简化的reg。

2、为什么需要clk gate?

模块不工作时,clk翻转浪费功耗。模块/reg相当于一个DFF,但是en为高时,模块才工作,clk才有效。不工作时,clk翻转浪费功耗。

3、如何clk gate?

将一直翻转的时钟变为en有效才翻转的时钟,即将CLK转化为CLK_G。

4、基于与门的clk gate(会有右图所示问题)

5、避免毛刺glicth的clk gate

en信号的source reg用下降沿触发,en信号从产生到与门之前有半个时钟周期,可以稳定毛刺。

*5、ICG

作用:采用使能信号EN控制数据是否有效,使能消耗无效时保持输出。

参考文献:深入浅出ClockGating - 操作 (基于基本CELL的clock gating形式)

时序分析基本概念介绍--clockgate_简单同学-CSDN博客_clock gate