FPGA之锁存器

前言

- 数字同步逻辑中应尽量避免产生锁存器,因为锁存器容易引起竞争、冒险,同时静态时序分析工具也很难分析穿过锁存器的路径。FPGA里面的latch是由查找表产生的。

- 由于fpga生成的latch路径和时延不确定,因此fpga内不建议用latch(除非一些场景必须使用组合逻辑和latch解决,且对latch的应用很了解)。

- 芯片IC设计的路径和时延是固定的,因此IC设计是可以使用latch的。

一、对锁存器理解

1、锁存器的概念

- 锁存器是一种在异步时序电路系统中,对输入信号脉冲电平敏感(电平触发)的存储单元,在时钟脉冲的电平作用下改变状态。

- 锁存器在数据未锁存时,输出端的信号随输入信号变化,就像信号通过一个缓冲器;一旦锁存信号有效,则数据被锁存,输入信号不起作用。因此,锁存器也被称为透明锁存器,指的是不锁存时输出对于输入是透明的。

- 一个锁存器可以存储1bit的信息,通常,锁存器会多个一起出现,如4位锁存器,8位锁存器。

2、锁存器与触发器的相同点和区别

(1)相同点

- 锁存器和触发器都是具有记忆功能的二进制存贮器件,是组成各种时序逻辑电路的基本器件之一。

- 由于latch和FF(Flip-Flop)二者都是时序逻辑,因此其输出不但同当前的输入相关,还与上一时间的输出相关。

(2)区别

- latch同其所有的输入信号相关,当输入信号变化时latch就变化,没有时钟端;DFF受时钟控制,只有在时钟触发时才采样当前的输入,产生输出。

- latch由电平触发,非同步控制,在使能信号有效时latch相当于通路(即相当于延迟一拍的导线),在使能信号无效时latch锁定,保持输出状态不变;DFF由时钟沿触发,同步控制。

- latch最大的危害在于不能过滤毛刺,这对于下一级电路是极其危险的; 因为同步电路信号的变化都发生在时钟沿,只要毛刺不出现在D触发器时钟的沿口并且不满足数据的建立和保持时间,就不会对系统造成危害(由于毛刺很短,多为几纳秒, 基本上都不可能满足数据的建立和保持时间)。因此可以说,D触发器的D输入端对毛刺信号不敏感。在FPGA设计中,只要能用D触发器的地方,就不用latch。

- 相对DFF来说,latch对输入电平敏感,受布线延迟影响较大。

- 相对DFF来说,latch将静态时序分析变得极为复杂。

二、什么样的代码容易生成锁存器

1、敏感列表是电平触发才可能生成锁存器latch

(1)可能生成锁存器代码示例

- 由于代码中的判断语句、条件语句 没有给出所有可能情况下的输出,导致综合器认为 这些未指定的情况下输出保持不变。这样的代码会综合为锁存器。

|

1

2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 |

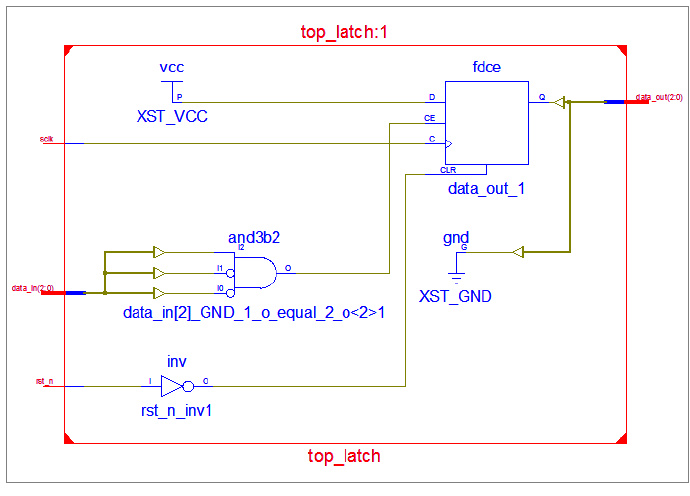

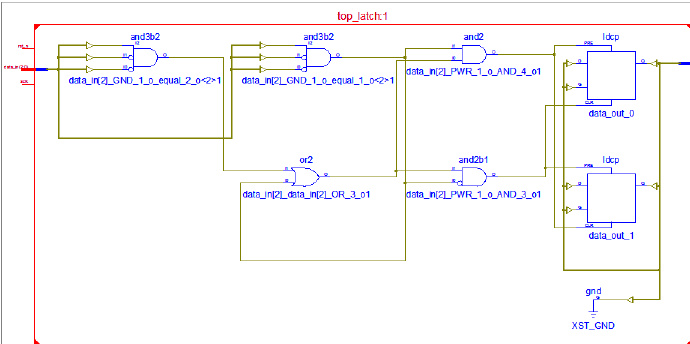

//判断条件未包含敏感列表的全部可能条件:data_in是3bit,共有8种数值,下面仅对2种取值情况进行判断,这种电路会生成锁存器。xilinx综合生成的【锁存器ldcp】如下图2

always @(data_in)

if(data_in == 3'd2) data_out <= 3'd1; else if(data_in == 3'd1) data_out <= 3'd2; //作为判断条件内的变量未包含到敏感列表内:这里的判断条件(data_in1 == 3'd1)没有放到敏感列表里,因此会生成锁存器 always @(data_in) if(data_in == 3'd2) data_out <= 3'd1; else if(data_in1 == 3'd1) data_out <= 3'd2; else data_out <= 3'd0; //case语句未完全遍历所有case条件,并且未包含default语句:敏感列表内的data_in总共有8种数值情况,而case条件仅有2种,且没有default语句,因此会综合生成锁存器latch always @(data_in) case(data_in) 2'd1:data_out <= data_in; 2'd2:data_out <= data_in1; //default:data_out <= 'd0; endcase |

(2)时钟延触发的逻辑都不会生成锁存器

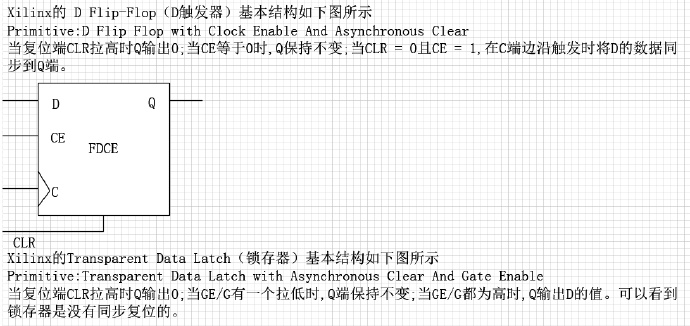

1)xilinx综合生成的【寄存器fdce】如下图。

|

1

2 3 4 5 6 7 |

always @(posedge sclk or negedge rst_n)

if(rst_n == 1'b0) data_out <= 3'd0; else if(data_in == 3'd1) data_out <= 3'd2; //else //时钟沿触发和异步复位,综合器会进行识别,因此若不写else也不会生成锁存器 // data_out <= 3'd0; |

|

1

2 3 4 5 6 |

always @(posedge sclk or negedge rst_n) begin

if(1'b0 == rst_n) //低电平有效,不受异步时钟控制,为D触发器的异步清0端口 sum <= 0; else if(1'b1 == En) //D触发器的时钟使能端口 sum <= a + b; end |

2、如何避免生成锁存器

(1)敏感列表内的变量不全,赋值号右边的变量必须放在敏感列表内;作为判断条件的变量一定要放到敏感列表内,判断条件一定要包含敏感列表变量取值的全部可能情况。

(2)使用完备的if...else语句,即if...else语句必须有else结束赋值。

(3)为每个输入条件设计输出操作,为case 语句设置default操作。特别是状态机设计中,最好有一个default状态转移,且每个状态最好也都有一个default操作。

(4)使用case语句,特别是在状态机设计时,尽量附加综合约束属性,综合为完全条件case语句(full case)。目前大多数综合工具都支持full case的综合约束属性。

(5)仔细检查综合报告,目前大多数综合器对所综合出的latch都会包“warning”。

3、xilinx综合工具综合处的锁存器结构

浙公网安备 33010602011771号

浙公网安备 33010602011771号