Xilinx FPGA配置clocking时钟动态相位输出

开发平台基于Vivado2017.3,器件使用的是Kintex7。

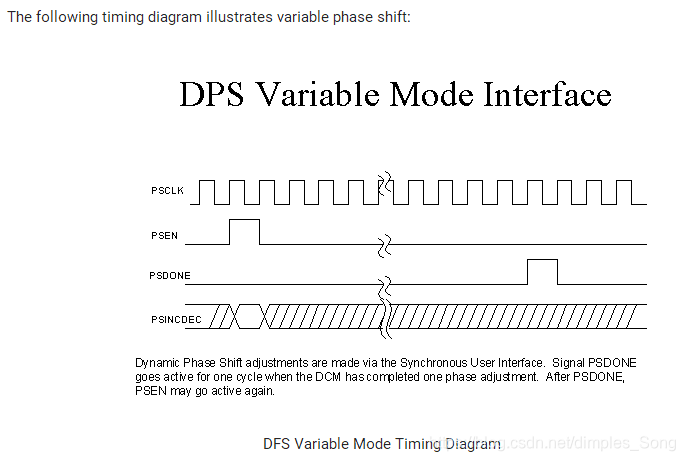

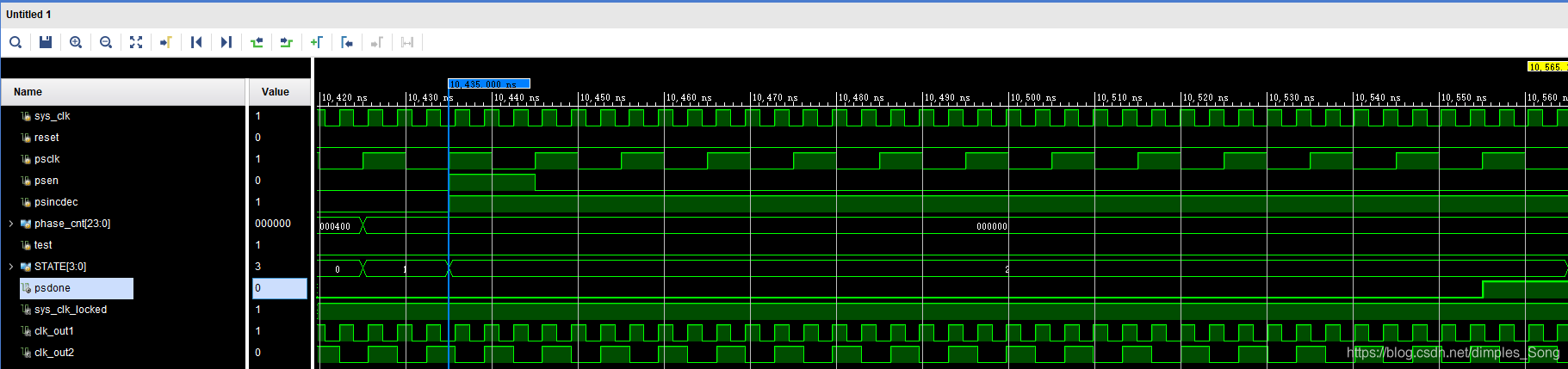

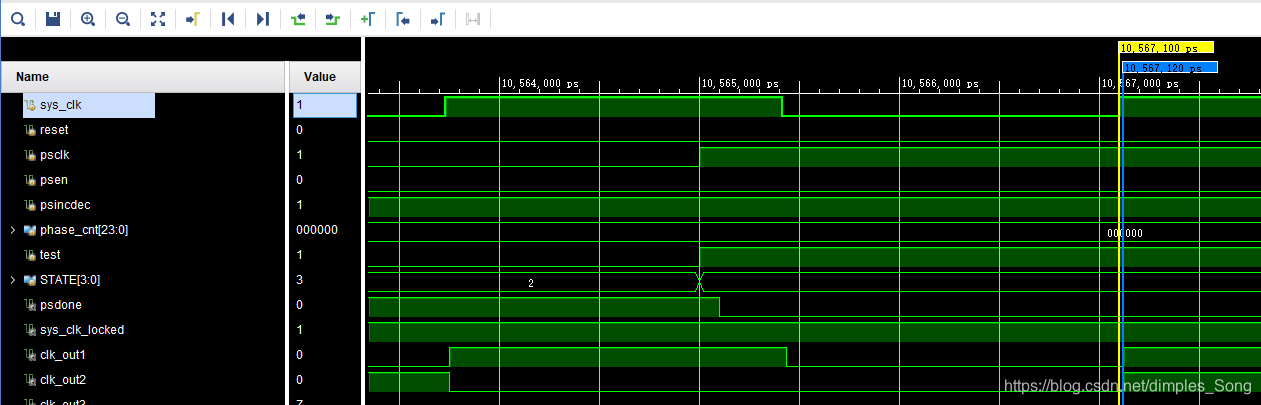

先贴个时序图:

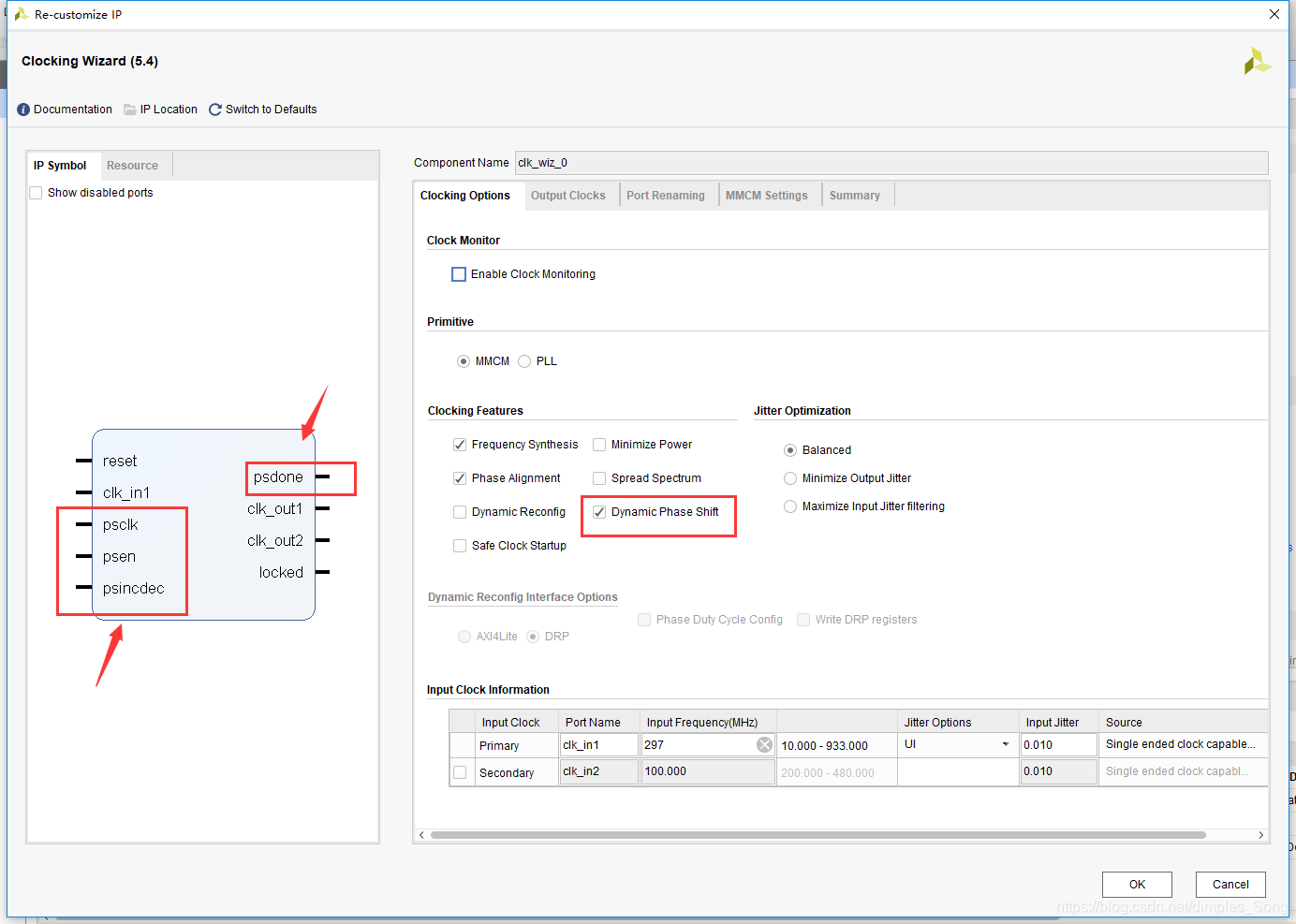

如何动态配置clocking输出时钟相位,首先在ip核设置界面,勾选Dynamic Phase Shift,在左侧接口总览里面可以看到多出来4个信号,psclk:用于相移控制信号的驱动时钟,psen:控制相位偏移的使能信号,psincdec:用于相位正负偏移的信号,1表示正向偏移,0表示负向偏移。最后psdone是相位偏移完成标志信号。权威的接口说明可以自行查阅xilinx 官方手册pg065。

标题

标题

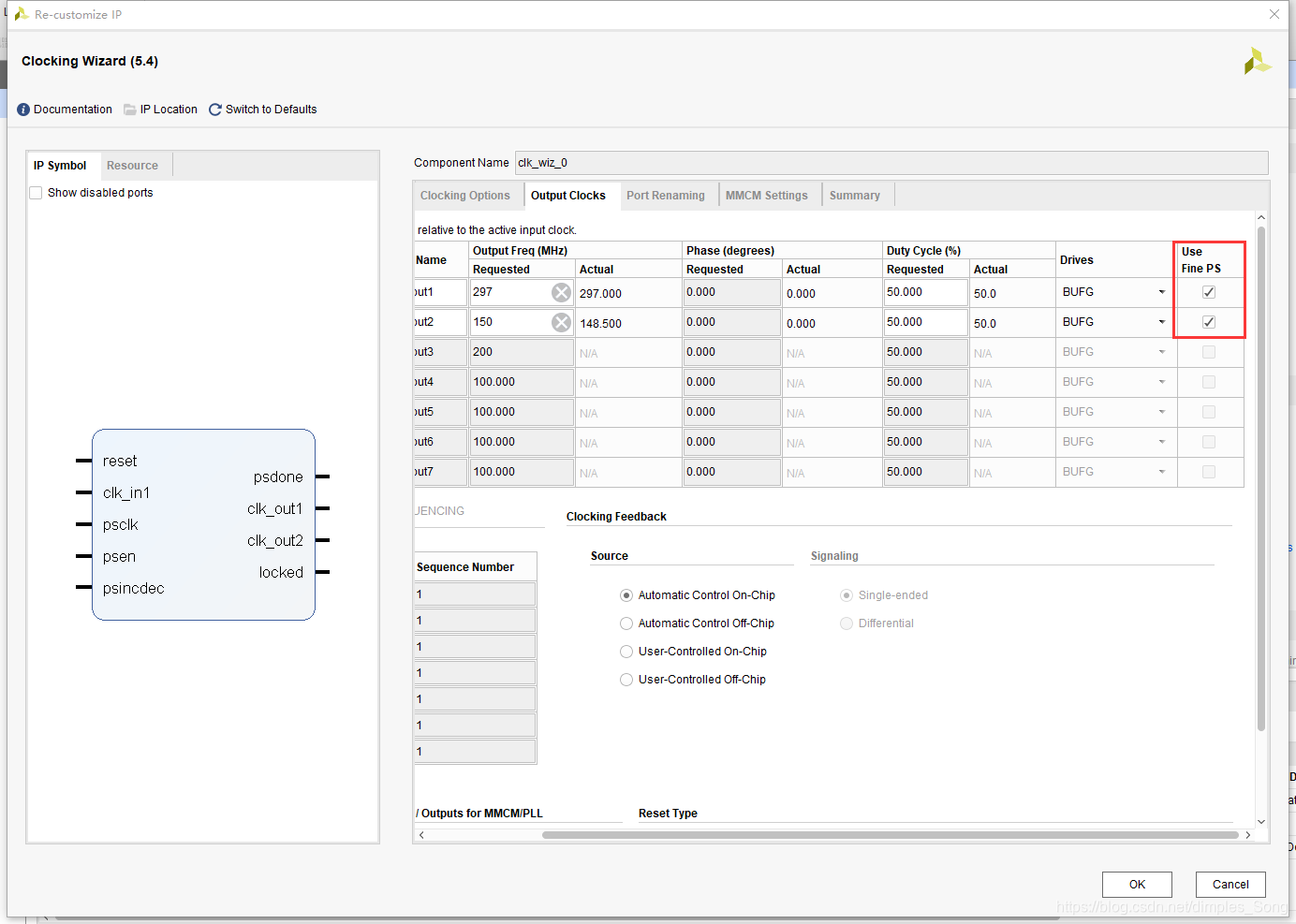

在第二页输出时钟最后勾选Use Fine PS,

标题

标题

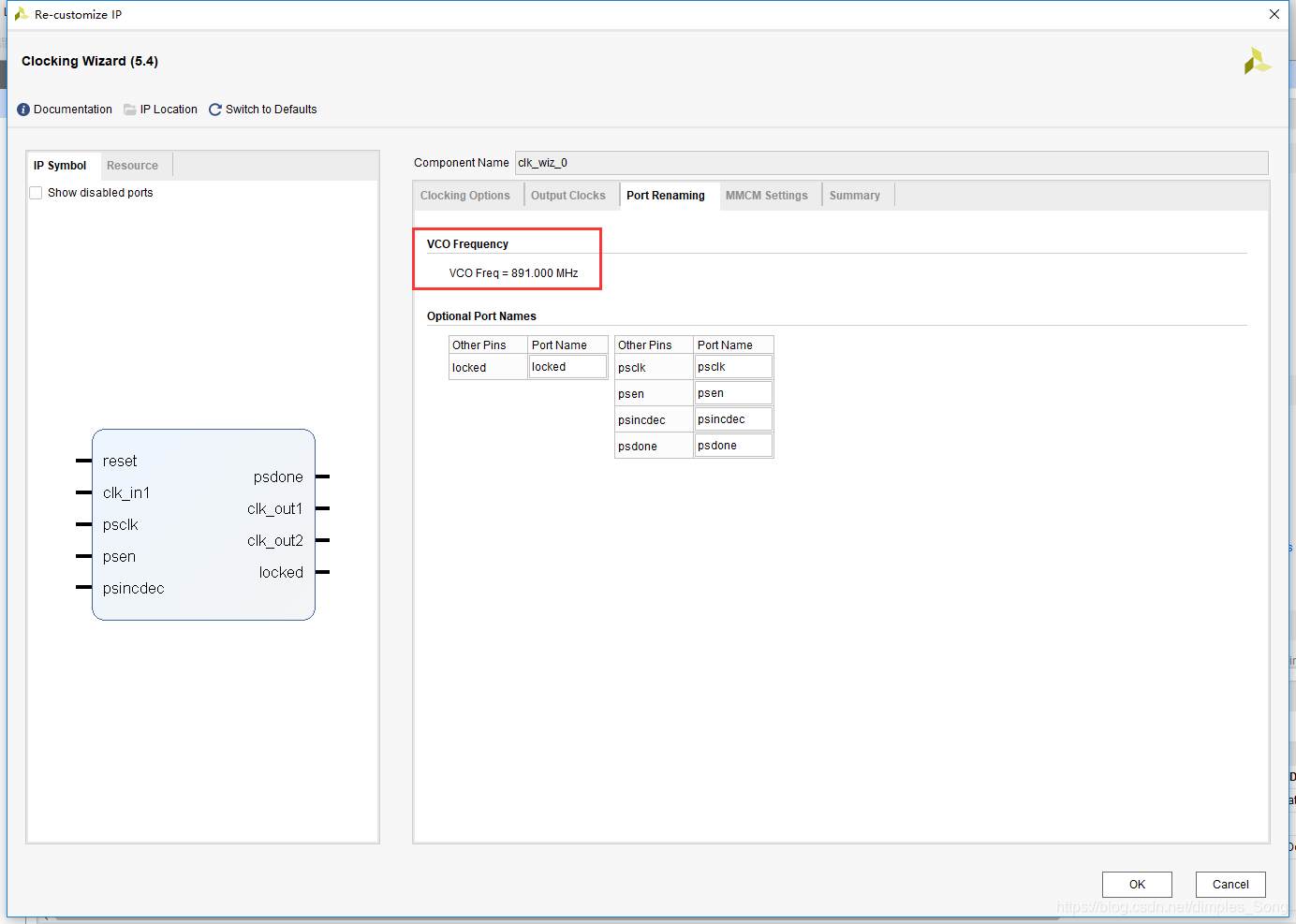

关注一下VCO的频率,一个psen高脉冲,输出相位偏移1/56个VCO周期。

标题

标题

然后例化一下,写个testbench,我看clocking这个ip核的example中,psclk的频率设置的是100Mhz。仿真使用的Vivado自带的仿真器,因为Modelsim仿真时,psdone信号死活不拉高,估计是有BUG。

仿真波形如下,一个psen,输出时钟相位偏移20ps。刚好等于1/891Mhz/56

标题

标题 标题

标题

浙公网安备 33010602011771号

浙公网安备 33010602011771号