在FPGA中实现源同步LVDS接收正确字对齐

在串行数据传输中,数据接收端需要一些特定的信息来恢复出正确的字边界,以确定串行码流中哪些比特属于原始并行数据里的同一时钟节拍里的数据,这一处理过程称为字对齐(Word Aligner)。一些标准的协议会定义特殊的码型(常见的码型如8B/10B编码中的K28.5)用于字对齐处理。另一些带源同步时钟的LVDS接口,通常会利用低频的源同步时钟来携带字对齐信息,用于接收端的正确恢复。FPGA对上述两种方案都可以进行正确处理。那么,如何FPGA中利用低频源同步时钟实现低压差分信号(LVDS)接收字对齐呢?

本文引用地址:http://www.eepw.com.cn/article/191976.htm

在串行数据传输中,数据接收端需要一些特定的信息来恢复出正确的字边界,以确定串行码流中哪些比特属于原始并行数据里的同一时钟节拍里的数据,这一处理过程称为字对齐(Word Aligner)。一些标准的协议会定义特殊的码型(常见的码型如8B/10B编码中的K28.5)用于字对齐处理。另一些带源同步时钟的LVDS接口,通常会利用低频的源同步时钟来携带字对齐信息,用于接收端的正确恢复。FPGA对上述两种方案都可以进行正确处理。对于标准协议,FPGA通常都会有知识产权(IP)模块提供。本文主要讨论在FPGA中利用低频源同步时钟实现低压差分信号(LVDS)接收字对齐的设计方法及步骤。

LVDS已经成为业界高速传输最普遍应用的差分标准。LVDS的优势包括:由于采用差分信号带来的对共模噪声的免疫能力,进而提高了抗噪声能力;功率消耗较小,噪声较小等。由于LVDS有比较好的抗躁声特性,它可以采用低至几百毫伏的信号摆幅,进而可以支持更高的数据速率。

LVDS串行器/解串器(SERDES)可以完成多位宽度的并行信号到LVDS串行信号的转换以及反方向操作,如图1所示。有些器件提供图1中的随路时钟,但有些器件可能并不提供,这时LVDS解串器还必须具有时钟恢复(CDR)功能。市面上有各种规格的LVDS SERDES器件,此外FPGA或其它一些器件也都能集成LVDS SERDES模块。

图1:LVDS串行器/解串器的功能示意图。

为确保正确的数据传送,通过LVDS接收器后必须能恢复字顺序,即输入到LVDS串行器的最高比特能够正确地出现在解串器恢复输出数据的最高比特位置上,至少是需要预先知道出现在哪个比特位置上后再进行调整。图2和图3分别给出了4位宽度下字顺序得到保留和没有得到保留的例子。对于图3的情况,需要采用一种方法找把字顺序调整过来。

图2:字顺序得到保留。

图3:字顺序没有得到保留。

字顺序的调整通常采用寻找训练码来进行。一些标准的协议通常会定义特殊的码型来进行字对齐处理,比如8B/10B编码中K28.5码型的主要功能就是字对齐处理。发送端在有效数据中插入K28.5码型,接收端在收到的数据中寻K28.5码型,找到之后以这个码型为参考得到正确的并行数据输出。此外,诸如SDH协议就利用帧头位置的A1A2字节来进行字对齐处理。

另外一些相对低速的LVDS接口也利用低频的源同步时钟来携带字对齐信息,以便在接收端实现正确的数据恢复。这里的低频源同步时钟也如图1中的随路时钟,LVDS数据和随路时钟之间的倍数关系通常等于LVDS串行化时的倍数因子。比如,德州仪器(TI)的SN65LVDS95 LVDS发送器,不仅可完成21:3的LVDS串行化发送,还将21位的并行数据和时钟串行化成3路LVDS数据输出和1路时钟输出。串行化因子的值等于7,所以输出时钟的频率是LVDS数据速率的七分之一。通过这个随路时钟,配套的解串器SN65LVDS96就能够正确恢复并行数据。

与这类单独的LVDS SERDES器件相比,FPGA集成LVDS模块能提供更高的集成度,并简化硬件设计、节省PCB面积,从而降低应用成本。高端FPGA还在I/O单元里固化了LVDS串行器/解串器,支持非常高的速率,比如Altera公司的Stratix III系列。

Stratix III FPGA系列是Altera公司基于TSMC 65nm工艺的高端FPGA,是业界高密度高性能可编程逻辑器件中,功耗最低的产品系列。Stratix III 器件可以同时提供最多276对LVDS串行化发送模块和276对LVDS解串行化接收模块,每路LVDS最高可以支持1.6Gbps。此外,它还独家提供可编程的输出摆幅和预加重功能,以支持长距离背板传送,如图4所示。

图4:Stratix III 支持可编程的输出摆幅(Vs(p-p))和预加重(Vpp(p-p))。

图5显示了Stratix III的LVDS接收器中固化在I/O单元里的模块。源同步的低频时钟rx_inclk通过PLL倍频移相后得到DIFFI/OCLK,对输入数据rx_in进行采样,采样后的数据可以进行最高因子为10的解串行化。

图5:Stratix III I/O固化的LVDS接收器。

由于FPGA具有非常高的灵活性,比如支持不同LVDS输入数据和输入时钟之间的倍频关系,以及不同的解串行化因子,所以Stratix III LVDS硬核模块的输出字顺序通常是不确定的,每次上电或者复位后字顺序都有可能发生变化,使用时需要根据特殊码型进行字对齐处理。

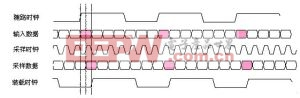

当输入到FPGA的数据和时钟之间的倍数关系等于解串器的解串行化因子时,FPGA与单独的LVDS解串器一样,有确定的字顺序输出,可以在没有训练码型的情况下继续正常应用。图6是解串行化因子为7时的时序图。假设随路时钟的上升沿对应数据的最高比特,在FPGA内部,PLL会从随路时钟产生一个进行过相位调整的7倍频率采样时钟。此时钟对输入数据进行采样后送入解串器,通过控制解串器的装载时钟相位,得到确定的并行数据输出字顺序。装载时钟的相位相对随路时钟相位的固定差异是通过接收PLL的相位控制来实现的,因此必须在输入时钟稳定后再释放PLL的复位控制,或者等输入时钟稳定后再复位PLL一次,否则输出的字顺序在每次上电时都可能不固定。

图6:LVDS接收及解串行化时序图。

在具体应用时,还需通过仿真来确定具体应用下的字输出顺序,然后在逻辑设计里面进行调整,使最终的并行输出符合满足需求。下面以与TI的SN65LVDS95 LVDS发送器对接为例来介绍具体的设计方法和步骤。当把Stratix III的LVDS与别的LVDS器件对接时,也可以此为参考。

图7:LVDS95输出时序。

点击查看大图

在图7,LVDS95输出的时钟和数据是对齐到输出时钟的上升沿上的,数据的最高比特(MSB)出现在时钟上升沿之在后的第三个比特。这里的目的是使Stratix III 的LVDS接收器输出正确的字顺序,也即图7中的D6出现在并行输出数据的最高比特上。

图8:综合设置页面。

假设并行侧的时钟频率是60MHz,这样串行LVDS的速率是480Mbps。为方便描述,这里只针对1路LVDS数据进行设计。

首先根据LVDS95的时序进行Stratix III中的LVDS模块(ALTLVDS)的调用。

图9:频率和锁相环设置页面。

在图8的综合设置页面中,我们没有选上“Implement Serializer/Deserializer circuitry in logic cells,这样就用到了LVDS SERDES硬核。同样也没有选上“Enable Dynamic Phase Alignment mode”选项,这表示不使用DPA功能。

图10:接收器设置页面。

在图9中,根据LVDS95的输出时序,在“What is the phase alignment of 'rx_in' with respect to the rising edge of 'rx_inclock'? ”里选择了0度。在图10的设置中,通常情况下需要选上“Register outputs”选项。但因为后续设计逻辑包含了这些寄存器,所以这里选择该选项。此外,在这里没有使能“rx_channel_data_align”端口来进行字重新对齐。

接下来需要通过仿真找出串行因子等于7的情况下,LVDS硬核的字顺序情况。图11给出了顶层设计例子,图12是在MODELSIM里的仿真结果。

图11:顶层模块的设计。

从图11的仿真波形可以看到,LVDS时钟上升沿之后的第一个数据将在并行侧的rx_out_tmp[6:0]中的rx_out_tmp[2]出现。结合LVDS95的特性,LVDS95输出的MSB(D6)将在rx_out_tmp[0]出现,于是需要将此输出滑动一位,得到正确的字顺序。

图12:仿真波形。

在图13中,首先将数据进行一拍延时,得到rx_out_tmp_dly[6:0],然后将rx_out_tmp_dly[0]放置在输出数据的最高位,rx_out_tmp[6:1]顺序放置在其他位上,得到数据向右滑动一位的效果。如果需要滑动多位,调整上述的放置位置就可以了。对上述调整逻辑,我们可以进一步通过仿真来验证。在此我们输入了一个计数器数据进行确认。图14给出了仿真的部分输出结果,图中,左边两根竖条标出了LVDS输入的“000001”数据,右边的两个竖条标出了rx_out的正确输出。这证明了我们的调整是正确的。

图13:字顺序的调整逻辑。

图14:内容为计数器的仿真输出波形。

本文小结

在利用Stratix III做LVDS接收时,我们可以将解串行化因子设置成等于输入的LVDS数据和时钟之间的倍数关系,这样就可以得到确定的字输出顺序,从而可以不依赖训练码实现正确LVDS接收的字对齐。此方法不仅适合于FPGA与单独的LVDS发送器进行对接,也可用于FPGA与FPGA之间的数据传送,使用时FPGA的LVDS发送端送出低频的源同步时钟即可。

浙公网安备 33010602011771号

浙公网安备 33010602011771号