FPGA之复位

在学习特权同学深入浅出玩转FPGA时,课本里面讲到,同步复位和异步复位都有其弊端。

异步复位的弊端:

异步复位中最严重的问题是,如果异步复位信号在触发器时钟有效沿附近“释放”(复位信号从有效变为无 效)的话,可能会导致触发器输出的亚稳态。

这里不得不说的是触发器有两个特点:

1.异步复位信号释放(对低电平有效的复位来说就是上跳沿)与紧跟其后的第一个时钟有效沿之间,有一个必须间隔的最小时间称为Trecovery(recovery time,恢复时间)。

举例:如果异步复位释放后马上来了一个时钟有效边沿,触发器输出端的值将是不确定的,可能是高电平也可能是低电平,可能处于高低电平之间,也可能处于震荡状态,这就是亚稳态。如下图所示,Q为输出。

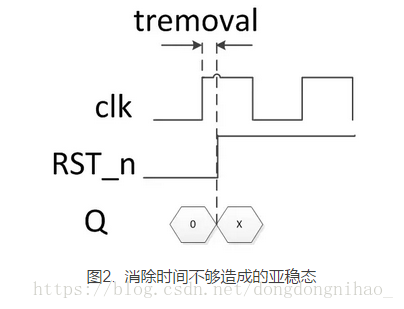

2.时钟有效沿与紧跟其后的异步复位信号释放之间所必须的最小时间称为tremoval(removal time消除时间)。小于这个时间,则触发器的输出端的值将是不确定的,可能是高电平,可能是低电平,可能处于高低电平之间,也可能处于震荡状态,并且在未知的时刻会固定到高电平或低电平。这种状态就称为亚稳态。

举例:如果时钟有效沿到来后,马上来了异步复位信号的上升沿(复位信号释放)触发器处于亚稳态。如下图所示。

同步复位的弊端:

同步复位唯一的缺点就是复位信号必须大于一个时钟周期才能保证被采到,从而能够复位成功,异步复位信号一旦到来,立马复位和边沿没有关系,所以异步复位信号更容易被识别,在保证同步复位信号持续时长的前提下,同步复位是没有问题的。

综上所述,为了避免一般的复位信号(直接接在寄存器的clr端口),复位信号和FPGA内部寄存器之间的“异步”性,导致亚稳态极容易出现。

针对异步复位做如下操作:

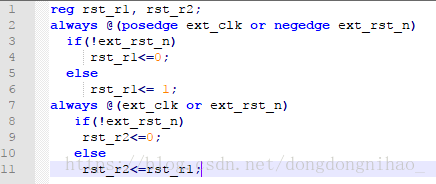

做异步复位,同步释放(本质还是将异步信号打一拍同步化)

上面代码实现的电路功能如下所示:

浙公网安备 33010602011771号

浙公网安备 33010602011771号