时钟资源

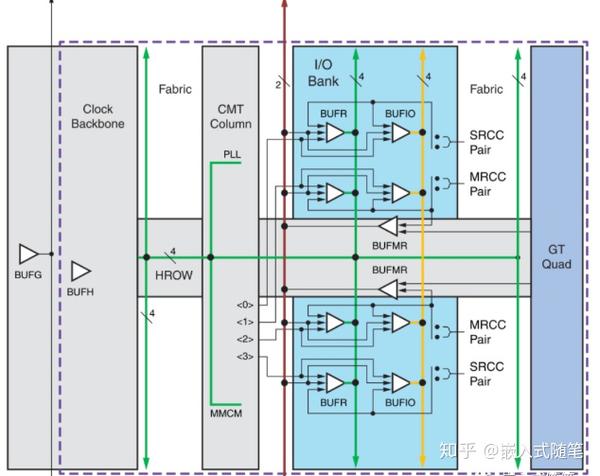

Xilinx的7系列时钟输入有SRCC和MRCC。在手册上有描述,SRCC可用于本时钟区域,MRCC用于本时钟区域和相邻时钟区域。单看这个就有些困惑了,那难不成还连接不到全局时钟了。官方手册中有下面这个图,可以看出SRCC和MRCC都是可以连接到全局时钟的。这个图由于有点具体,不太好理解。

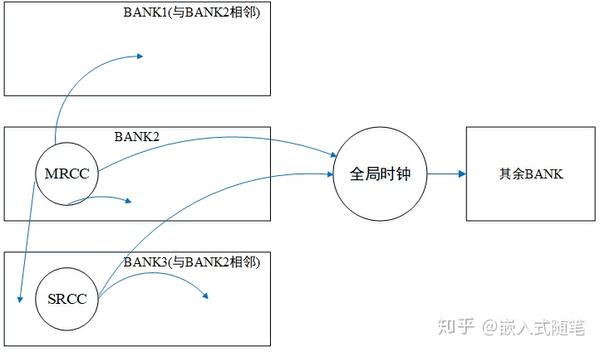

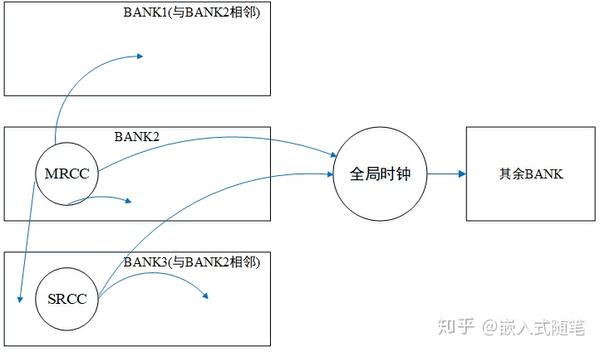

看下面这个图,首先MRCC和SRCC都是可以连接到全局时钟的,但是全局时钟的资源有限。如果程序较大都使用全局时钟的话,那时钟资源就不够用了。SRCC可用于本区域时钟这个比较好了解,MRCC用于相邻的区域该这么理解,MRCC通过不同于全局时钟的渠道可以到达相邻的区域。虽然通过手册可以看到芯片的各个区域分布,但是这个还是最好交给EDA自己优化。如下图BANK1和BANK3可以使用BANK2的MRCC分上来的时钟,没必要先将BANK2的MRCC连接到全局时钟再连接到BANK1和BANK3,这样不但节省了全局时钟资源,而且路径更短。

1)BUFR是区域时钟缓冲器,要进入区域时钟网络,必须例化BUFR。

2)bufg和bufr都要ccio驱动 包括bufg。(clock capable io)。普通io无法驱动bufg和bufr。

3)一个design,如果不例化bufg,或者bufr,直接定义一个input clk,则会在综合阶段自动插入bufg。

4)一个design的时钟,不仅可以由bufg驱动,也能由bufr和bufio驱动。

5)ccio = MRCC + SRCC.

看下面这个图,首先MRCC和SRCC都是可以连接到全局时钟的,但是全局时钟的资源有限。如果程序较大都使用全局时钟的话,那时钟资源就不够用了。SRCC可用于本区域时钟这个比较好了解,MRCC用于相邻的区域该这么理解,MRCC通过不同于全局时钟的渠道可以到达相邻的区域。虽然通过手册可以看到芯片的各个区域分布,但是这个还是最好交给EDA自己优化。如下图BANK1和BANK3可以使用BANK2的MRCC分上来的时钟,没必要先将BANK2的MRCC连接到全局时钟再连接到BANK1和BANK3,这样不但节省了全局时钟资源,而且路径更短。

另,文章引用:

当Xilinx 7Series FPGA中,存在3种主要的时钟网络:BUFG,BUFR,BUFIO以及他们所衍生出的各种变种。那么他们有什么主要特点和区别呢?

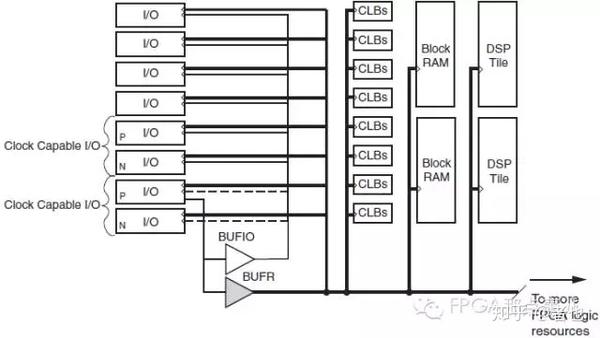

BUFIO是IO时钟网络,顾名思义,它只能驱动IO Block里面的逻辑,不能驱动CLB里面的LUT,REG等逻辑。BUFIO可以被如下节点驱动:

1、SRCCs and MRCCs in the same clockregion

2、MRCCs in an adjacent clock regionusing BUFMRs

3、MMCMs clock outputs 0-3 driving theHPC in the same clock region

BUFR是regional时钟网络,顾名思义,它的驱动范围只能局限在一个clock region的逻辑,但是它可以同时驱动IO和内部逻辑。BUFR可以被如下节点所驱动:

1、所有能驱动BUFIO的节点

2、MMCMs clock outputs 0-3

3、General interconnect

BUFIO和BUFR的主要区别可以用下图概括:

BUFG是全局时钟网络,这个大家最熟悉了,它可以驱动所有的IO和逻辑,并且可以被Transceiver所驱动。

那既然有BUFG了还需要BUFR做什么呢?

BUFR相比BUFG的最大优势是skew和功耗都比较小,在源同步的设计中,这一点也是很关键的。

浙公网安备 33010602011771号

浙公网安备 33010602011771号